входу регистра сдвига, разрядные выходы которого подключены к соответствующим входам первого и второго коммутаторов, выход регистра сдвига подключен к входу блока управления, третнй выход которого подключен к третьему управляющему входу второго сумматор а.

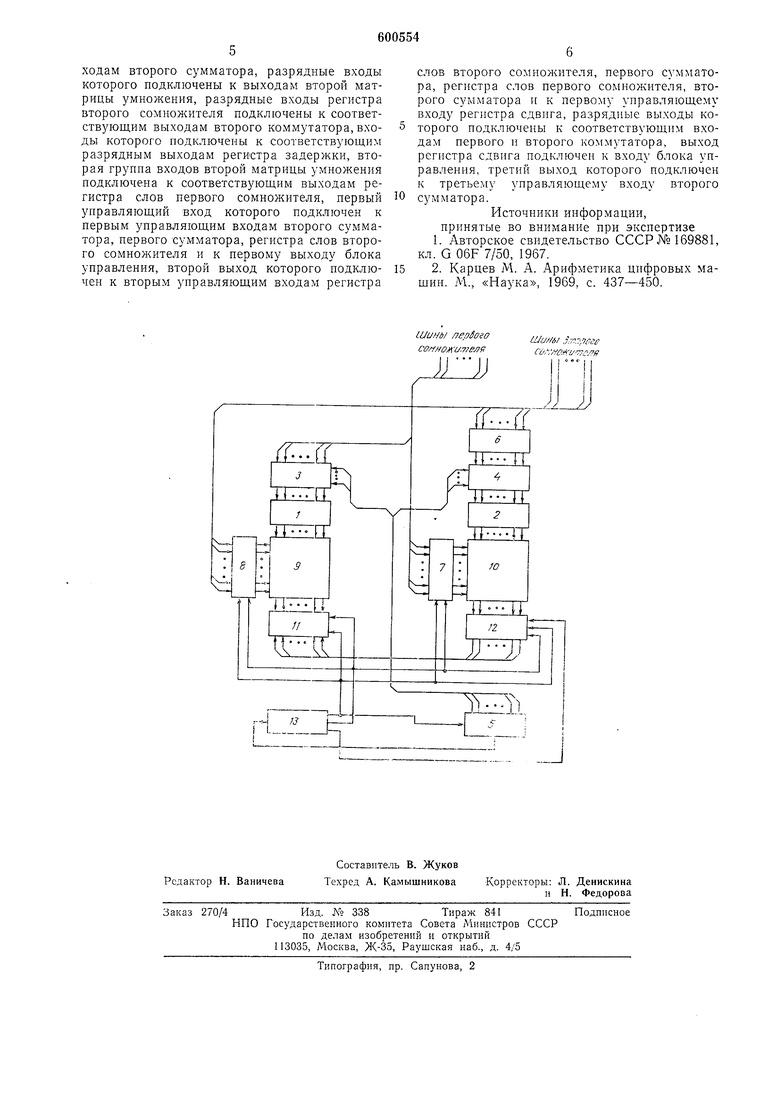

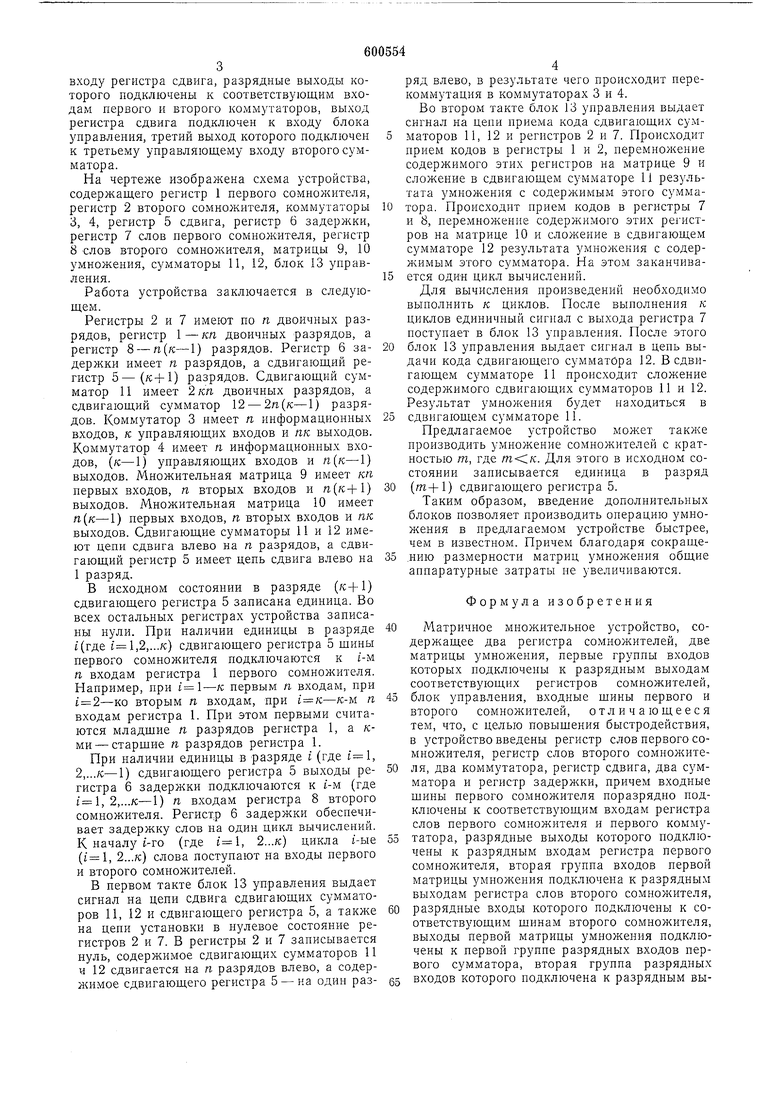

На чертеже изображена схема устройства, содержащего регистр 1 первого сомножителя, регистр 2 второго сомножителя, коммутаторы 3, 4, регистр 5 сдвига, регистр 6 задержки, регистр 7 слов первого сомножителя, регистр 8 слов второго сомножителя, матрицы 9, 10 умножения, сумматоры 11, 12, блок 13 управления.

Работа устройства заключается в следующем.

Регистры 2 и 7 имеют по п двоичных разрядов, регистр 1-кп двоичных разрядов, а регистр 8 - п(к-1) разрядов. Регистр 6 задержки имеет п разрядов, а сдвигающий регистр 5-(к+1) разрядов. Сдвигающий сумматор 11 имеет 2кп двоичных разрядов, а сдвигающий сумматор 12 - 2п(к-1) разрядов. Коммутатор 3 имеет п информационных входов, к управляющих входов и пк выходов. Коммутатор 4 имеет п информационных входов, (к-1) управляющих входов и п(к-1) выходов. Множительная матрица 9 имеет кп первых входов, п вторых входов и п(к+1) выходов. Множительная матрица 10 имеет п(к-1) первых входов, п вторых входов и ПК выходов. Сдвигающие сумматоры 11 и 12 имеют цепи сдвига влево на п разрядов, а сдвигающий регистр 5 имеет цепь сдвига влево на 1 разряд.

В исходном состоянии в разряде (к+1) сдвигающего регистра 5 записана единица. Во всех остальных регистрах устройства записаны нули. При наличии единицы в разряде Цгде 1,2,...к) сдвигающего регистра 5 шины первого сомножителя подключаются к i-м п входам регистра 1 первого сомножителя. Например, при первым п входам, при 1 2-ко вторым п входам, при 1 к-/с-м п входам регистра 1. При этом первыми считаются младщие п разрядов регистра 1, а /сми - старшие п разрядов регистра 1.

При наличии единицы в разряде i (где i-l, 2,...к-1) сдвигающего регистра 5 выходы регистра 6 задержки подключаются к i-м (где i-l, 2,...к-1) п входам регистра 8 второго сомножителя. Регистр 6 задержки обеспечивает задержку слов на один цикл вычислений. К началу t-ro (где , 2...к) цикла /-ые (, 2...к) слова поступают на входы первого и второго сомножителей.

В первом такте блок 13 управления выдает сигнал на цепи сдвига сдвигающих сумматоров 11, 12 и сдвигающего регистра 5, а также на цепи установки в пулевое состояние регистров 2 и 7. В регистры 2 и 7 записывается нуль, содержимое сдвигающих сумматоров 11 и 12 сдвигается на п разрядов влево, а содержимое сдвигающего регистра 5 - на один разряд влево, в результате чего происходит перекоммутация в коммутаторах 3 и 4.

Во втором такте блок 13 управления выдает сигнал на цепи приема кода сдвигающих сумматоров 11, 12 и регистров 2 и 7. Происходит прием кодов в регистры 1 и 2, перемножение содержимого этих регистров на матрице 9 и сложение в сдвигающем сумматоре 11 результата умножения с содержимым этого сумматора. Происходит прием кодов в регистры 7 и 8, перемножение содержимого этих регистров на матрице 10 и сложение в сдвигающем сумматоре 12 результата умножения с содержимым этого сумматора. На этом заканчивается один цикл вычислений.

Для вычисления произведений необходимо выполнить к циклов. После выполнения к циклов единичный сигнал с выхода регистра 7 поступает в блок 13 управления. После этого

блок 13 управления выдает сигнал в цепь выдачи кода сдвигающего сумматора 12. В сдвигающем сумматоре 11 происходит сложение содержимого сдвигающих сумматоров И и 12. Результат умножения будет находиться в

сдвигающем сумматоре 11.

Предлагаемое устройство может также производить умножение сомножителей с кратностью т, где . Для этого в исходном состоянии записывается единица в разряд

(т+) сдвигающего регистра 5.

Таким образом, введение дополнительных блоков позволяет производить операцию умножения в предлагаемом устройстве быстрее, чем в известном. Причем благодаря сокращению размерности матриц умножения общие аппаратурные затраты не увеличиваются.

Формула изобретения

Матричное множительное устройство, содержащее два регистра сомножителей, две матрицы умнолсения, первые группы входов которых подключены к разрядным выходам соответствующих регистров сомножителей,

блок управления, входные шины первого и второго сомножителей, отличающееся тем, что, с целью повышения быстродействия, в устройство введены регистр слов первого сомножителя, регистр слов второго сомножителя, два коммутатора, регистр сдвига, два сумматора и регистр задерлски, причем входные шины первого сомножителя поразрядно подключены к соответствующим входам регистра слов первого сомножителя и первого коммутатора, разрядпые выходы которого подключены к разрядным входам регистра первого сомножителя, вторая группа входов первой матрицы умножения подключена к разрядным выходам регистра слов второго сомножителя,

разрядные входы которого подключены к соответствующим шинам второго сомножителя, выходы первой матрицы умножения подключены к первой группе разрядных входов первого сумматора, вторая группа разрядных

входов которого подключена к разрядным выходам второго сумматора, разрядные входы которого подключены к выходам второй матрицы умножения, разрядные входы регистра второго сомножителя подключены к соответствующим выходам второго коммутатора, входы которого подключены к соответствующим разрядным выходам регистра задержки, вторая группа входов второй матрицы умножения подключена к соответствующим выходам регистра слов первого сомножителя, первый управляющий вход которого подключен к первым управляющим входам второго сумматора, первого сумматора, регистра слов второго сомножителя и к первому выходу блока управления, второй выход которого подключен к вторым управляющим входам регистра

слов второго сомножителя, первого сумматора, регистра слов первого сомножителя, второго сумматора и к первому управляющему входу регистра сдвига, разрядные выходы которого подключены к соответствующим входам первого и второго коммутатора, выход регистра сдвига подключен к входу блока управления, третий выход которого подключен к третьему управляющему входу второго сумматора.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР№ 169881, кл. G 06F 7/50, 1967.

2. Карцев М. А. Арифметика цифровых машин. М., «Наука, 1969, с. 437-450.

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1078433A1 |

| Множительно-делительное устройство | 1974 |

|

SU553614A1 |

Шинд/ coffHo i/,

Авторы

Даты

1978-03-30—Публикация

1975-04-03—Подача