1

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вы- числительных машин последовательного действия.

Известно устройство для умножения последовательного типа I, содержащее регистры множителя, множимого и произведения, одноразрядный сумматор последовательного действия, блок управления, логические элементы И и ИЛИ.

Принцип работы такого устройства не позволяет использовать в нем динамическне регистры с большой степенью интеграции, что ограничивает область применения устройства.

Наиболее близким р«йением по тех ической сущности к изобретению является последовательное множительное устройство с умножением на к разрядов множителя 2, содержащее динамические регистры множимого, частичных произведений, К последовательных сумматоров (, где п - разрядность сомножителей), К элементов И, причем выходы элементов И соответ ственно подключены к первым входам последовательных суиматоров.

Недостатком известного устройства является то, что регистр множителя не выполнен дин㹫ическим, это не , позволяет реализовать в устройстве динамический принцип работы, что в конечном счете сужает область его применения, множительное устройство содержит,большое количество линий задержки на один такт, это усложняет его, увеличивает число связей в устройстве и снижает возможности интегрального исполнення устройства.

Цель изобретения - упрощение устройства.

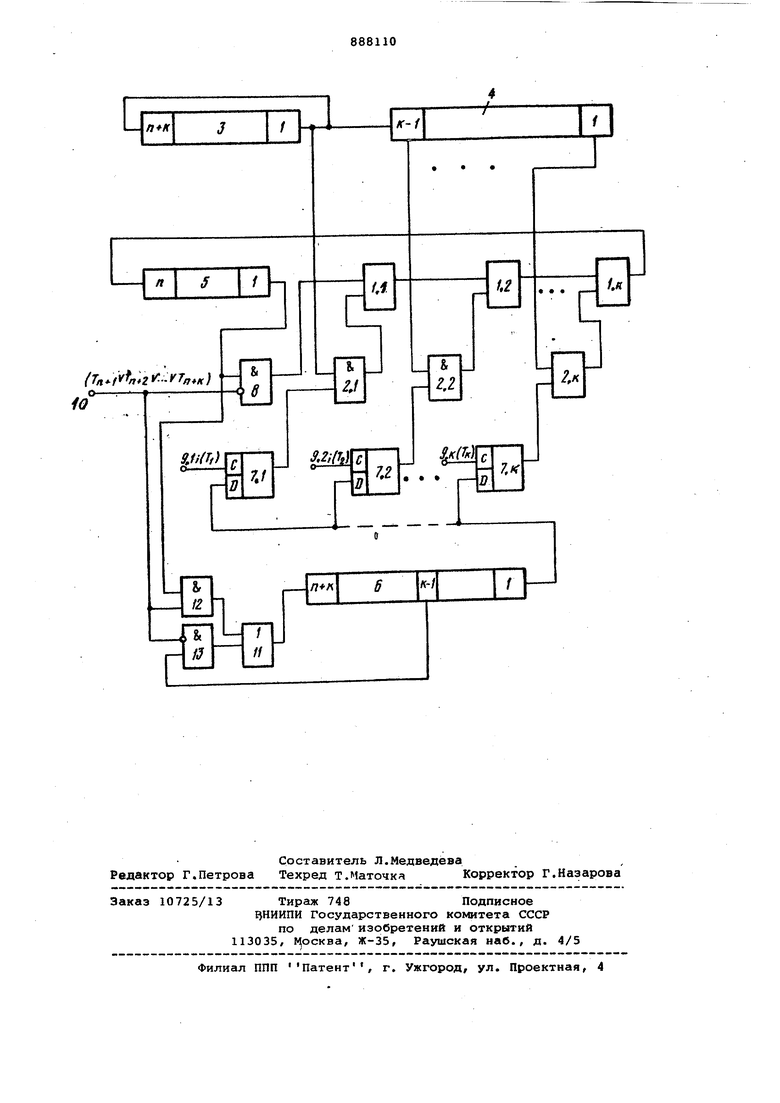

5 Поставленная цель достигается тем, что в него введены динамнческнй регистр множителя, динамический регистр задержки, К D-триггеров, (К-И)-й элемент Н, два элемента запрета, элемент 20 или, причем первый выход динамическог о регистра множителя подключен к D входам О-трйггеров, С входа которых соответственно соедннены с тактовыми шинамн устройства, выходы ;25 D-триггеров подключены к первмя входам соответствующих элементов и, второй вход первого последовательного сумматора соединен с выходом первого элемента запрета, выход каждого 30 последовательного сумматора соединен с вторым входом следующего последовательного сумматора, выход к-го последовательного сумматора соедине с входом динамического регистра час тичных произведений, выход которого подключен к первому входу (k+l)-ro элемента И, а также к прямому входу первого элемента запрета, вход дйна мического регистра множимого соединен с его выходом и подключен к второму входу первого элемента и и к входу динамического регистра задерж ки, выходы которого подключены соот ветственно к вторым входам элементов И, с второго по k-й выход (k+1) го разряда динамического регистра множителя подключен к прямому входу второго.элемента запрета, инверсный вход которого подключен к второму входу (k+l)-ro элемента И, к. инверс ному входу первого элемента запрета а также к управляющей тактовой шине устройства, выходы (k+l)-ro элемента И и второго элемента запрета сое динены с входами элемента ИЛИ, выход которого подключен к входу динамического регистра множителя. На чертеже представлена функцио нальная схема последовательного мно жительного устройства. Устройство содержит kl сумматоров п следовательного действия 1.1, 1 2....jl.k,k элементов И 2.1, 2.2,...,2.k,динамические регистры: (n+k)-разрядный регистр 3 множимого (k-1)-разрядный регистр 4 задержки, п-раэрядный (п-разрядность сомножите лей) регистр 5 частичных произведений (n+k)-разрядный регистр б множителя а также К D-триггеров 7.1, 7.2,..., 7.k, первый элемент 8 запрета, k так товых шин 9.1, 9.2,..., 9.k, управляющую тактовую шину 10, элемент ИЛИ l,(k+)-й элемент и 12,второй элемент 13 запрета. Устройство работает следующим образом. Работа устройства осуществляется по циклам. Длительность каждого цикла равна (n+k) тактам, так как при умножении п-разрядного множимого на k очередных цифр множителя получается часуичное произведение, имеющее разрядность (n+k, а для получения одной цифры частичного произведения нужен один такт. Будем считать, что когда на выходах первых разрядов динамических регистров в режиме хранения находятся первые разряды-записанных в них чисел, на первой тактирующей шине 9.1 появляется единичныйсигнал Т1, соответствующий началу цикла. Сигналу Т2 на шине 9.2 соответст15ует такое расположение информации в регистрах при котором на выходах первых разрядов находятся вторые разряды чисел и т.д. в исходном состоянии (такт Т1 первого цикла) в п первых разрядах регистра 3 находится множимое, а в п первых разрядах регистра б находится множитель. В остальных k разрядах регистров 3 и б (с/п+1)-го по (n+k)-и записаны нули. В регистрах 5 и 4 в исходном состоянии записаны нулевые коды. Рассмотрим цикл работы устройства, В,тактах Т1,,Tk каждого цикла в триггеры 7.1,..., 7.k записывается код очередных k разрядов множителя, на которые в данном цикле будет производиться умножение. Последовательное поступление в каждом цикле на триггеры 7.1,..., 7.k очередных k разрядов множителя обеспечивается соответствующей коммутацией цепей циркуляции регистра б. Цепь циркуляции регистра 6 замыкается с выхода его (k+l)-ro разряда, что обеспечивает в каждом цикле сдвиг на k разрядов в рторону младших разрядов (вправо). Цикл циркуляции регистра 3 совпадает с циклом схемы, равным (n+k) тактов. Цепь циркуляции регистра 5 замыкается через последовательно соединенные сумматоры 1.1,..., l.k. Цикл его циркуляции равен п тактов (на k тактов меньше цикла схемы), что обеспечивает в каждом цикле сдвиг информации на k разрядов вправо. Таким образом, на сумматоре 1.1 в каждом цикле осуществляется сложение сформированной в предыдущих циклах и сдвинутой на k разрядов вправо суммы частичных произведений и кода множимого, умноженного на младший из k очередных разрядов множителя. На сумматоре 1.2 осуществляется сложение сформированного на выходе сумматора 1.1 числа и сдвинутого на один разряд влево множимого, умноженного на вторую цифру группы разрядов множителя. Аналогично осуществляется сложение на остальных сумматорах. Соответствующие сдвиги множимого влево обеспечиваются задержкой через регистр 4 подачи кода множимого на входы сумматоров 1.2,...,l.k. Управление подачей кода множимого на входы сумматоров 1.1,... l.k через элементы И 2.1 г...,2.k (умножение на цифру множителя) осуществляется триггерами 7.1,...,7.k. На выходе сумматора l.k таким образом за n+k тактов формируется очередная сумма частичных произведений, причем в первых k тактах определяется k очередных (начиная с младших) ЦИФР окончательного результата (произведения), в последних п тактах формируется такущая п-разрядная сумма частичных произведений. Заметим, что к концу такта предыдущаяп-разрядная сумма частичных.

произведений полностью выдвинется иг регистра 5, а в его k младших разрядах будут находиться k очередных цифр произведения. Поэтому,начиная с такта Т(п+ 1) по сигналу на шине Ю, выдала кода из регистра 5 на сумматор 1.1 через элемент 8 блокируется, разрывается цепь циркуляции регистра б с выхода {k+l)-ro разряда, и открывается через элементы 11 и 12 цепь приема очередных k разрядов произведения в старшие разряды регистра 6.

После последнего (n+k)-го такта Кс1ждого цикла состояние узлов и регистров устройства следующее. Регистр 3 в исходном состоянии. Кули из (n+k) старших разрядов регистра множимого в последних jc тактах пе- реписались в регистр 4, так что он тоже в исходном состоянии. В регистре 5 находится очередное частичное произведение, поступившее туда за последние п тактов с сумматора l.k. В регистре б в его младших разрядах находится k очередных цифр множителя, а в старших разрядах очередные К цифр результирующего произведения. На К В-триггерах; записаны k предыдущих цифр множителя, однако они не влияют на формирование произведения в следующем цикле, так как с первого по k-й такты происходит перезапись очередных цифр множителя в соответствующие триггера.

После последнего такта последнего цикла в регистре 5 хранятся п старших цифр произведения, а в старших разрядах регистра 6 его п младши с цифр. . .

Таким образом использование в последовательном множительном устройстве в цепи формирования произведения динамических регистров позволяет значительно упростить устройство, а также расширяет область его применения за счет использования в мгипогабаритных вычислительных устройстгвах на интегральных динамических рн гистрах.

Формула изобретения

Последовательное множительное yetройство, содержащее динамические регистры множимого, частичных произведений, К последовательных сумматоров, (, где п-разрядиость сомножителей), К элементов И, причем выходы элементов И соответственно подключены к первым входам последос вательных сумматоров, отличающееся тем, что, с целью упрощения устройства, в него введены динамический регистр множителя, динамический регистр задержки, К D-триггеров, (k+)-й элемент И, два элемента запрета, элемент ИЛИ, причем первый выход динамического регистра множителя подключен к D-входам Dтриггеров, С входы которых соответственно соединены с тактовыми шинами устройства, выходы D-триггеров подключены к первым входам соответствующих элементов И, второй вход первого последовательного сумматора соединен с выходом первого элемента

0 запрета, выход каждого последователь ного сумматора соединен с вторым входом следующего последовательного сумматора, выход k-ro последовательного сумматора соединен с входом динамического регистра частичных произведений, выход которого подключен к первому входу (k+1)-го элемента И, а также к прямому входу первого элемента . запрета, вход динамического

Q регистра множимого соединен с его выходом и подключен к второму входу, первого элемента И и к входу динамического регистра задержки,выходы которого подключены соответственно к

с вторым входам элементов И,с второго по k-й выход (k+1)-го разряда динами ческого регистра множителя подключен к прямому входу второго элемента запрета, инверсный вход которого подключен к второму входу (k+1)-го элёмен0 та и, к инверсному входу первого элемента запрета,а также ук управляющей тактовой шине устройства, выходы (k+1)-го элемента И и второго элемента запрета соединены с входами элемента ИЛИ, выход которого подключен к входу динамического регистра множителя.

Источники информации, принятые во внимание при экспертизе

0 Авторское свидетельство СССР W 608157, кл. G 06 F 7/39, 1974.

2. Карцев М.А. Арифметика цифровых машин.-М., Наука, 1969, с. 458-464 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное множительное устройство | 1981 |

|

SU987620A1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для умножения чисел | 1979 |

|

SU817702A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

Авторы

Даты

1981-12-07—Публикация

1980-03-31—Подача