Устройство может работать с числами с фиксированной запятой или с числом, представленным в нормальной форме. Во втором случае в разрядной сетке устройства отводится часть разрядов для фиксации порядков чисел. В данном описании рассмотрен конкретный пример работы реализации для двоич-ных чисел с фиксированной запятой.

Блок управления 6 анализирует состояние знаковых разрядов сумматоров 4, 5 и регистра 1 и в соответствии с ними вырабатывает и заносит в знаковый разряд сумматора 5 знак результата множительно-делительиой операции.

При равенстве знаков операндов а и 6 знак результата соответствует знаку операнда с, в .противном случае обратному знаку этого операнда. В последующих вычислениях знаковые разряды не участвуют.

Далее, производится нормализация чисел а в регистре 1 и & в регистре 2 и сумматоре 4. Направление и величина необходимого сдвига числа с определяется направлением и величиной сдвигов при нормализации чисел а и Ь. Если левому направлению сдвига (в сторону старших разрядов) приписать знак «плюс, а правому - «минус, то направление и величина сдвига числа с будет определяться знаком и величиной простой зависимости

где р и /-величина сдвига числа & и а соответственно.

Устройство реализует эту зависимость следующим образом.

Если первым нормализовалось число о, для случая и , то блок управления 6 подсчитывает последующие такты сдвига числа b до его нормализации и затем производит сдвиг числа с в регистре 3 и сумматоре 5 на подсчитанное количество сдвигов вправо - в сторону младщих разрядов. Если же первым нормализовалось число Ь, то блок управления 6 подсчитывает последующие такты сдвига числа а в регистре 1 до его нормализации и затем ироизводит сдвиг числа с в регистре 3 и сумматоре 5 на подсчитанное количество тактов сдвига влево - в сторону старщих разрядов. Если для нормализации числа а требуются сдвиги влево, т. е. а 0,5, а для числа Ь вправо, т. е. , то подсчитывается суммарное количество сдвигов для чисел а и Ь, после чего па это количество сдвигается число с вправо. Если же направление -сдвигов для чисел а и & противоположное предыдущему условию, то число с сдвигается на суммарное количество сдвигов влево.

Для случая, когда ,5, ,5 и , подсчитывается разность количества сдвигов при нормализации чисел а и Ь, а число с сдвигается па эту разность влево. Для случая ,5, ,5 и , число с сдвигается на разность количеств сдвигов при нормализации чисел а и Ь Е сторону младщих разрядов - вправо.

Затем начинается выполнение второго этапа, состоящего из последовательности щагов - выполнение множительно-делительной операции представляет собой итерационный процесс, реализующий зависимости (1) - (3) и состоит из ряда однотипных щагов. Первый шаг. В регистрах 2 и 3 производится сдвиг соответствующих чисел &о и Со, полученных после операции нормализации, на один разряд вправо для получения величии и Со-2 соответственно. С выходов сумматора 4 и регистра 1 соответствующие числа bo и Со подаются на соответствующие входы блока управления 6, где происходит сравнение их величин. Причем, при подаче содержимого сумматора 4 и регистра 1 на блок управления 6 в данный момент -

первое сравнение - ив последующих операциях сравнения значение содержимого сохраняется о сумматоре 7 и регистре . По результату операции сравнения блок управления 6 вырабатывает сигнал g,-, по которому содерл имое регистров 2 и 3 подается с сохранением в регистрах 2, 3 в сумматоры 4 и 5 соответственно для подсуммирования с содержимым сумматоров или для вычитания из содержимого сумматоров. Если же сравниваемые величины равны, то вырабатывается команда «Останов и вычислительный процесс прекращается. В этом случае в сумматоре 5 зафиксирован результат вычислений. Одновременно с суммированием (вычитанием) в сумматорах 4 и 5 производится сдвиг содержимого регистров 2, 3 на один разряд вираво для получения очередных приращений и использземых на втором щаге.

Второй щ а г. Как и на предыдущем щаге блок управления 6 сравнивает содержимое сумматора 4, с содержимым регистра 1 и вырабатывает сигнал, по которому содержимое регистров 2 и 3 подается, с сохранением этих содержимых в регистрах 2, 3, в сумматоры 4, 5 соответственно для подсуммирования или вычитания. Если же сравниваемые величины равны, то процесс прекращается (сигнал «Останов), а в сумматоре 5 фиксируется результат вычислений.

Если блок зправления 6 не выработал сигнала «Останов, то продолжится выполнение следующих шагов вычисления, причем, все они аналогичны второму щагу и начинаются с анализа содержимого сумматоров 3 и 5.

Количество указанных шагов при выполнении вычислений составляет величииу g, причем , где п-количество разряДов разрядной сетки устройства, предназначенных для представления дробной части чисел. Если на каком-либо щаге вырабатывается блоком управления 6 сигнал «Останов, то это влечет за собой сокращение времени

вычислений, так как этот сигнал в зависимости от значения чисел а н b может возникнуть на любом шаге, начиная с первого. По окончании вычислительного процесса результат зафиксирован в сумматоре 5.

Если на предлагаемом устройстве требуется выполнить операцию деления двух чисел

вида или , тогда при занесении bО

В устройство делимого а или с и делителя 6, в качестве недостающего сомножителя с или а соответственно вводится единица. Если требуется выполнить самостоятельную операцию умножения (), то в качестве делителя при занесении сомножителей в устройство вводится единица ().

Длина разрядной сетки устройства выбирается в зависимости от диапазона чисел, с которым предназначена работа устройства и от требуемой точности вычислений.

Таким образом, введение дополнительных сумматора и регистра позволяет повысить быстродействие вычислений и расширить функциональные возможности устройства, выполняя одновременно умножение и деление.

Формула изобретения

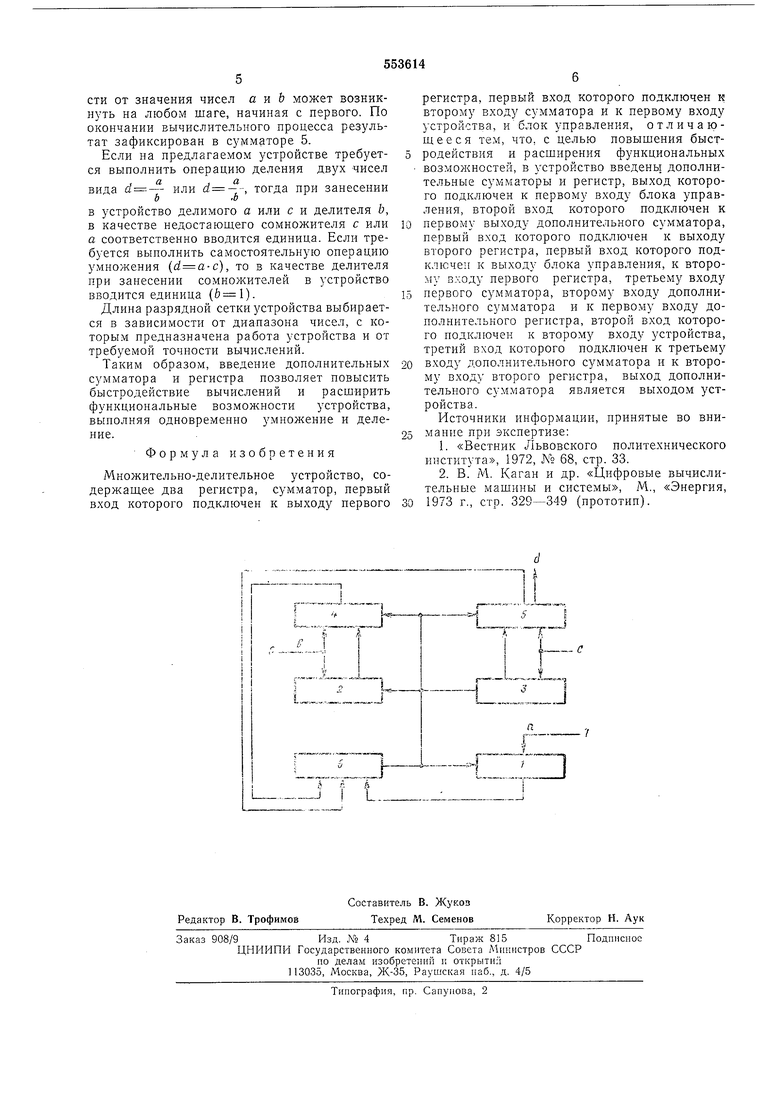

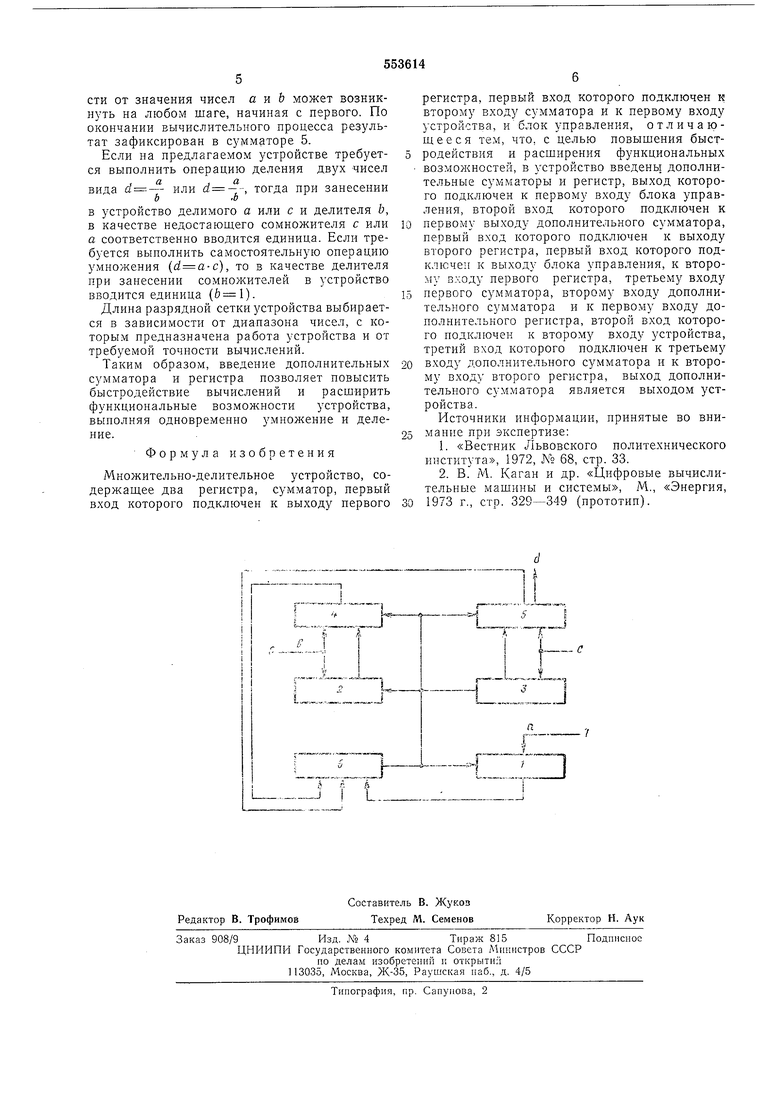

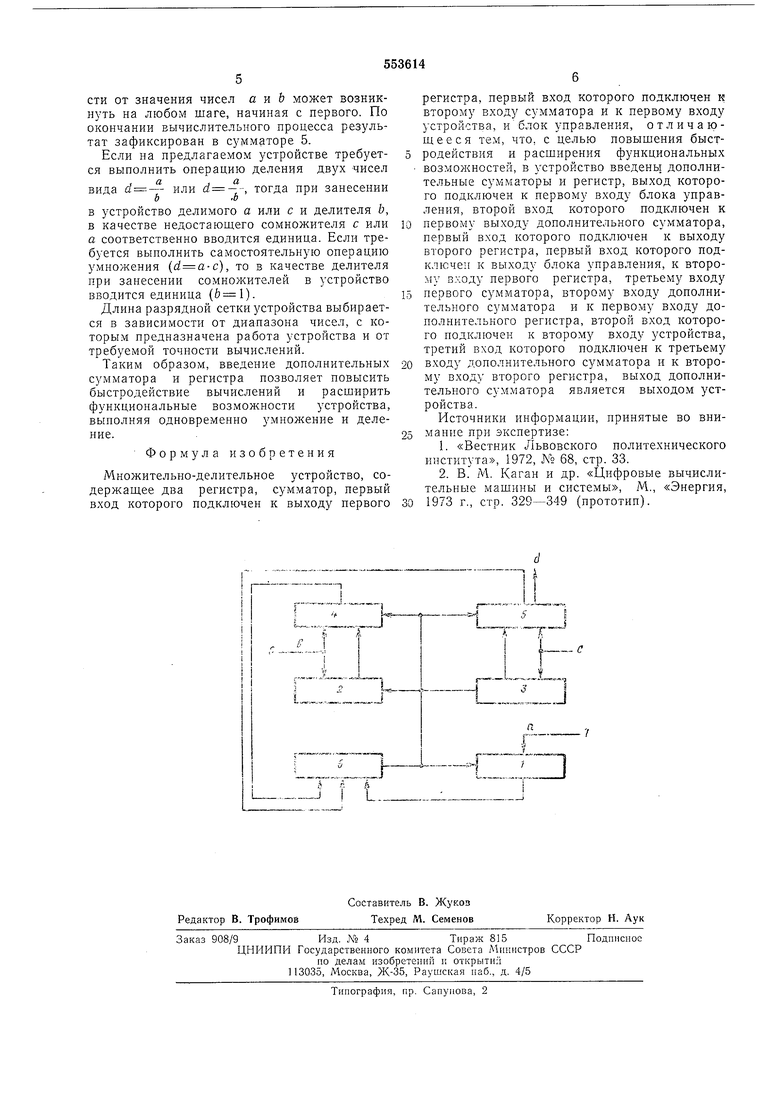

Множительно-делительное устройство, содержащее два регистра, сумматор, первый вход которого подключен к выходу первого

регистра, первый вход которого подключен к второму входу сумматора и к первому входу устройства, и блок управления, отличающееся тем, что, с целью повыщения быстродействия и расщирения функциональных возможностей, в устройство введень; дополнительные сумматоры и регистр, выход которого подключен к первому входу блока управления, второй вход которого подключен к

первому выходу дополнительного сумматора, первый вход которого подключен к выходу второго регистра, первый вход которого подключен к выходу блока управления, к второму входу первого регистра, третьему входу

первого сумматора, второму входу дополнительного сумматора и к первому входу дополнительного регистра, второй вход которого подключен к второму входу устройства, третий вход которого подключен к третьему

входу дополнительного сумматора и к второму входу второго регистра, выход дополнительного сумматора является выходом устройства.

Источники информации, принятые во внимание при экспертизе:

1.«Вестник Львовского политехнического института, 1972, ЛЬ 68, стр. 33.

2.В. М. Каган и др. «Цифровые вычислительные машины и системы, М., «Энергия,

1973 г., стр. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 2016 |

|

RU2633095C1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1062693A1 |

| Цифровое устройство для ограничения чисел | 1978 |

|

SU767758A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

i

н

.J

It.-

-.н

с 1

Авторы

Даты

1977-04-05—Публикация

1974-08-27—Подача