Изобретение относится к вычислиттельной технике и может исполь9рвать ся при построении центральных процессоров цифровых вычислительных ма шин. .

Целью изобретения является расширение функциональных возможностей прцессора за счет нормализации чисел с фиксированной запятой

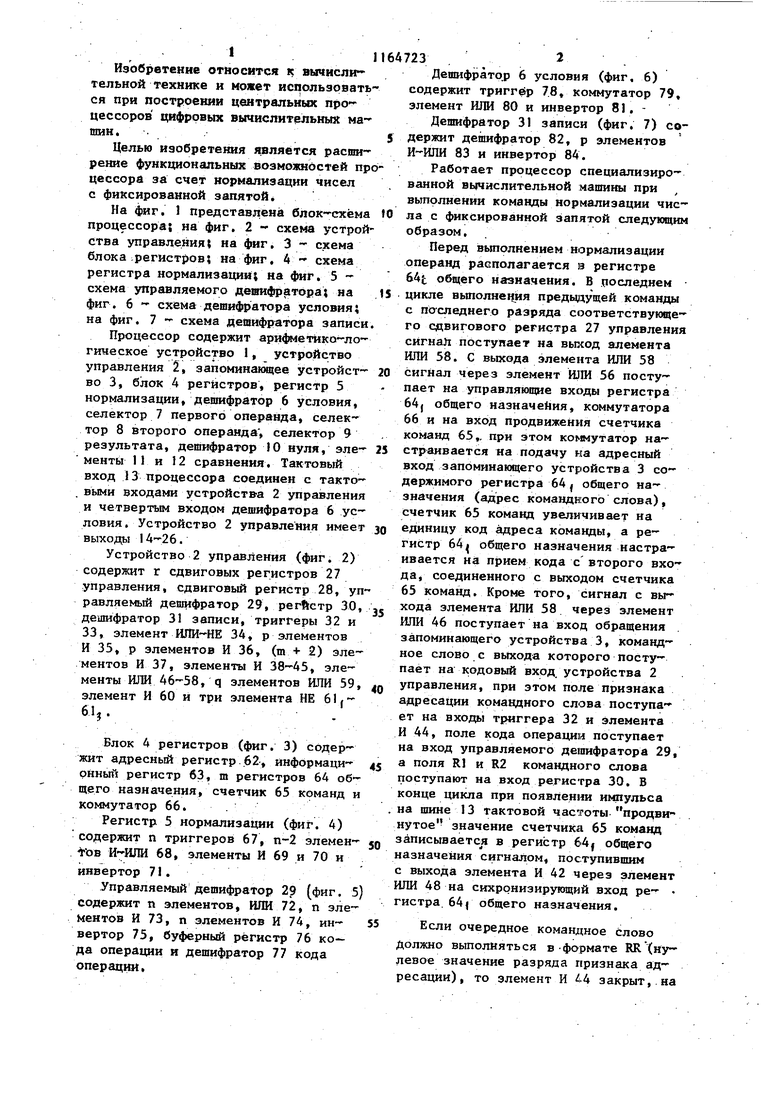

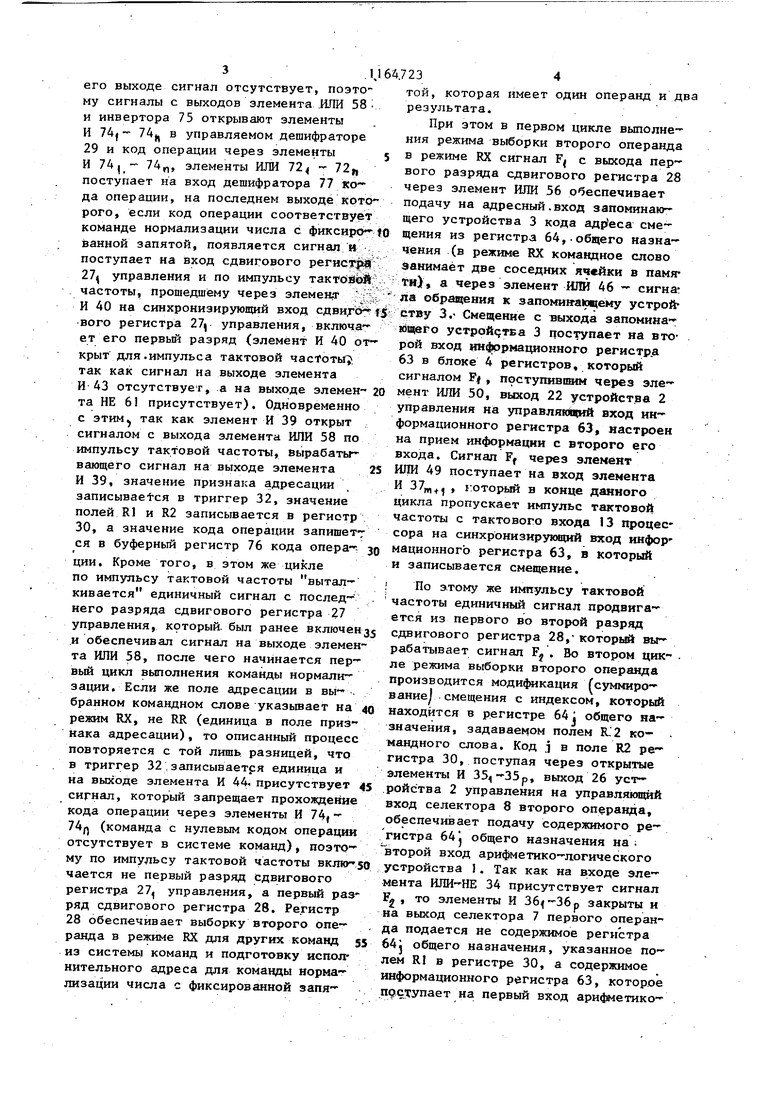

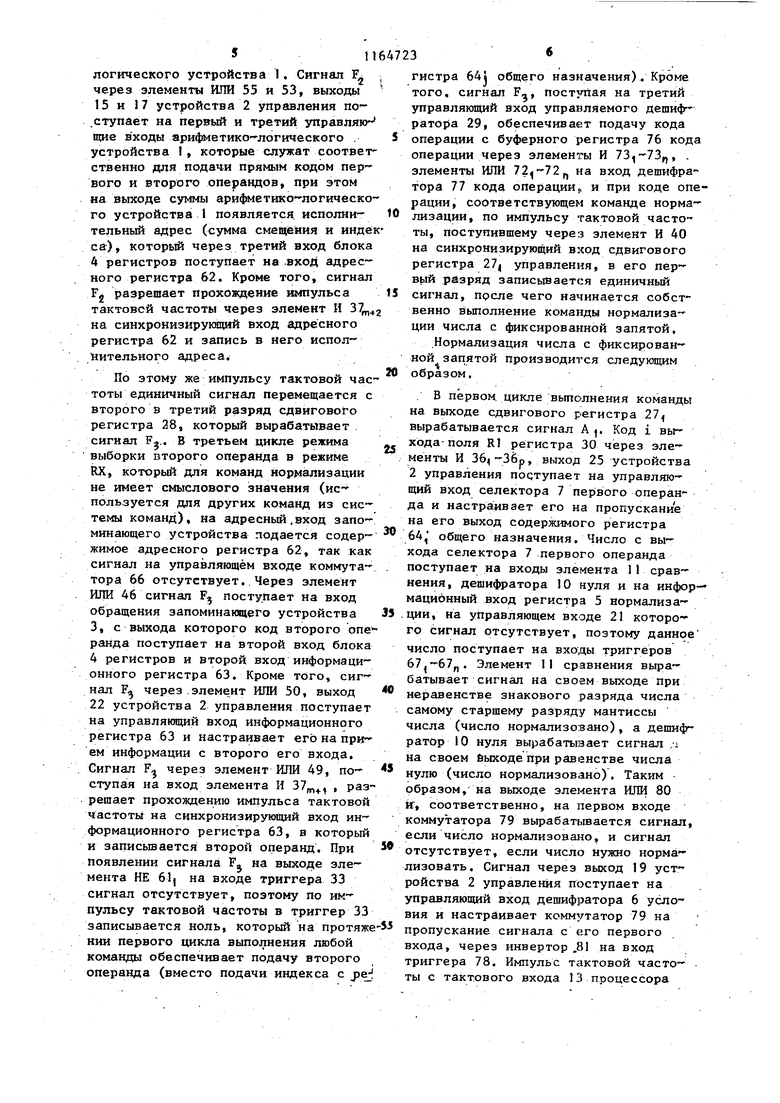

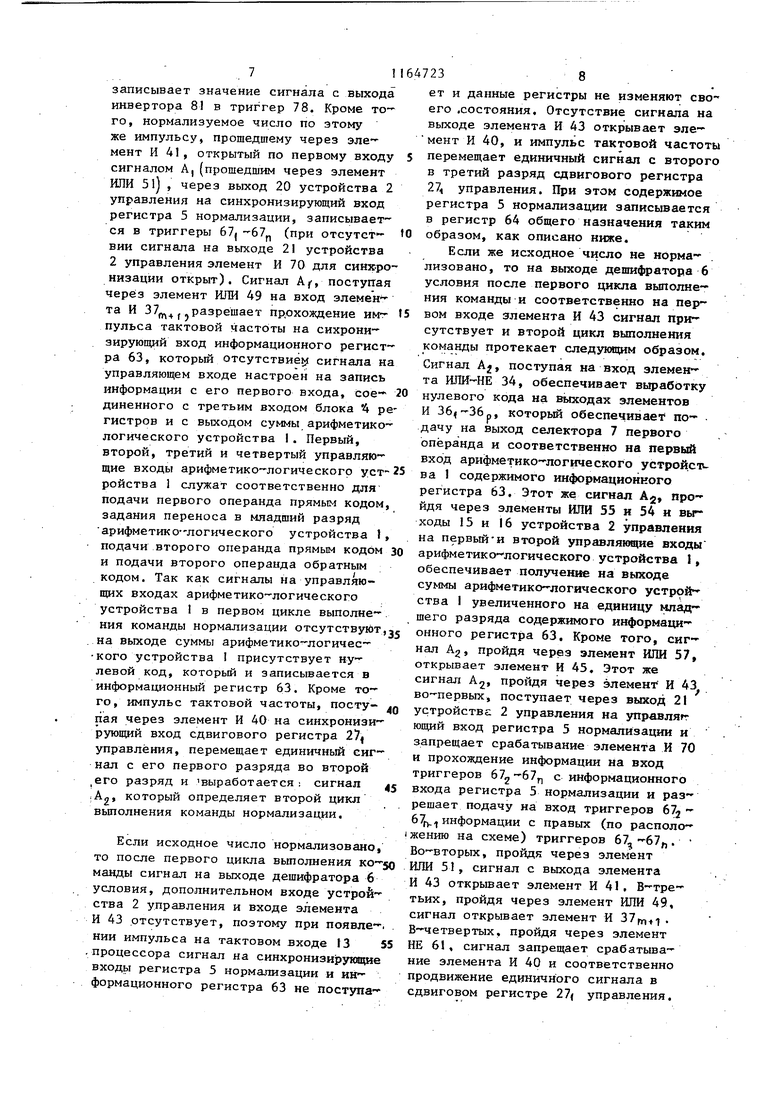

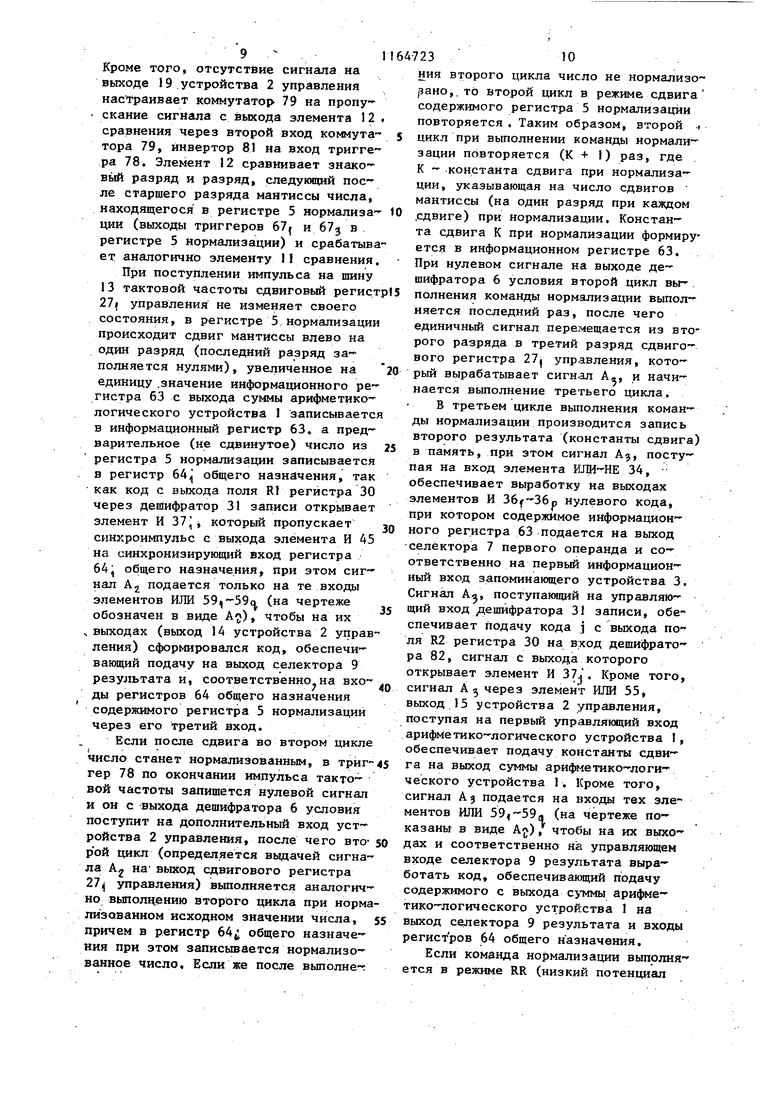

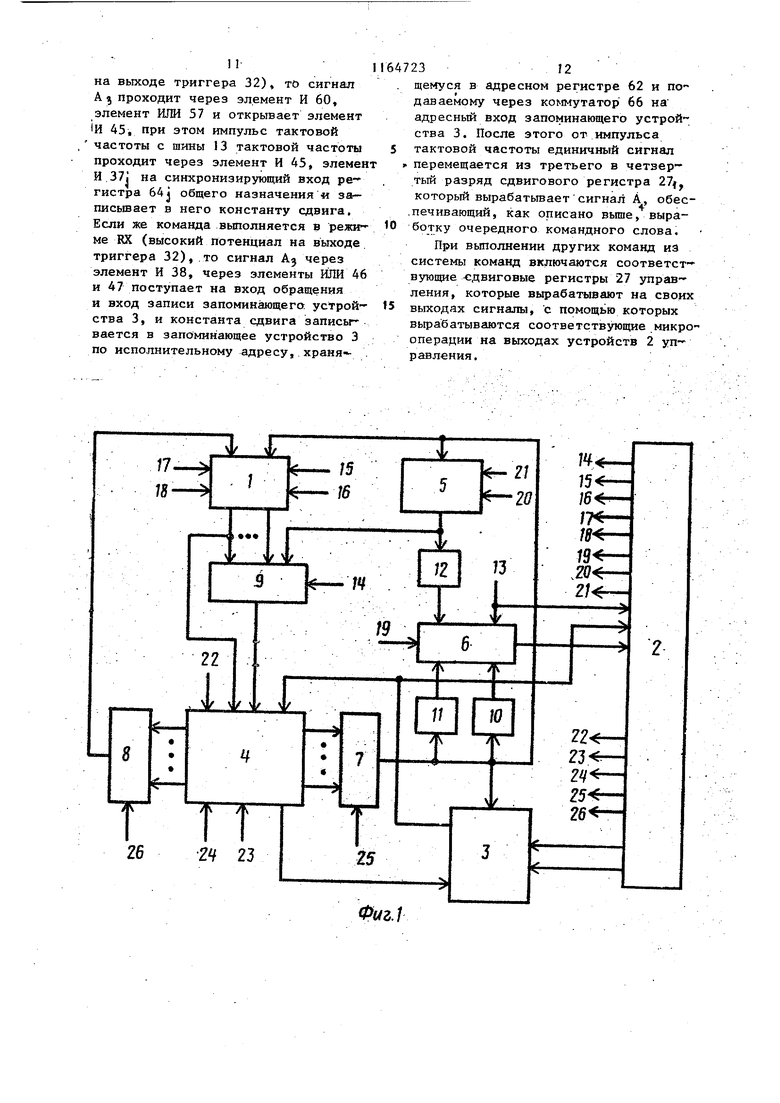

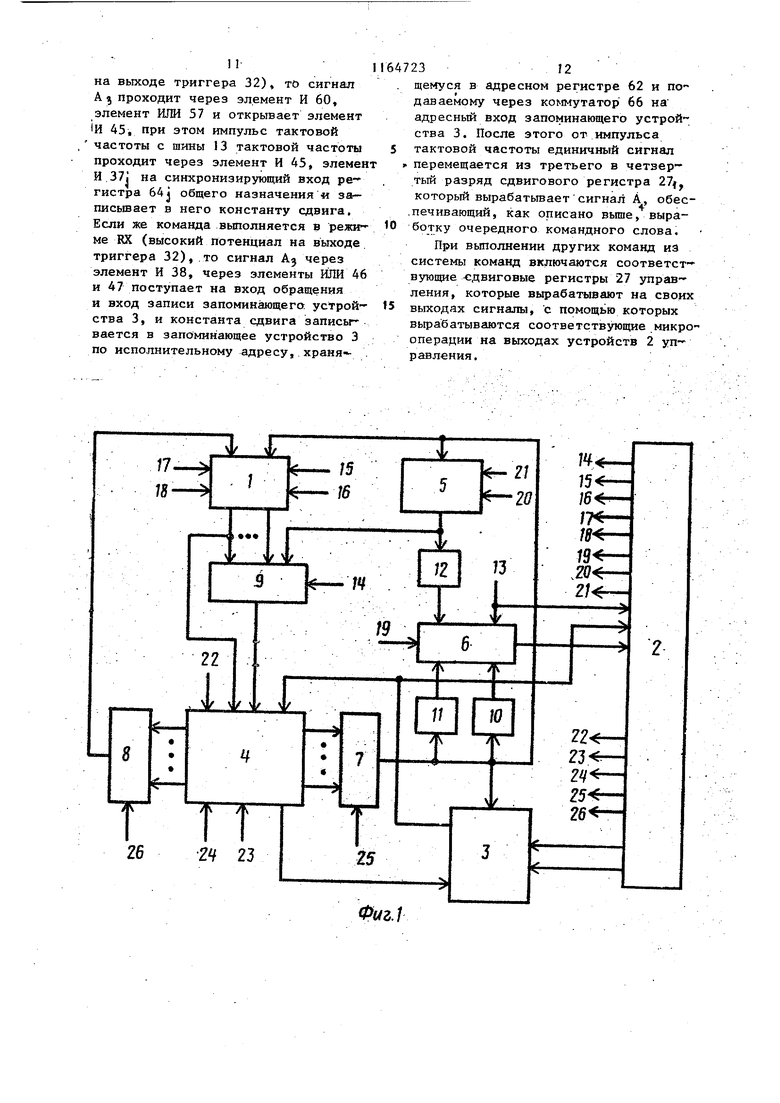

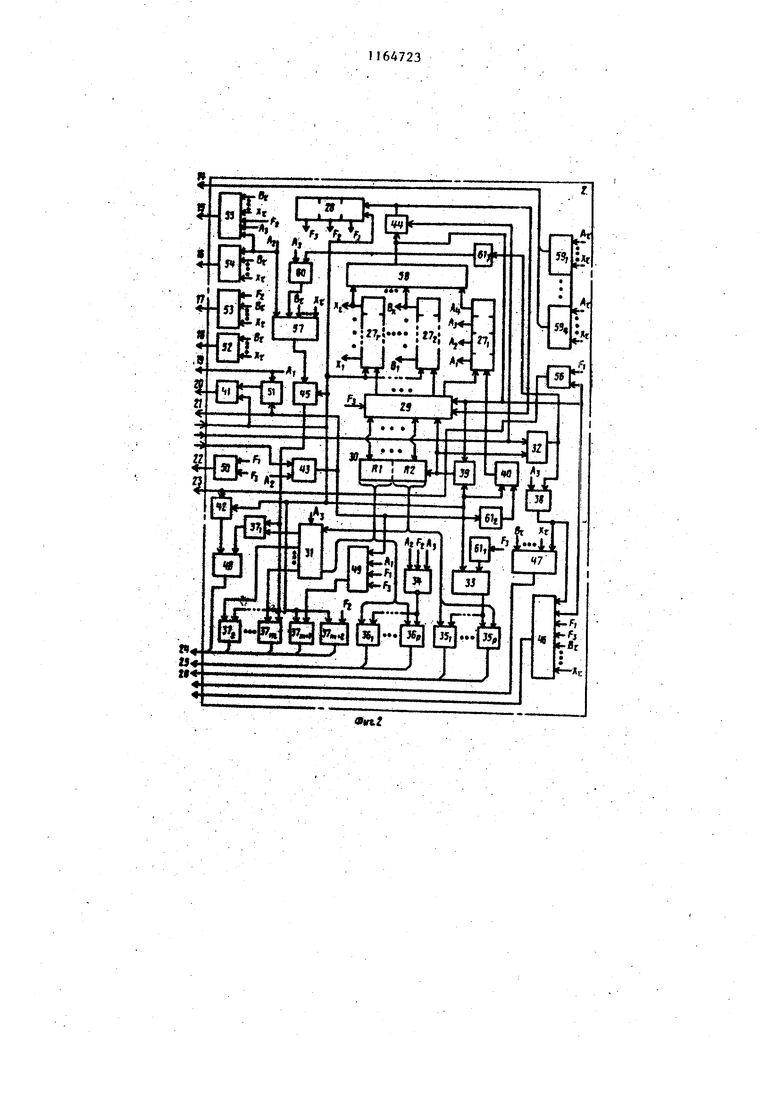

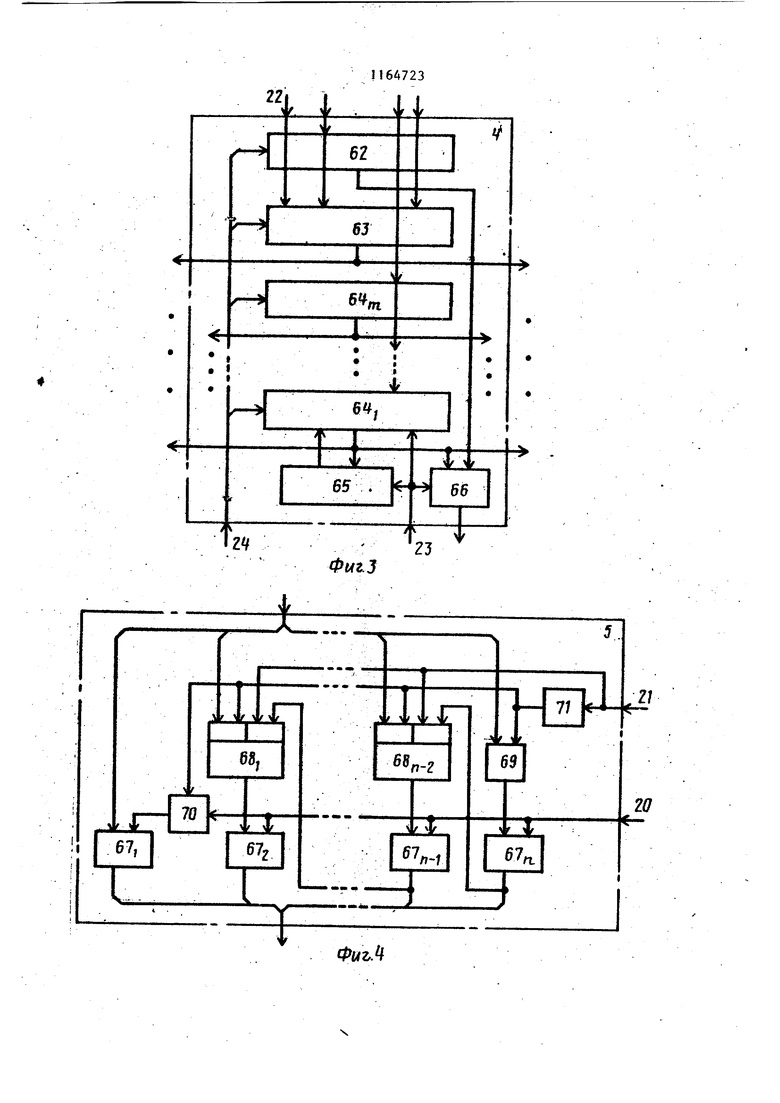

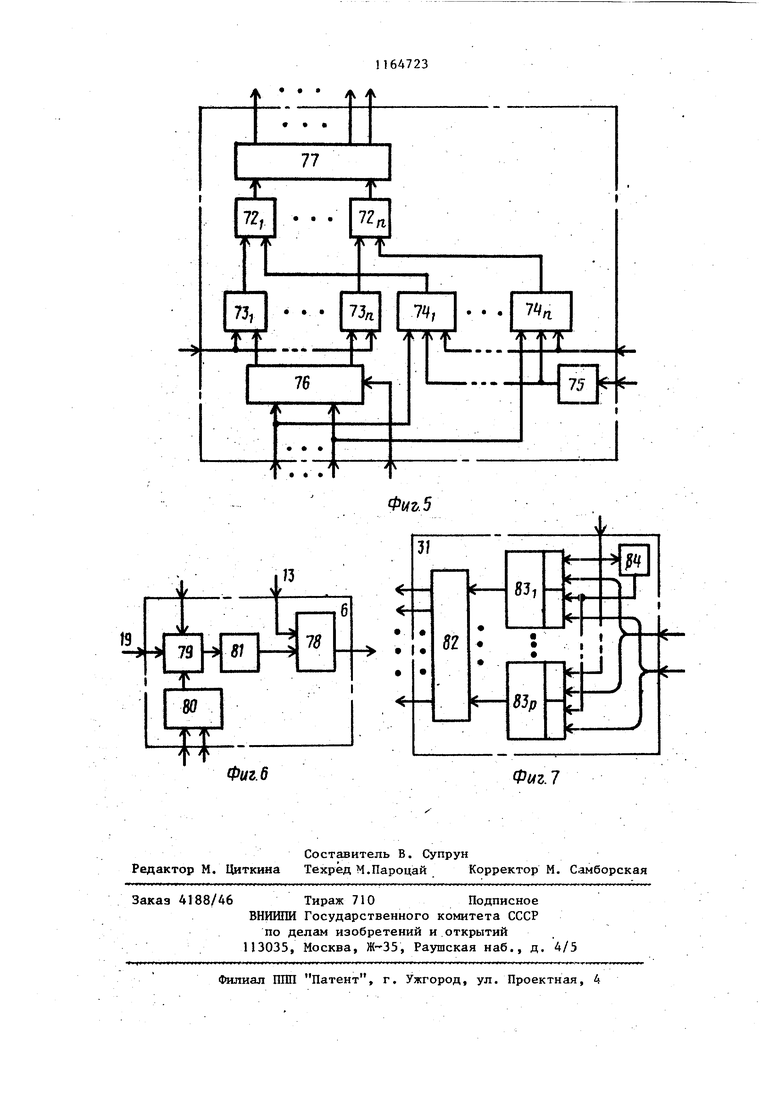

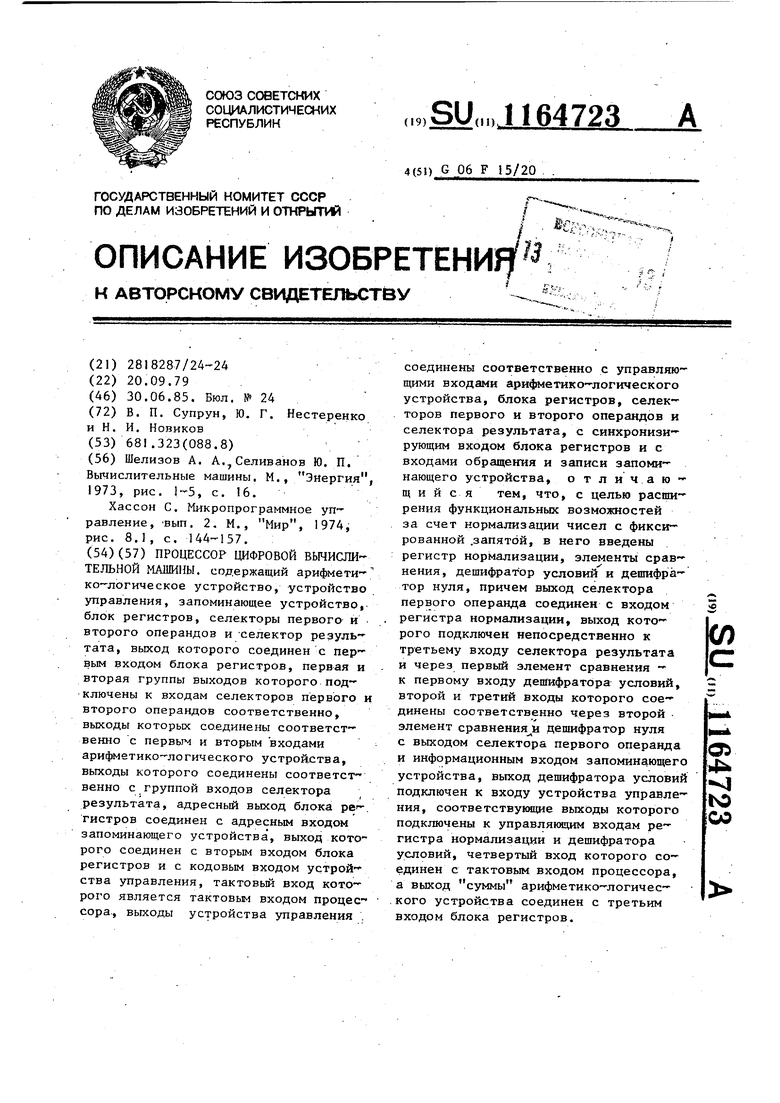

На фиг. 1 представлена блок-схема процессора; на фиг. 2 схема устройства управления; на фиг. 3 - схема блока регистров на фиг, 4 - схема регистра нормализации; на фиг. 5 схема управляемого дешифратора; на фиг. 6 - схема дешифратора условия; на фиг. 7 - схема дешифратора записи

Процессор содержит арифметико-логическое устройство 1, устройство управления 2, запоминающее устройство 3, блок 4 регистров, регистр 5 нормализации, дешифратор 6 условия, селектор 7 первого операнда, селектор 8 второго операнда , селектор 9 результата, дешифратор 10 нуля, элементы 1 I и 12 сравнения. Тактовый вход 13 процессора соединен с тактовыми входами устройства 2 управления и четвертым входом дешифратора 6 условия. Устройство 2 управления имеет выходы I4-26.

Устройство 2 управления (фиг. 2) содержит г сдвиговых регистров 27 управления, сдвиговый регистр 28, уп равляемый дешифратор 29, регистр 30, дешифратор 31 записи, триггеры 32 и 33, элемент ИЛИ-НЕ 34, р элементов И 35, р элементов И 36, (т + 2) элементов И 37, элементы И 38-45, элементы ИЛИ 46-58, q элементов ИЛИ 59, элемент И 60 и три элемента НЕ 61 (61

Блок 4 регистров (фиг. 3) содержит адресный регистр 62, инфОрмационный регистр 63, m регистров 64 общего назначения, счетчик 65 команд и коммутатор 66. .

Регистр 5 нормализации (фиг. 4) содержит п триггеров 67, п-2 элеменfoB И-ИЛИ 6В, элементы И 69 и 70 и инвертор 71.

Управляемый дешифратор 29 (фиг. 5 содержит п элементов, ИМ 72, п элементов И 73, п элементов И 74, ийвертор 75, буферный регистр 76 кода операции и дешифратор 77 кода операции.

Дешифратор 6 условия (фиг. 6) содержит триггер 7.8, коммутатор 79, элемент ИЛИ 80 и инвертор 81.Дешифратор 31 записи (фиг. 7) содержит деспифратор 82, р элементов И-ИЛИ 83 и инвертор 84.

Работает процессор специализированной вычислительной машины при выполнении команды нормализации числа с фиксированной запятой следующим образом.

Перед вьтолнением нормализации операнд располагается в регистре 64t общего назначения. В .последнем цикле вьшолнения предц|:1ущей команды с последнего разряда соответствующего сдвигового регистра 27 управления сигнал поступает на вьпсод элемента ИЛИ 5В. С выхода элемента ИЛИ 58 сигнал через элемент 56 поступает на управляющие входы регистра 64) общего назначения, коммутатора 66 и на вход продвижения счетчика команд 65,. при этом коммутатор настраивается на подачу на адресный вход запоминающего устройства 3 содержимого регистра 64 общего назначения (адрес командного слова), счетчик 65 команд увеличивает на единицу код адреса команды, а регистр 64 общего назначения настраивается на прием кода с второго входа, соединенного с выходом счетчика 65 команд. Кроме того, сигнал с выхода элемента ИЛИ 58 через элемент ИЛИ 46 поступает на вход обращения . запоминающего устройства 3, командное слово с выхода которого поступает на кодовый вход, устройства 2 управления, при этом поле признака адресации командного слова поступает на входы триггера 32 и элемента И 44, поле кода операции поступает на вход управляемого дешифратора 29, а поля R и R2 командного слова поступают на вход регистра 30. В конце цикла при появлении и aIyльca на шине 13 тактовой частоты продвинутое значение счетчика 65 команд записывается в регистр 6i4| общего назначения сигналом, поступившим с выхода элемента И 42 через элемент ИЛИ 48 на сихронизирующий вход ре- гистра. 64J общего назначения.

Если очередное командное слово должно выполняться в-формате RR (нулевое значение разряда признака адресации) , то элемент И 44 закрыт, на его выходе сигнал отсутствует, поэтему сигналы с выходов элемента .ИЛИ 58 и инвертора 75 открывают элементы И 74f- 74„ в управляемом дешифраторе 29 и код операции через элементы И 74,- 74п, элементы ИЛИ 72 - 72 поступает на вход дешифратора 77 КО да операции, на последнем выходе кото рого, если код операции соответствует команде нормализации числа с фиксиро ванной запятой, появляется сигнал И поступает на вход сдвигового регистр 27 управления и по импульсу тактойой частоты, прошедшему через элеменя И 40 на синхронизирующий вход сдвит о- вого регистра 27( управления, включа ет его первый разряд (элемент И 40 оТ крыт для. импульс а тактовой часТоты. так как сигнал на выходе элемента И 43 отсутствует, а на выходе элемен та НЕ 61 присутствует). Одновременно с этим так как элемент И 39 открыт сигналом с выхода элемента ИЛИ 58 по импульсу тактовой частоты, вырабатывающего сигнал на выходе элемента И 39, значение признака адресации зaпиcывaetcя в триггер 32, значение полей R1 и R2 записывается в регистр 30, а значение кода операции запишетт ся в буферньш регистр 76 кода опера-, ции. Кроме того, в этом же цикле по импульсу тактовой частоты выталкивается единичный сигнал с последнего разряда сдвигового регистра 21 управления, который, был ранее включён и обеспечивал сигнал на выходе элемен та ИЛИ 58, после чего начинается первый цикл выполнения команды нормализации. Если же поле адресации в вы бранном командном слове указьшает на режим RX, не RR (единица в поле признака адресации), то описанный процесс повторяется с той лишь разницей, что в триггер 32,записываетря единица и на выходе элемента И 44. присутствует сигнал, который запрещает прохождение кода операции через элементы И 74 - 74 (команда с нулевым кодом операции отсутствует в системе команд), поэтому по импульсу тактовой частоты вклю чается не первый разряд сдвигового регистра 27 управления, а первый раз ряд сдвигового регистра 28. Регистр 28 обеспечивает выборку второго операнда в режиме RX для других команд из системы команд и подготовку исполнительного адреса для команды нормализации числа с фиксированной запятой, которая имеет один операнд и два результата. При этом в первом цикле выполнения режима выборки второго операнда в режиме RX сигнал F с выхода первого разряда сдвигового регистра 28 через элемент ИЛИ 56 обеспечивает подачу на адресный.вход запоминающего устройства 3 кода адргеса смещения из регистра 64,.общего назначения (в режиме RX командное слово занимает две соседних ячейки в памяти), а через элемент ИЛИ 46 - сигнала обращения к запоми1гаК)цему устройству 3. Смещение с выхода запоминающего устройства 3 поступает на второй вход информационного регистра 63 в блоке 4 регистров, который сигналом Pf, поступивпвш через элемент ИЛИ 50, выход 22 устройст.ва 2 управления на управляюорей вход информационного регистра 63, настроен на прием информацни с второго его входа. Сигнал F через злемеят ИЛИ 49 поступает на вход элемента 37., готорьй в конце данного цикла пропускает импульс тактовой частоты с тактового входа 13 процессора на синхронизирующий вход информационного регистра 63, в который и записывается смещение. По этому же импульсу тактовой частоты единичный сигнал продвигается из первого во второй разряд сдвигового регистра 28,-который) вырабатывает сигнал F- . Во втором цик ле режима выборки второго операнда производится модификация Гсуммиро- вание смещения с индексом, который 64j общего на- находится в регистре задаваемом полем R-2 козначения, мандного слова. Код j в поле R2 регистра 30, поступая через открытые элементы И 35,-35р, выход 26 устройства 2 управления на управляющий вход селектора 8 второго операнда, обеспечивает подачу содержимого регистра 64 j общего назначения на ; второй вход арифметико-логического устройства J. Так как на выходе элемента ИЛИ-НЕ 34 присутствует сигнал Е , то элементы И закрыты и на выход селектора 7 первого операнда подается не содержимое регистра 64j общего назначения, указанное полем R в регистре 30, а содержимое информационного регистра 63, котор.оё П9с.тупает на первый вход ари метикологического устройства 1. Сигнал F, через элементы ИЛИ 55 и 53, выходы 15 и 17 устройства 2 управления по.ступает на первый и третий управляю щие входы арифметико-логического . устройства 1, которые служат соответственно для подачи прямым кодом пер вого и второго операндов, при этом на выходе суммы арифметико-логического устройства I появляется исполнительный адрес (сумма смещения и инде са), который через третий вход блока 4 регистров поступает на .вход адресного регистра 62. Кроме того, сигнал Fj разрешает прохождение импульса тактовой частоты через элемент И на синхронизирукяций вход адресного регистра 62 и запись в него исполнительного адреса. По этому же импульсу тактовой час тоты единичный сигнал перемещается с второго в третий разряд сдвигового регистра 28, который вырабатывает сигнал Fj.. 38 третьем цикле режима выборки второго операнда в режиме RX, который для команд нормализации не имеет смыслового значения (используется для других команд из системы команд), на адресный.вход запоминающего устройства подается содержимое адресного регистра 62, так как сигнал на управляющем входе коммутатора 66 отсутствует. Через элемент ИДИ 46 сигнап Fj поступает на вход обращения запоминаняцего устройства 3, с выхода которого код второго опе ранда поступает на второй вход блока 4 регистров и второй вход информационного регистра 63. Кроме того, сигнал F через элемент ИЛИ 50, выход 22 устройства 2 управления поступает на управляющий вход информационного регистра 63 и настраивает его на прием информации с второго его входа. Сигнал F через элемент ИЛИ 49, поступая на вход элемента И 37 , раз решает прохождению импульса тактовой частоты на синхронизирующий вход информационного регистра 63, в который и записьшается второй операнд. При появлении сигнала F, J на выходе элемента НЕ 61| на входе триггера 33 сигнал отсутствует, поэтому по импульсу тактовой частоты в триггер 33 записывается ноль, который на протяж НИИ первого цикла выполнения любой команды обеспечивает подачу второго операнда (вместо подачи индекса с jpH 11 3 гистра 641 общего назначения) . Кроме J -, . того, сигнал F, на третий управляющий вход упраиляемого дешиф ратора 29, обеспечивает подачу кода операции с буферного регистра 76 кода операции через элементы И 73,-73„, . элементы ШШ на вход дешифратора 77 кода операции,, и при коде операции, соответствующем команде нормализации, по импульсу тактовой частоты, поступившему через элемент И 40 на синхронизирующий вход сдвигового регистра 27 управления, в его первый рйзряд записывается единичный сигнал, после чего начинается собственно выполнение команды нормализации числа с фиксированной запятой. .Нормализация числа с фиксированной запятой Производится следующим образом, . В первом, цикле вьтолнения команды на выходе сдвигового рвгистра 27 вырабатывается сигнал А . Код i выхода-поля R1 регистра 30 через элементы И , выход 25 устройства 2 управления поступает на управляющий вход селектора 7 первого операнда и настра;ивает его на пропускание на его выход содержимого регистра 64, общего назначения. Число с выхода селектора 7 первого операнда поступает на входы элемента 11 сравнения, дешифратора 10 нуля и на информационный вход регистра 5 нормализации, на управляющем входе 21 которо-го сигнал отсутствует, поэтому данное число поступает на входы триггеров 67.-67„. Элемент II сравнения вырабатывает сигнал на своем выходе при неравенстве знакового разряда числа самому старшему разряду мантиссы числа (число нормализовано), а дешифратор 10 нуля вырабатывает сигнал .i на своем быходе при равенстве числа нулю (число нормализовано). Таким образом, на выходе элемента ИЛИ 80 и , соответственно, на первом входе коммутатора 79 вырабатывается сигнал, если число нормализовано, и сигнал отсутствует, если число нужно нормализовать. Сигнал через выход 19 уст ройства 2 управления поступает на управляющий вход дешифратора 6 усло ВИЯ и настраивает коммутатор 79 на пропускание сигнала с его первого входа, через инвертор .81 на вход триггера 78. Импульс тактовой часто ты с тактового входа 13 процессора записывает значение сигнала с выхода инвертора 81 в триггер 78. Кроме того, нормализуемое число по этому же импульсу, прошедшему через эле мент И 41, открытый по первому входу сигналом А,(прошедшим через элемент ИЛИ 51) , через выход 20 устройства 2 управления на синхронизирующий вход регистра 5 нормализации, записывается в триггеры 67) 67 (при отсутствии сигнала на выходе 21 устройства 2 управления элемент И 70 для синхро низации открыт). Сигнал Af, поступая через элемент ИЛИ 49 на вход элемен та И разрешает прохождение имт пульса тактовой частоты на сихрони зирующий вход информационного регист ра 63, который отсутствие сигнала на управляющем входе настроен на запись информации с его первого входа, сое- диненного с третьим входом блока ре гистров и с выходом суммы арифметикологического устройства I. Первый, второй, третий и четвертый управляющие входы арифметико-логическогр устройства 1 служат соответственно для подачи первого операнда прямым кодом задания переноса в младший разряд арифметикО логического устройства I подачи второго операнда прямым кодом и подачи второго операнда обратным кодом. Так как сигналы на управляющих входах арифметико-логического устройства I в первом цикле выполнения команды нормализации отсутствуют на выходе суммы арифметико логичес кого устройства I присутствует ну левой код, который и записывается в информационный регистр 63. Кроме то- го, импульс тактовой частоты, поступая через элемент И 40 на синхронизи рующий вход сдвигового регистра 27j управления, перемещает единичный сиг нал с его первого разряда во второй его разряд и выработается : сигнал ,АЛ, который определяет второй цикл выполнения команды нормализации. Если исходное число нормализовано, то после первого цикла выполнения команды сигнал на выходе дешифратора 6 условия, дополнительном входе устрой ства 2 управления и входе элемента И 43 отсутствует, поэтому при появлв НИИ импульса на тактовом входе 13 .процессора сигнал на синхронизирующие входы регистра 5 нормализации и ин формационного регистра 63 не поступа ет и данные регистры не изменяют сво его .состояния. Отсутствие сигнала на выходе элемента И 43 открывает элемент И 40, и импульс тактовой частоты перемещает единичный сигнал с второго в третий разряд сдвигового регистра 27, управления. При этом содержимое регистра 5 нормализации записывается в регистр 64 общего назначения таким образом, как описано ниже. Если же исходное число не норма- . лизовано, то на вьпсоде дешифратора 6 условия после первого цикла выполне- ния команды-и соответственно на пер вом входе элемента И 43 сигнал присутствует и второй цикл выполнения команды протекает следуншщм образом. Сигнал Aj, поступая на вход элемента ИЛИ-НЕ 34, обеспечивает выработку нулевого кода на выходах элементов И , который обеспечивает подачу на выход селектора 7 первого опёранда и соответственно на первый вход арифметико-логического устройства 1 содержимого информационного регистра 63. Этот же сигнал А, пройдя через элементы ИЛИ 55 и 54 и выходы 15 и 16 устройства 2 управления на первый-и второй управляющие входы арифметико-логического устройства I, обеспечивает получение иа выходе суммы арифметико-логического устройства I увеличенного иа единицу младшего разряда содержимого информационного регистра 63, Кроме того, сигнал Ag, пройдя через элемент ИЛИ 57, открывает элемент И 45. Этот же сигнал А2, пройдя через элемент И 43 во-первых, поступает через выход 21 устройстве 2 управления иа зшравлягг ющий вход регистра 5 нормализации и . запрещает срабатывание элемента И 70 и прохождение информации на вход триггеров 672--67, с информационного входа регистра 5 нормализации и разрешает подачу на вход триггеров 67j 67fj. информации с правых (по располо- жению на схеме) триггеров 67,,-67 . Во вторь1х, пройдя через элемент ШШ 51 , сигнал с выхода элемента И 43 открывает элемент И 41. В-третьих, пройдя через элемент ИЛИ 49, сигнал открывает элемент И 37fn+i В-четвертых, пройдя через элемент НЕ 6, сигнал запрещает срабатывание элемента И 40 и соответственно продвижение единичного сигнала в сдвиговом регистре 27( управления.

Кроме того, отсутствие сигнала на выходе 19 устройства 2 управления настраивает коммутатор 79 на пропуекание сигнала с выхода элемента 12 , сравнения через второй вход коммута 5 тора 79, инвертор 81 на вход тригге ра 78. Элемент 12 сравнивает знаковьй разряд и разряд, следующий пос ле старшего разряда мантиссы числа, находящегося в регистре 5 нормализа 10 ции (выходы триггеров 67j и 67 в регистре 5 нормализации) и срабатыва ет аналогично элементу 1 сравнения. При поступлении импульса на шину 13 тактовой частоты сдвиговый регистр15 27{ управления не изменяет своего состояния, в регистре 5 нормализации происходит сдвиг мантиссы влево на один разряд (последний разряд заполняется нулями), увеличенное на 20 единицу .значение информационного регистра 63 с выхода суммы арифметикологического устройства 1 записывается в информационный регистр 63, а пред-верительное (не сдвинутое) число из 25

регистра 5 нормализации записывается в регистр 64 общего назначения, так как код с выхода поля R1 регистра 30 через дешифратор 31 записи открывает элемент И 37 который пропускает JQ синхроимпульс с выхода элемента И 45 на синхронизирующий вход регистра 64 общего назначения, при этом сигнал Aj подается только на те входы элементов ИЛИ 59 59t (на чертеже обозначен в виде А), чтобы на их

выходах (выход 14 устройства 2 управления) сформировался код, обеспечи вающий подачу на выход селектора 9 результата и, соответственно.на вхо- . ды регистров 64 общего назначения содержимого регистра 5 нормализации через его третий вход.

Если после сдвига во втором цикле I . . . число станет нормализованным, в триг-45

гер 78 по окончании импульса так то-вой частоты запишется нулевой сигнал и он с выхода дешифратора 6 условия поступит на дополнительный вход устройства 2 управления, после чего в то- 50 рой цикл (определяется выдачей сигнала Ag на выход сдвигового регистра 27 управления) выполняется аналогич но выполнению второго цикла при нормализованном исходном значении числа, 55 причем в регистр 64 общего назначения при этом записывается нормализО ванное число. Если же после выполнен

ния второго цикла число не нормализо|3ано,. то второй цикл в режиме сдвига содержимого регистра 5 нормализации повторяется . Таким образом, второй цикл при выполнении команды иормали зации повторяется (К + I) раз, где К - константа сдвига при нормализации, указывающая на число сдвигов мантиссы (на один разряд при каждом .сдвиге) при нормализации. Константа сдвига К при нормапизации формируется в информационном регистре 63. При нулевом сигнале на выходе дешифратора 6 условия второй цикл вы- полнения команды нормализации выполняется последний раз, после чего единичный сигнал перемещается из второго разряда в третий разряд сдвигового регистра 27( управления, который вырабатывает сигн.ал А, и начинается выполнение третьего цикла.

В третьем цикле выполнения команды нормализации производится запись второго результата (константы сдвига в память, при зтом сигнал Aj, поступая на вход элемента ИЛИ-НЕ 34, обеспечивает выработку на выходах элементов И нулевого кода, при котором содержимое информационного регистра 63 подается на выход селектора 7 первого операнда и соответственно на первый информационный вход запоминающего устройства 3. Сигнал Ач, поступающий на управляющий вход дешифратора 3 записи, обеспечивает подачу кода j с выхода поля R2 регистра 30 на вход дешифратора 82, сигнал с выхода которого открывает элемент И 37,|. Кроме того, сигнал А 5 через элемент ИЛИ 55, выход 15 устройства 2 управления, поступая на первый управлякщий вход арифметико-логического устройства 1, обеспечивает подачу константы сдвига на выход суммы арифметико-логического устройства 1. Кроме того, сигнал АЗ подается на входы тех элементов ИЛИ 594-59 (на чертеже показаны в виде Ар), чтое1ы на их выходах и соответственно на управляющем входе селектора 9 результата выработать код, обеспечивающий подачу содержимого с выхода су-ммы ари я етико-логического устройства 1 на выход селектора 9 результата и входы регистров 64 общего назначения.

Если команда нормализации выполняется в режиме RR (низкий потенциал 11 на выходе триггера 32), то сигнал А проходит через элемент И 60, элемент ИЛИ 57 и открывает элемент 1И 45, при этом импульс тактовой частоты с шины 13 тактовой частоты проходит через элемент И 45, элемен И 37; на синхронизирующий вход регистра 64 общего назначения« sat- письюает в него константу сдвига. Если же команда вьтолняется в режи:ме RX (высокий потенциал на выходе триггера 32), то сигнал АЗ через элемент И 38, через элементы ШШ 46 и 47 поступает на вход обращения и вход записи запоминающего устройства 3, и константа сдвига записы вается в запоминающее устройство 3 по исполнительному адресу,. храня-312щемуся в адресном регистре 62 и по даваемому через коммутатор 66 на адресный вход запоминающего устройства 3. После этого от импульса тактовой частоты единичный сигнал перемещается из третьего в четвертый разряд сдвигового регистра 274, который вырабатьгеаетсигнал А, обеспечивагощий, как описано вьппе, выработку очередного командного слова. При выполнении других команд из системы команд включаются соответствующие-сдвиговые регистры 27 управления, которые вырабатывают на своих выходах сигналы, с помощью которых вырабатываются соответствзпощие микро операции на выходах устройств 2 управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Центральный процессор | 1979 |

|

SU960830A1 |

| Операционное устройство процессора | 1979 |

|

SU809189A1 |

| Асинхронное устройство управления | 1979 |

|

SU826351A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Центральный процессор | 1980 |

|

SU890400A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

| Микропрограммное вычислительное устройство | 1984 |

|

SU1229761A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

ПРОЦЕССОР ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ, содержащий арифметико-логическое устройство, устройство управления, запоминающее устройство,блок регистров, селекторы первого и второго операндов и -селектор результата, выход которого соединен с первым входом блока регистров, первая и вторая группы выходов которого подключены к входам селекторов первого и второго операндов соответственно, выходы которых со.единены соответственно с первые и вторым входами арифметико-логического устройства, выходы которого соединены соответст венно с группой входов селектора результата, адресный выход блока ре--, гистров соединен с адресным входом запоминающего устройства , выход которого соединен с вторым входом блока регистров и с кодовым входом устройства управления, тактовьй вход которого является тактовым входом процессора, выходы устройства управления Jj3 соединены соответственно с управляющими входами арифметико-логического устройства, блока регистров, селекторов первого и второго операндов и селектора результата, с синхронизирующим входом блока регистров и с входами обращения и записи запоминающего устройства, отлич.ающ и и с я тем, что, с целью расширения функциональных возможностей за счет нормализации чисел с фиксированной .запятой, в него введены регистр нормализации, элементы сравнения, дешифратор условий и дешифратор нуля, причем выход селектора первого операнда соединен с входом регистра нормализации, выход котосл рого подключен непосредственно к третьему входу селектора результата и через первый злемент сравнения - к первому входу дешифратора условий, второй и третий входы которого соединены соответственно через второй элемент сравнениями дешифратор нуля с выходом селектора первого операнда 05 и информационным входом запоминающего to устройства, выход дешифратора условий подключен к входу устройства управления, соответствукицие выходы которого О9 подключены к управляющим входам регистра нормализации и дешифратора условий, четвертый вход которого соединен с тактовым входом процессора, а выход суммы арифметико-логического устройства соединен с третьим входом блока регистров.

Фиг.1

ФигМ

| Шелизов А | |||

| А.., Селиванов Ю | |||

| П | |||

| Вычислительные машины | |||

| М., Энергия, 1973, рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Хассон С | |||

| Микропрограммное управление, Вып | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для электрической передачи изображений без проводов | 1920 |

|

SU144A1 |

Авторы

Даты

1985-06-30—Публикация

1979-09-20—Подача