Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении отказоустойчивых многопроцессорных вычислительных систем.

Цель изобретения - расширение класса решаемых задач путем обеспечения возможности анализа и реконструкции структуры устройства в мажоритарном режиме при отказе каналов.

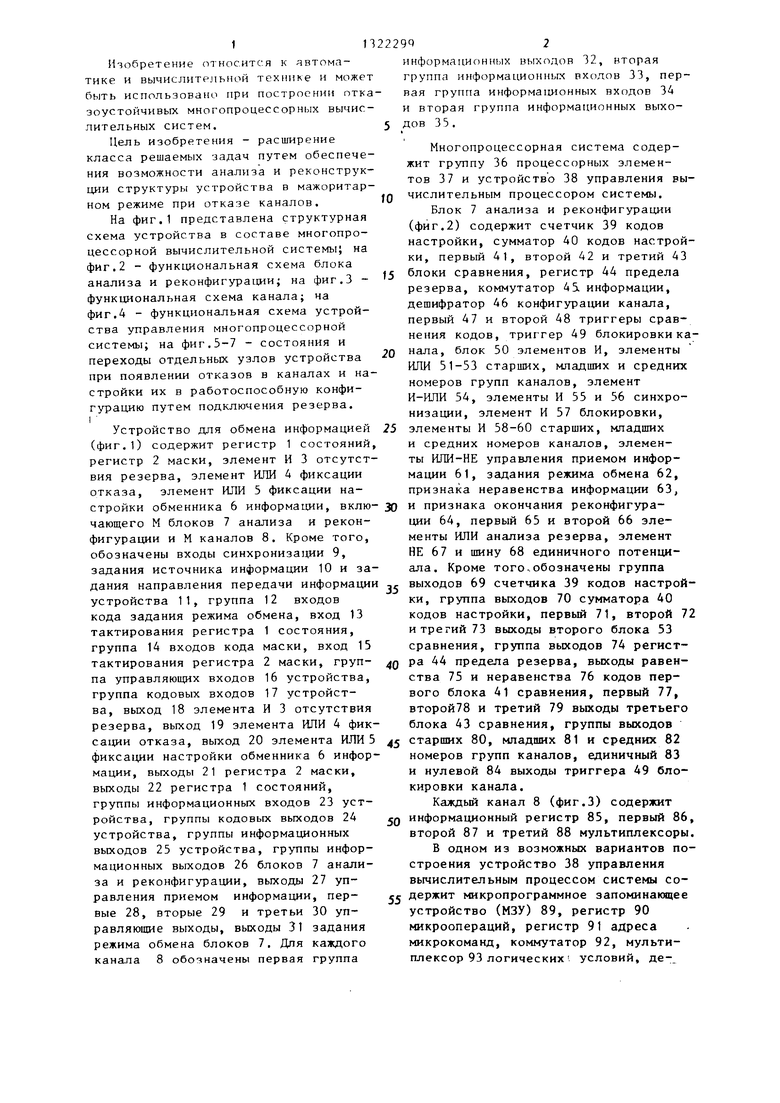

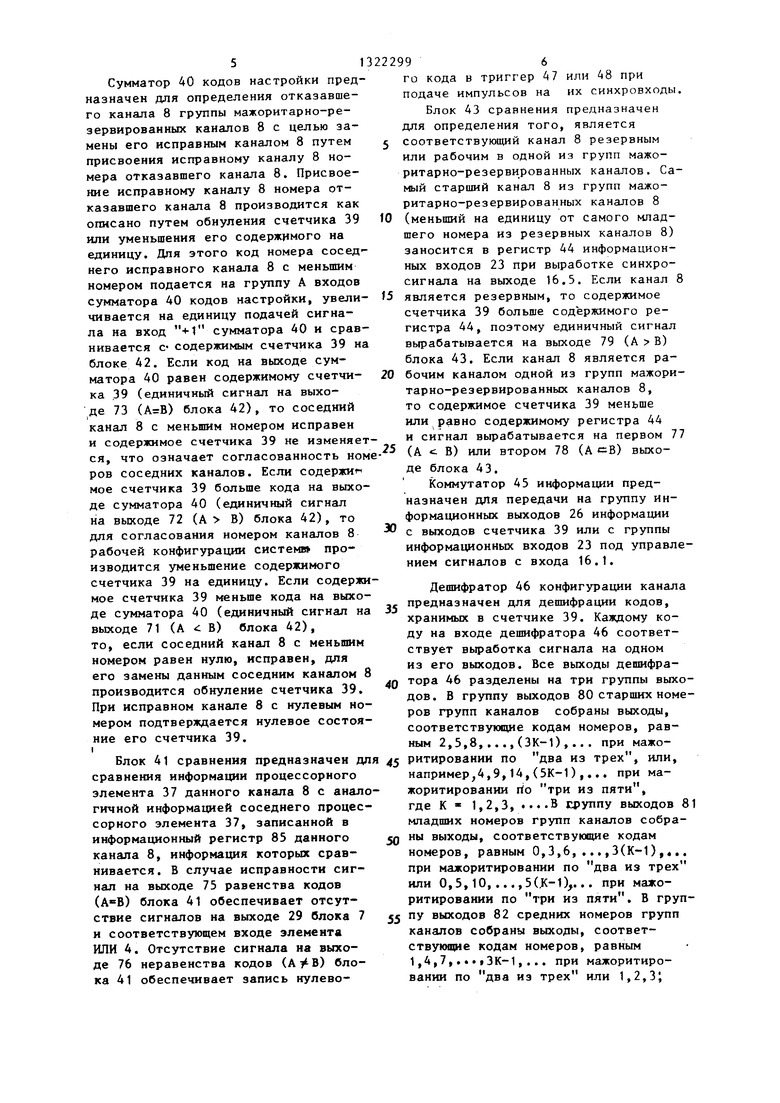

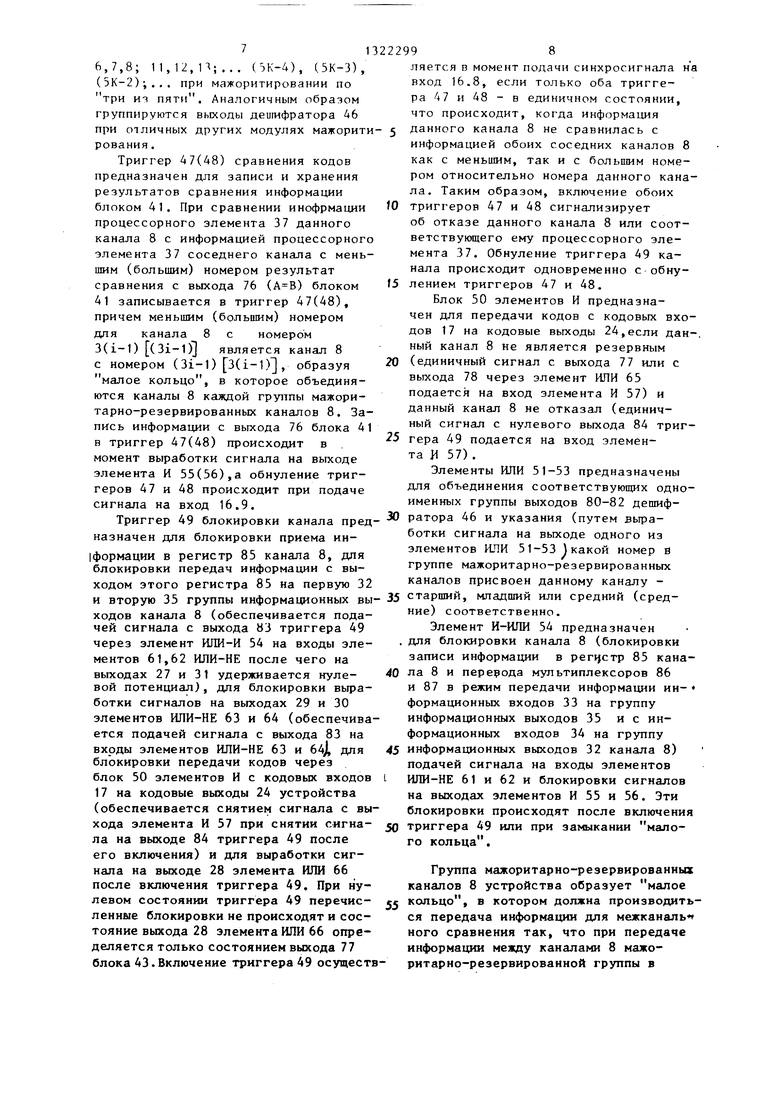

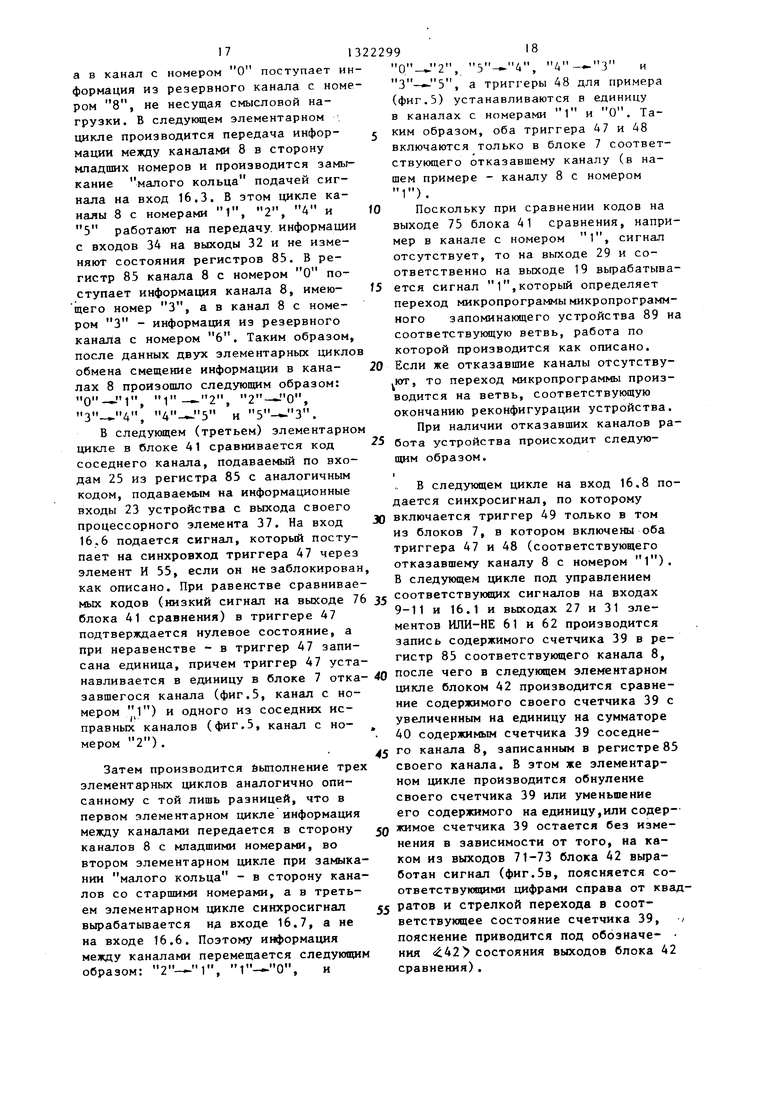

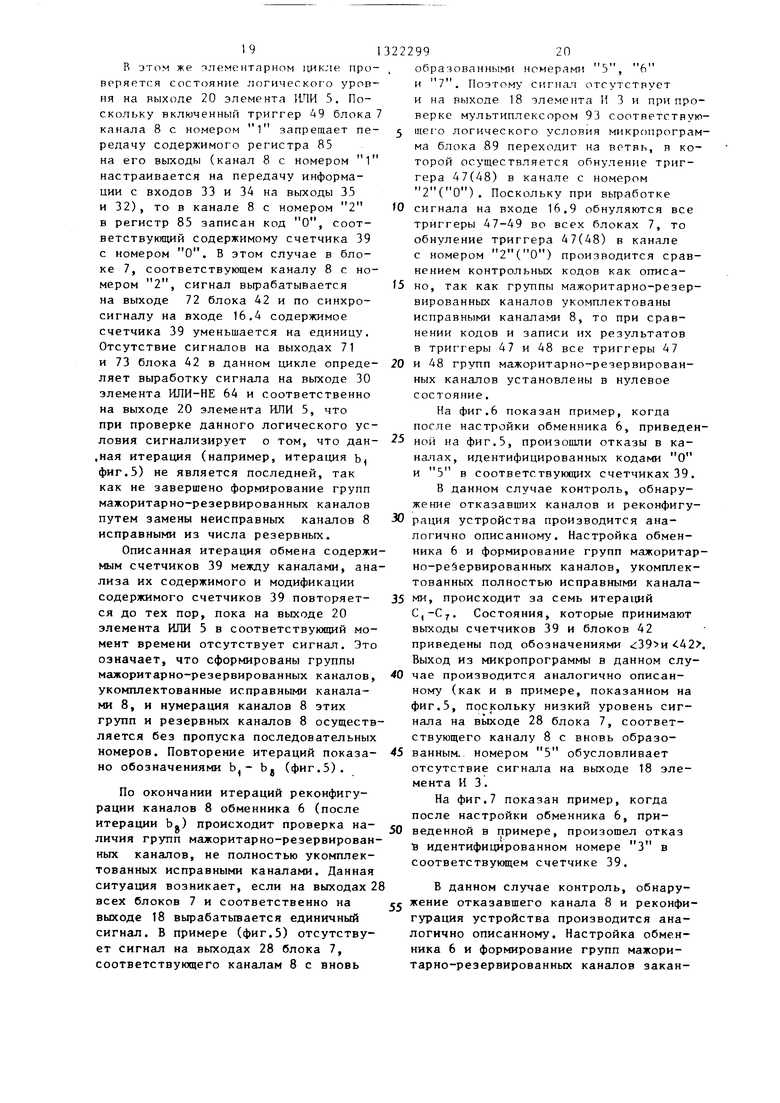

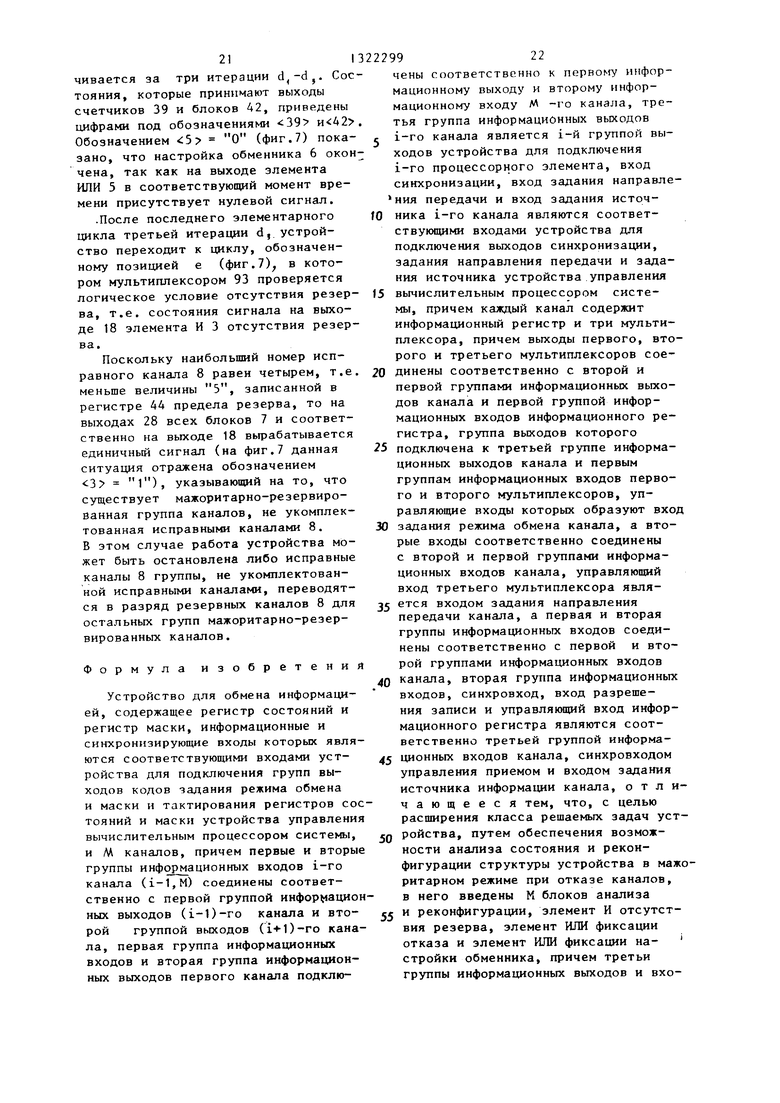

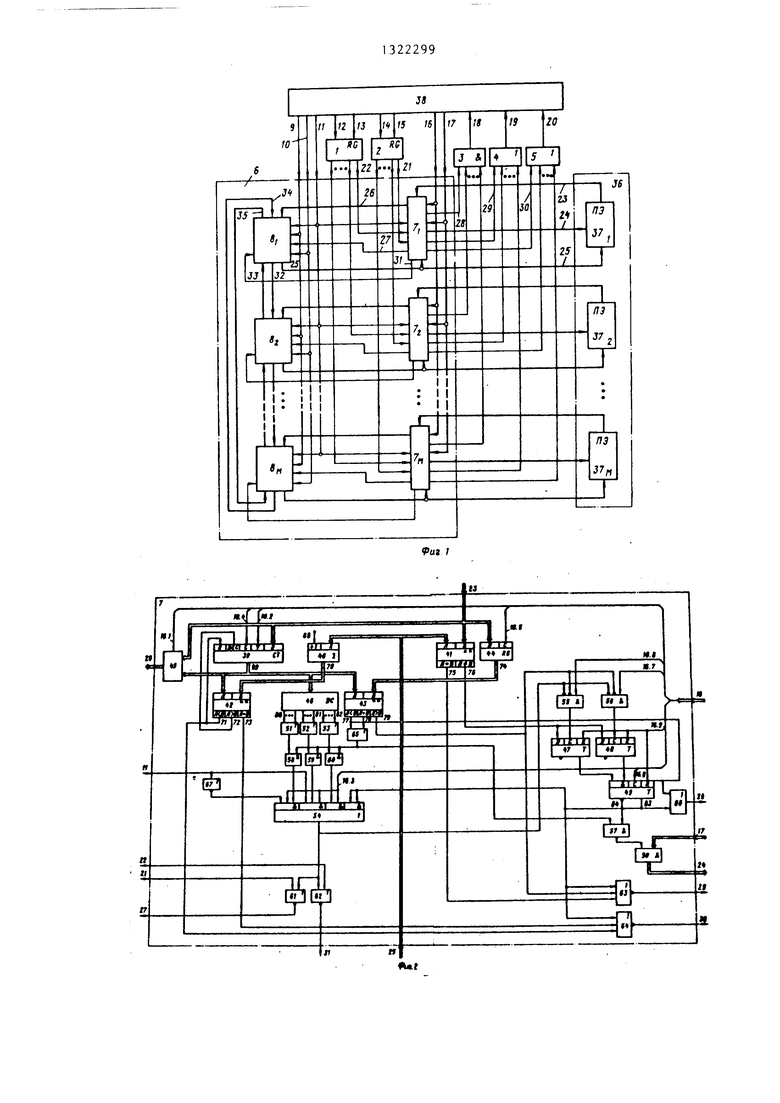

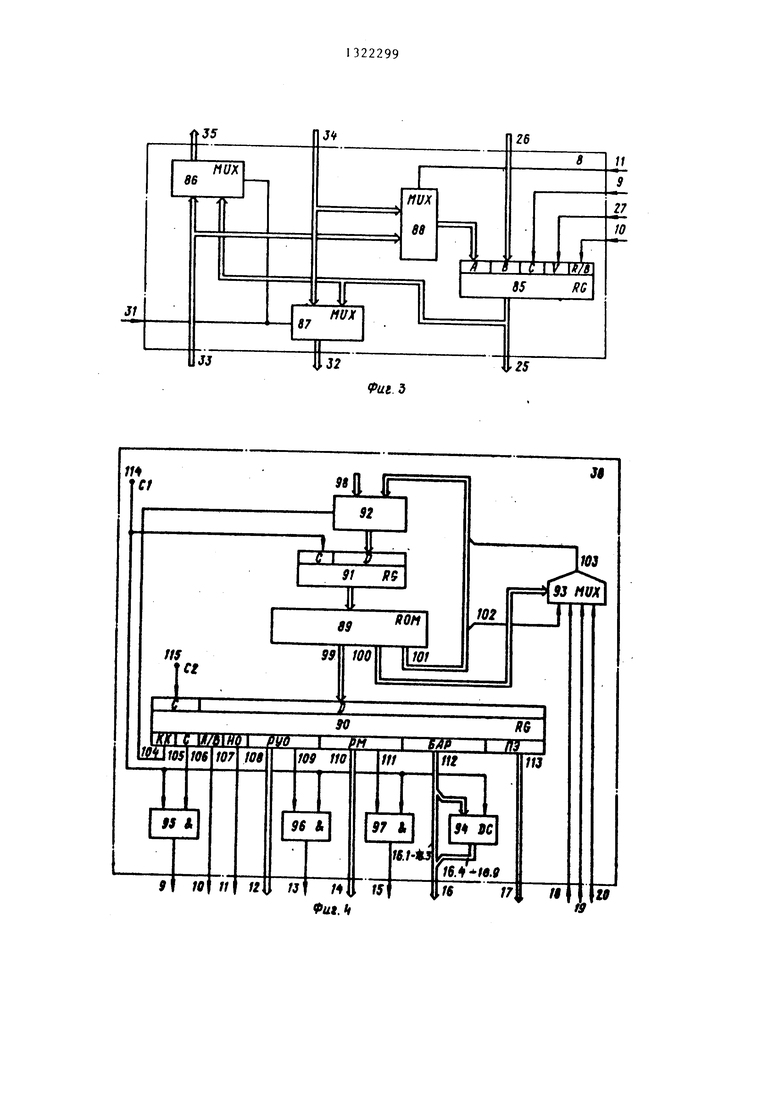

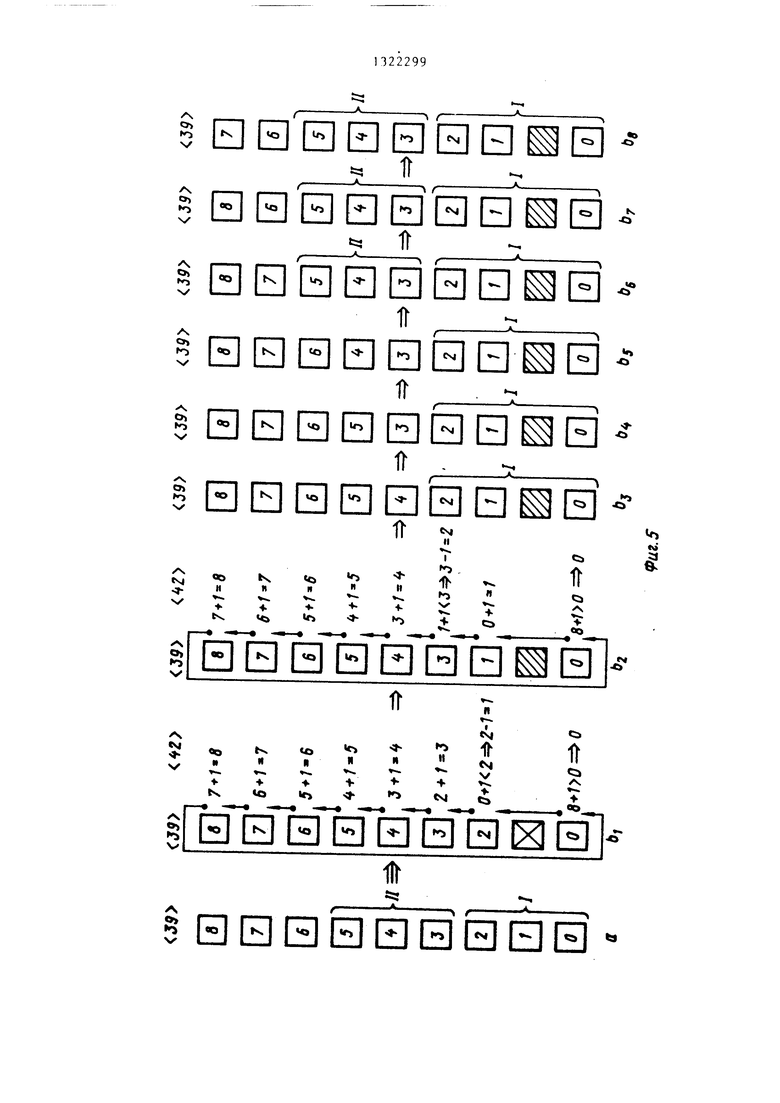

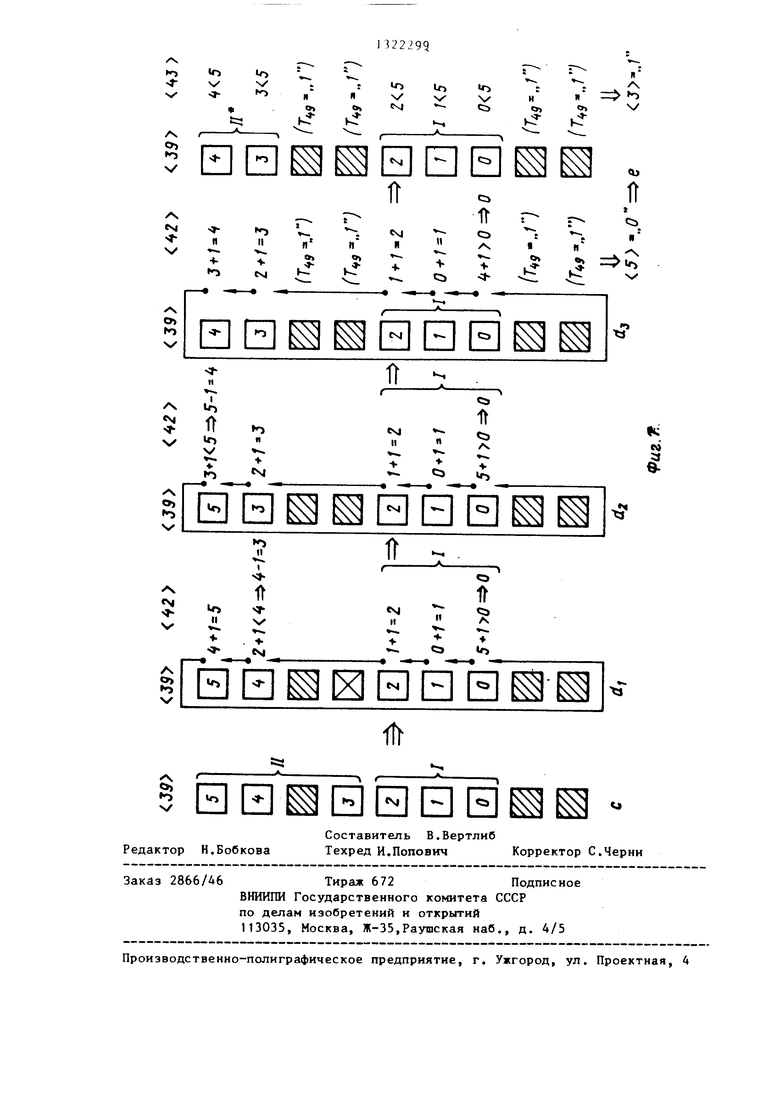

На фиг.1 представлена структурная схема устройства в составе многопроцессорной вычислительной системы; на фиг.2 - функциональная схема блока анализа и реконфигурации; на фиг.З - функциональная схема канала; на фиг.4 - функциональная схема устройства управления многопроцессорной системы; на фиг.5-7 - состояния и переходы отдельных узлов устройства при появлении отказов в каналах и настройки их в работоспособную конфигурацию путем подключения резерва.

I

Устройство для обмена информацией

(фиг.1) содержит регистр 1 состояний, регистр 2 маски, элемент И 3 отсутствия резерва, элемент ИЛИ 4 фиксации отказа, элемент ИЛИ 5 фиксации настройки обменника 6 информации, вклю- ЗО и признака окончания реконфигурачающего М блоков 7 анализа и реконфигурации и М каналов 8. Кроме того, обозначены входы синхронизации 9, задания источника информации 10 и заДания направления передачи информации ,, выходов 69 счетчика 39 кодов настройустройства 11, группа 12 входов кода задания режима обмена, вход 13 тактирования регистра 1 состояния, группа 14 входов кода маски, вход 15 тактирования регистра 2 маски, группа управляющих входов 16 устройства, группа кодовых входов 17 устройства, выход 18 элемента И 3 отсутствия резерва, выход 19 элемента ИЛИ 4 фиксации отказа, выход 20 элемента ИЛИ 5 фиксации настройки обменника 6 информации, выходы 21 регистра 2 маски, выходы 22 регистра 1 состояний, группы информационных входов 23 устройства, группы кодовых выходов 24 устройства, группы информационных выходов 25 устройства, группы информационных выходов 26 блоков 7 анализа и реконфигурации, выходы 27 управления приемом информации, первые 28, вторые 29 и третьи 30 управляющие выходы, выходы 31 задания режима обмена блоков 7. Для каждого канала 8 обозначены первая группа

ки, группа выходов 70 сумматора 40 кодов настройки, первый 71, второй 72 и третий 73 второго блока 53 сравнения, группа выходов 74 регист- Q pa 44 предела резерва, выходы равенства 75 и неравенства 76 кодов первого блока 41 сравнения, первый 77, второй78 и третий 79 выходы третьего блока 43 сравнения, группы выходов 45 старших 80, младпшх 81 и средних 82 номеров групп каналов, единичный 83 и нулевой 84 выходы триггера 49 блокировки канала.

Каждый канал 8 (фиг.З) содержит 5Q информационный регистр 85, первый 86, второй 87 и третий 88 мультиплексоры. В одном из возможных вариантов построения устройство 38 управления вычислительным процессом системы core держит микропрограммное запоминающее устройство (МЗУ) 89, регистр 90 микроопераций, регистр 91 адреса микрокоманд, коммутатор 92, мультиплексор 93 логических условий, де-

5

229Р2

информационных выходов 32, вторая группа информационных входов 33, первая группа информационных входов 34 и вторая группа информационных выходов 3 5 .

Многопроцессорная система содержит группу 36 процессорных элементов 37 и устройство 38 управления вычислительным процессором системы.

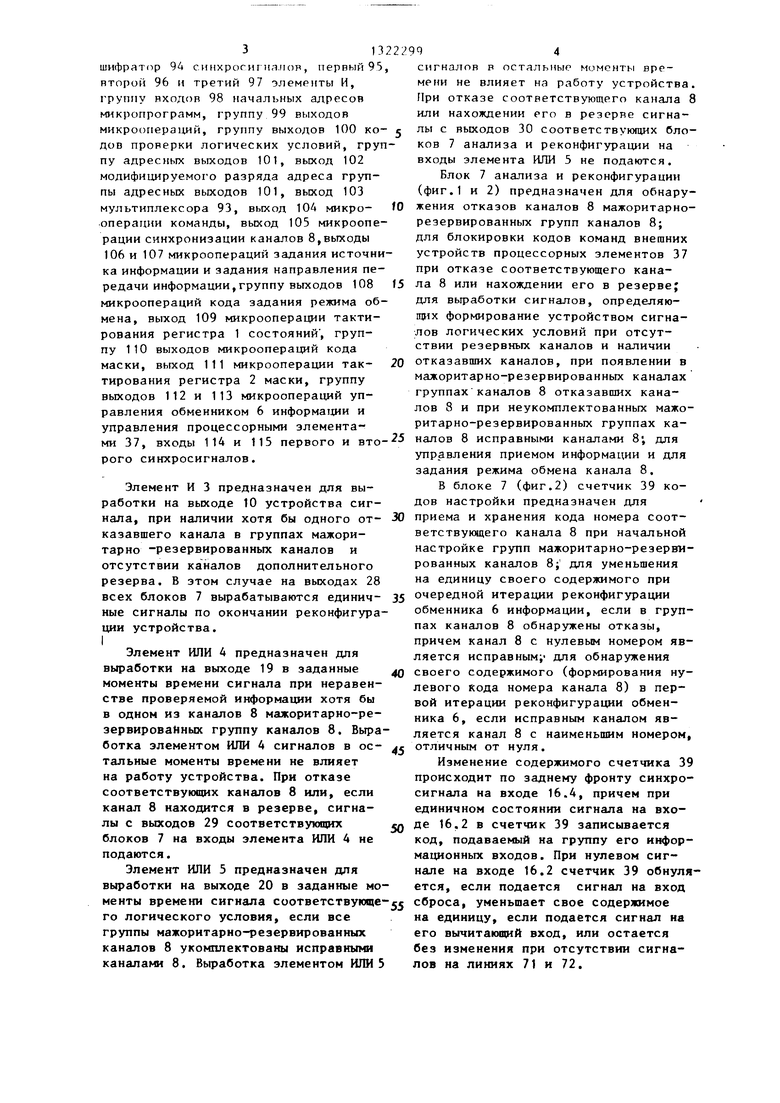

Блок 7 ана,пиза и реконфигурации (фиг.2) содержит счетчик 39 кодов настройки, сумматор 40 кодов настройки, первый 41, второй 42 и третий 43 блоки сравнения, регистр 44 предела резерва, коммутатор 4S информации, дешифратор 46 конфигурации канала, первый 47 и второй 48 триггеры сравнения кодов, триггер 49 блокировки канала, блок 50 элементов И, элементы ИЛИ 51-53 старших, младших и средних номеров групп каналов, элемент И-ИЛИ 54, элементы И 55 и 56 синхронизации, элемент И 57 блокировки, элементы И 58-60 старших, младших и средних номеров каналов, элементы ИЛИ-НЕ управления приемом информации 61, задания режима обмена 62, признака неравенства информации 63,

ции 64, первый 65 и второй66 элементы ИЛИ анализа резерва,элемент НЕ 67 и шину 68 единичногопотенциала. Кроме того,обозначеныгруппа

ки, группа выходов 70 сумматора 40 кодов настройки, первый 71, второй 72 и третий 73 второго блока 53 сравнения, группа выходов 74 регист- pa 44 предела резерва, выходы равенства 75 и неравенства 76 кодов первого блока 41 сравнения, первый 77, второй78 и третий 79 выходы третьего блока 43 сравнения, группы выходов старших 80, младпшх 81 и средних 82 номеров групп каналов, единичный 83 и нулевой 84 выходы триггера 49 блокировки канала.

Каждый канал 8 (фиг.З) содержит информационный регистр 85, первый 86, второй 87 и третий 88 мультиплексоры. В одном из возможных вариантов построения устройство 38 управления вычислительным процессом системы coдержит микропрограммное запоминающее устройство (МЗУ) 89, регистр 90 микроопераций, регистр 91 адреса микрокоманд, коммутатор 92, мультиплексор 93 логических условий, де-

шифратор 9Д сиихрогигиллов, первый 95 второй 96 и третий 97 элементы И, группу входов 98 начальных адресов микропрограмм, группу 99 выходов микроопераций, группу выходов 100 ко- дов проверки логических условий, группу адресных выходов 101, выход 102 модифицируемого разряда адреса группы адресных выходов 101, вькод 103 мультиплексора 93, выход 10А микро- операции команды, выход 105 микрооперации синхронизации каналов 8,выходы 106 и 107 микрооперации задания источника информации и задания направления передачи информации, группу выходов 108 микроопераций кода задания режима обмена, выход 109 микрооперации тактирования регистра 1 состояний , группу 110 выходов микроопераций кода маски, выход 111 микрооперации так- тирования регистра 2 маски, группу выходов 112 и 113 микроопераций управления обменником 6 информации и управления процессорными элементами 37, входы 114 и 115 первого и вто рого синхросигналов.

Элемент И 3 предназначен для выработки на выходе 10 устройства сигнала, при наличии хотя бы одного от- казавшего канала в группах мажоритарно -резервированных каналов и отсутствии каналов дополнительного резерва. В зтом случае на выходах 28 всех блоков 7 вырабатываются единич- ные сигналы по окончании реконфигурации устройства. I

Элемент ИЛИ 4 предназначен для

вьфаботки на выходе 19 в заданные моменты времени сигнала при неравенстве проверяемой информации хотя бы в одном из каналов 8 мажоритарно-ре- зервироваНных группу каналов 8. Вьфа ботка элементом ИЛИ 4 сигналов в ос- тальные моменты времени не влияет на работу устройства. При отказе соответствующих каналов 8 или, если канал 8 находится в резерве, сигналы с выходов 29 соответствующих блоков 7 на входы элемента ИЛИ 4 не подаются.

Элемент ИЛИ 5 предназначен для выработки на выходе 20 в заданные моменты времени сигнала соответствующе го логического условия, если все группы мажоритарно-резервированных каналов 8 укомплектованы исправными каналами 8. Выработка элементом ИЛИ 5

сигналов р остальные моменты времени не влияет на работу устройства При отказе соответствующего канала 8 или нахождении его в резерве сигналы с выходов 30 соответствующих блоков 7 анализа и реконфигурации на входы элемента ИЛИ 5 не подаются.

Блок 7 анализа и реконфигурации (фиг.1 и 2) предназначен для обнаружения отказов каналов 8 мажоритарно- резервированных групп каналов 8; для блокировки кодов команд внешних устройств процессорных элементов 37 при отказе соответствующего канала 8 или нахождении его в резерве для выработки сигналов, определяющих формирование устройством сигналов логических условий при отсутствии резервных каналов и наличии отказавших каналов, при появлении в мажоритарно-резервированных каналах группах каналов 8 отказавших каналов 8 и при неукомплектованных мажоритарно-резервированных группах каналов 8 исправными каналами 8; для упр авления приемом информации и для задания режима обмена канала 8.

В блоке 7 (фиг.2) счетчик 39 кодов настройки предназначен для приема и хранения кода номера соответствующего канала 8 при начальной настройке групп мажоритарно-резервированных каналов 8; для уменьшения на единицу своего содержимого при очередной итерации реконфигурации обменника 6 информации, если в группах каналов 8 обнаружены отказы, причем канал 8 с нулевым номером является исправным;- для обнаружения своего содержимого (формирования нулевого кода номера канала 8) в первой итерации реконфигурации обменника 6, если исправным каналом является канал 8 с наименьшим номером, отличным от нуля.

Изменение содержимого счетчика 39 происходит по заднему фронту синхросигнала на входе 16.4, причем при единичном состоянии сигнала на входе 16.2 в счетчик 39 записывается код, подаваемый на группу его информационных входов. При нулевом сигнале на входе 16.2 счетчик 39 обнуляется, если подается сигнал на вход сброса, уменьшает свое содержимое на единицу, если подается сигнал на его вычитающий вход, или остается без изменения при отсутствии сигналов на линиях 71 и 72.

Сумматор 40 кодов настройки предназначен для определения отказавшего канала 8 группы мажоритарно-резервированных каналов 8 с целью замены его исправным каналом 8 путем присвоения исправному каналу 8 номера отказавшего канала 8. Присвоение исправному каналу 8 номера отказавшего канала 8 производится как описано путем обнуления счетчика 39 или уменьшения его содержимого на единицу. Для этого код номера соседнего исправного канала 8 с меньшим номером подается на группу А входов сумматора 40 кодов настройки, увеличивается на единицу подачей сигнала на вход -f 1 сумматора 40 и сравнивается с- содержимым счетчика 39 на блоке 42. Если код на выходе сумматора 40 равен содержимому счетчика .39 (единичный сигнал на выходе 73 () блока 42), то соседний канал 8 с меньшим номером исправен и содержимое счетчика 39 не изменяется, что означает согласованность ном ров соседних каналов. Если содержиг мое счетчика 39 больше кода на выходе сумматора 40 (единичный сигнал на выходе 72 (А В) блока 42), то для согласования номером каналов 8 рабочей конфигурации систем производится уменьшение содержимого счетчика 39 на единицу. Если содержиДешифратор 46 конфигурации кана

мое счетчика 39 меньше кода на выхо, г, / ч. а предназначен для дешифрации кодов, де сумматора 40 (единичный сигнал на 35 „„„„„ „ „„„.„ о ,

выходе 71 (А В) блока 42), то, если соседний канал 8 с меньшим номером равен нулю, исправен, для его замены данным соседним каналом 8

хранимых в счетчике 39. Каждому ко ду на входе дешифратора 46 соответ ствует выработка сигнала на одном из его выходов. Все выходы дешифра 40 тора 46 разделены на три группы вы дов. В группу выходов 80 старших но ров групп каналов собраны выходы, соответствующие кодам номеров, рав

производится обнуление счетчика 39. При исправном канапе 8 с нулевым номером подтверждается нулевое состояние его счетчика 39.

хранимых в счетчике 39. Каждому коду на входе дешифратора 46 соответствует выработка сигнала на одном из его выходов. Все выходы дешифра- 40 тора 46 разделены на три группы вых дов. В группу выходов 80 старших ном ров групп каналов собраны выходы, соответствующие кодам номеров, равным 2,5,8(ЗК-1),... при мажоБлок 41 сравнения предназначен для 45 Ритировании по два из трех, или, сравнения информации процессорного например,4,9,14,(5К-1),... при ма- элемента 37 данного канала 8 с аналогичной информацией соседнего процессорного элемента 37, записанной в информационный регистр 85 данного канала 8, информация которых сравнивается. В случае исправности сигнал на выходе 75 равенства кодов

жоритировании rio три из пяти ,

где К« 1,2,3В группу выходов

младших номеров групп каналов собра

ны выходы, соответствующие кодам номеров, равным 0,3,6, ...,3(К-1),,. при мажоритировании по два из трех или 0,5,10, ...,5(.К-1),... при мажоритировании по три из пяти. В гру

() блока 41 обеспечивает отсутствие сигналов на выходе 29 блока 7 и соответствующем входе элемента ИЛИ А. Отсутствие сигнала на выходе 76 неравенства кодов (А/В) блока 41 обеспечивает запись нулевого кода в триггер 47 или 48 при подаче импульсов на их синхровходы.

Блок 43 сравнения предназначен для определения того, является

соответствующий канал 8 резервным или рабочим в одной из групп мажоритарно-резервированных каналов. Самый старший канал 8 из групп мажоритарно-резервированных каналов 8

(меньший на единицу от самого младшего номера из резервных каналов 8) заносится в регистр 44 информационных входов 23 при выработке синхросигнала на выходе 16.5. Если канал 8

является резервным, то содержимое счетчика 39 больше содержимого регистра 44, поэтому единичный сигнал вырабатывается на выходе 79 (А В) блока 43. Если канал 8 является рабочим каналом одной из групп мажоритарно-резервированных каналов 8, то содержимое счетчика 39 меньше или равно содержимому регистра 44 и сигнал вьфабатывается на первом 77

(А В) или втором 78 (А с:В) выходе блока 43.

Коммутатор 45 информации предназначен для передачи на группу информационных выходов 26 информации

с выходов счетчика 39 или с группы информационных входов 23 под управлением сигналов с входа 16.1.

Дешифратор 46 конфигурации канала

предназначен для дешифрации кодов, „„„„„ „ „„„.„ о ,

хранимых в счетчике 39. Каждому коду на входе дешифратора 46 соответствует выработка сигнала на одном из его выходов. Все выходы дешифра- тора 46 разделены на три группы выходов. В группу выходов 80 старших номеров групп каналов собраны выходы, соответствующие кодам номеров, равРитировании по два из трех, или, например,4,9,14,(5К-1),... при ма-

жоритировании rio три из пяти ,

где К« 1,2,3В группу выходов 81

младших номеров групп каналов собраны выходы, соответствующие кодам номеров, равным 0,3,6, ...,3(К-1),,.. при мажоритировании по два из трех или 0,5,10, ...,5(.К-1),... при мажоритировании по три из пяти. В группу выходов 82 средних номеров групп каналов собраны выходы, соответствующие кодам номеров, равным 1,4,7,,..,ЗК-1,... при мажоритировании по два из трех или 1,2,3;

713222998

6,7,8; 11,12,П;... (5К-4), (5К-3), ляется в момент подачи синхросигнала н а (5К-2);... при мажоритировании по вход 16.8, если только оба тригге- три из пяти. Аналогичным образом Ра 47 и 48 - в единичном состоянии,

группируются выходы деигифратора 46

что происходит, когда информация

Ю

при отличных других модулях мажорити- 5 Данного канала 8 не сравнилась с рования.

Триггер 47(48) сравнения кодов предназначен для записи и хранения результатов сравнения информации блоком 41. При сравнении инофрмации процессорного элемента 37 данного канала 8 с информацией процессорного элемента 37 соседнего канала с меньшим (большим) номером результат сравнения с выхода 76 () блоком 41 записывается в триггер 47(48), причем меньшим (большим) номером для канала 8 с номером 3(1-1) (31-1) является канал 8 с номером (31-1) 3(1-1), образуя малое кольцо, в которое объединяются каналы 8 каждой группы мажоритарно-резервированных каналов 8. Запись информации с выхода 76 блока 41 в триггер 47(48) происходит в момент выработки сигнала на выходе элемента И 55(56),а обнуление триггеров 47 и 48 происходит при подаче сигнала на вход 16.9.

информацией обоих соседних каналов 8 как с меньшим, так и с большим номером относительно номера данного канала. Таким образом, включение обоих триггеров 47 и 48 сигнализирует об отказе данного канала 8 или соот- ветствуюшего ему процессорного элемента 37. Обнуление триггера 49 канала происходит одновременно с обнуJ5 лением триггеров 47 и 48.

Блок 50 элементов И предназначен для передачи кодов с кодовых входов 17 на кодовые выходы 24,если дан-, ный канал 8 не является резервным

20 (единичный сигнал с выхода 77 или с выхода 78 через элемент ИЛИ 65 подается на вход элемента И 57) и данный канал 8 не отказал (единичный сигнал с нулевого выхода 84 триг25 гера 49 подается на вход элемента Ц 57).

Элементы ИЛИ 51-53 предназначены для объединения соответствующих одноименных группы выходов 80-82 дешифТриггер 49 блокировки канала пред- Ратора 46 и указания (путем выра- назначен для блокировки приема ин- сигнала на выходе одного из

ос Q „„ элементов ИЛИ 51-53 )какой номер fl формации в регистр 85 канала 8, для/

блокировки передач информации с вы- группе мажоритарно-резервированных ходом этого регистра 85 на первую 32 каналов присвоен данному каналу - и вторую 35 группы информационных вы- 35 старший, младший или средний (сред- ходов канала В (обеспечивается пода- е) соответственно. чей сигнала с выхода 83 триггера 49 Элемент И-ИЛИ 54 предназначен через элемент ШШ-И 54 на входы эле- блокировки канала 8 (блокировки ментов 61,62 ИЛИ-НЕ после чего на записи информации в регистр 85 кана- выходах 27 и 31 удерживается нуле- 40 ла 8 и перерода мультиплексоров 86 вой потенциал), для блокировки выра- и 87 в режим передачи информации ин- ботки сигналов на выходах 29 и 30 формационных входов 33 на группу элементов ИЛИ-НЕ 63 и 64 (обеспечива- информационных выходов 35 и с ин- ется подачей сигнала с выхода 83 на формационных входов 34 на группу входы элементов ИЛИ-НЕ 63 и 64J, для 45 информационных выходов 32 канала 8)

подачей сигнала на входы элементов I ИЛИ-НЕ 61 и 62 и блокировки сигналов на выходах элементов И 55 и 56. Эти блокировки происходят после включения

блокировки передачи кодов через блок 50 элементов И с кодовых входов 17 на кодовые выходы 24 устройства (обеспечивается снятием сигнала с выхода элемента И 57 при снятии сигна- 0 триггера 49 или при замыкании мало- ла на выходе 84 триггера 49 после его включения) и для выработки сигнала на выходе 28 элемента ИЛИ 66 после включения триггера 49. При нуго кольца .

Группа мажоритарно-резервированных каналов 8 устройства образует малое

левом состоянии триггера 49 перечис- кольцо, в котором должна производитьленные блокировки не происходят и сое-ся передача информации для межканаль

тояние выхода 28 элемента ИЛИ 66 опре-ного сравнения так, что при передаче

деляется только состоянием выхода 77информации между каналами 8 мажоблока 43.Включение триггера 49 осуществ-ритарно-реэервированной группы в

что происходит, когда информация

Данного канала 8 не сравнилась с

информацией обоих соседних каналов 8 как с меньшим, так и с большим номером относительно номера данного канала. Таким образом, включение обоих триггеров 47 и 48 сигнализирует об отказе данного канала 8 или соот- ветствуюшего ему процессорного элемента 37. Обнуление триггера 49 канала происходит одновременно с обнулением триггеров 47 и 48.

Блок 50 элементов И предназначен для передачи кодов с кодовых входов 17 на кодовые выходы 24,если дан-, ный канал 8 не является резервным

(единичный сигнал с выхода 77 или с выхода 78 через элемент ИЛИ 65 подается на вход элемента И 57) и данный канал 8 не отказал (единичный сигнал с нулевого выхода 84 триггера 49 подается на вход элемента Ц 57).

Элементы ИЛИ 51-53 предназначены для объединения соответствующих одноименных группы выходов 80-82 дешифтриггера 49 или при замыкании мало-

го кольца .

Группа мажоритарно-резервированных каналов 8 устройства образует малое

сторону старших номеров информация канала 8 со старшим номером в группе должна попасть в канал 8 группа с младшим номером и, наоборот, пр передаче информации между каналами 8 мажоритарно-резервированной группы в сторону младших номеров. Признаком замыкания малого кольца является подача сигнала на вход 16.3.

.Таким образом, замыкание малого кольца после передачи информации между всеми каналами 8 устройства в сторону младших (средних/старших) номеров производится передачей информации между каналами 8 устрой- ства в сторону старших (младших)номеров и вьфаботкой сигнала на входе 16.3. Тогда при замыкании малого кольца и передаче информации в сторону старших (младших) номеров каналов 8 заблокирована запись в регистры 85 каналов 8, имеющих средние и младшие (старшие) номера, и разрешена трансляция информации через эти каналы с групп информационных входов 38 и 34 на группы выходов 35 и 32, а через каналы 8, имеющие старшие (младшие) номера, блокиру т- ся трансляция информации с входов 33 и 34 на выходы 35 и 32 (инфор- мация на выходы 35 и 32 зтих каналов 8 подается с выходов их регистров 85) и разрешена запись в регистры 85 этих каналов 8. В резервных

каналах 8 в данном случае на их груп- 35 регистра 2. А при нулевом (единичном)

пы выходов 32 и 35 передается информация с выходов регистров 85 и разрешена запись информации в эти регистры. Поэтому при замыкании малого кольца и передаче информации в сторону старших (младших) номеров каналов 8 в канал 8 со старшим номером самой младшей группы (с младшим номером самой старшей группы) записана информация с резервного канала 8 с самым старшим номером (с самым младшим номером канала 8 в группе резервных каналов).

Элемент И 55(56) предназначен для подачи на синхровход триггера 47(48) сигнала с выхода 16.6(16,7). Выработка синхросигналов на выходах элементов И 55 и 56 при подаче сигналов на их входы 16,6 и 16.7 запрещается в двух случаях: если отказал соот- ветствую1ций канал 8 или процессорный элемент 37, то сигнала с выхода 83 триггера 49, пройдя через элемент

5

0

5

И-ИЛИ 54 запрещает срабатывание элементов И 55 и 56 (выработка сигнала на выходе элемента И-ИЛИ 54 во время замыкания малого кольца не влияет на работу элементов И 55 и 56, так как сигналы на входах 16.3, 16.6 и 16.7 не совместны во времени), и, если соответствующий канал 8 является резервным, тогда сигнал с выхода 79 блока 43 блокирует срабатывание элементов И 55 и 56.

Элемент ИЛИ-НЕ 61 управления приемом информации предназначен для разрешения записи в регистр 65 информации при наличии сигнала или запрета при отсутствии сигнала на выходе элемента ИЛИ-НЕ 61. Поскольку устройство может работать в нерезервированном режиме аналогично работе известного устройства, и в мажоритарно-резервированном с возможностью замены отказавших каналов 8 резервирования, то выработкой сигналов на выходе элемента ИЛИ-НЕ 61 управляют два источника - регистр 2 маски и элемент И-ИЛИ 54. В нерезервированном режиме работы устройства триггер 49 находится в нулевом состоянии и на входы 16.3 сигналы не подаются, поэтому сигнал на выходе элемента И-ИЛИ 54 отсутствует, а значение сигнала на выходе элемента ИЛИ-НЕ 61 определяется значением сигнала на соответствующем выходе 21

0

значении соответствующего выхода 21 единичный (нулевой) сигнал на выходе 27 элемента ИЛИ-НЕ 61 разрешает (запрещает) запись информации в регистр 85 канала 8. В мажоритарно- резервированном режиме работы устройства регистр 2 обнулен и разрешение (запрет) записи информации в регистр 85 канала 8 производится нуле- вым (единичным) сигналом на выходе

элемента И-ИЛИ 54, I

Элемент ИЛИ-НЕ 62 задания режима

обмена предназначен для управления л источниками информации передаваемой на выходы 35 и 32 мультиплексоров 86 и 87 канала 8. При единичном сигнале на выходе 31 элемента ИПИ-НЕ62 информация на выходы 35 и 32 мульти- 5 плексоров 86 и 87 подается с выходов регистра 85, а при нулевом - с входов 33 и 34 канала 8 соответственно.

Элемент ИЛИ-НЕ 63 предназначен для сигнализации о наличии отказавшего канала 8 в момент сравнения информации соседних каналов 8 в блоке сравнения. Моменты данного сравнения информации соответствуют моментам проверки мультиплексорам 93 логичес- ких условий состояния сигнала на выходе 19 элемента ИЛИ 4, управляемого сигналами с выходов 29. В остальные моменты времени информация на выходе 29 элемента ИЛИ-НЕ 63 может быть произвольной. При отказе канала 8 (включен триггер 49) или, если канал 8 является резервным (единичный сигнал на выходе 79 блока 43), на выходе 29 элемента ИЛИ-НЕ 63 сигнал отсутствует независимо от состояния сигнала на выходе 75 блока 41. В противном случае при сравнении кодов (единичньй сигнал на выходе 75) на выходе 29 эле- мента ИЛИ-НЕ 63 сигнал отсутствует, а при несравнении кодов (сигнал на выходе 75 отсутствует) на выходе

29и соответственно на выходе 19 вырабатывается сигнал.

Элемент ИЛИ-НЕ 64 признака окончания реконфигурации предназначен для выработки сигнала на выходах

30и 20, если какая-либо из групп мажоритарно-резервированных каналов неукомплектована полностью исправными каналами 8. Сигнал на выходе 30 несет смысловую нагрузку только в моменты времени, когда мультиплексором 93 осуществляется проверка сигнала соответствующего логического условия на выходе 20 элемента

ИЛИ 5. При отказе соответствующего канала 8 сигнал на выходе 83 триггера 49 запрещает вьфаботку сигналов на выходе 30. При наличии отказавщих каналов В в какой-либо из групп мажоритарно-резервированных каналов в соответствующий момент времени на выходе 72 блока 42 вьфабатывается си нал, а на его выхода х 71 и 73 сигналы отсутствуют, поэтому в данный момент времени на выходах 30 и 20 вырабатываются сигналы, что соответствует неукомплектованности групп неправ ными каналами 8. Если же в соответствующий момент времени на выходе 71 (А В) или 73 () вырабатывается сигнал, то на выходе 30 в данный момент времени сигнал от-

сутствует. I

Элемент ИЛИ 65 анализа резерва

предназначен для выработки сигнала.

если соответствующий канал 8 является одним из группы мажоритарно-резервированных каналов. Если же данный канал 8 является резервным, то отсутствие сигнала на выходе элемента ИЛИ 65 блокирует срабатывание элементов И 58 и 60 и через элемент И 57 запрещает передачу кодов через блок 50.

Элемент ИЛИ 66 анализа резерва предназначен для вьфаботки сигнала на вьгходе 28 блоков 7, если произоше отказ соответствующего канала 8 (единичный сигнал на выходе 83 триггера 49), либо при условии, что данный канал 8 является не резервным и его номер меньше самого старшего номера канала 8 из числа каналов 8, формирующих группы мажоритарно-резервированных каналов (данный номер хранится в регистре 44). Ситуация, при которой вьфабатываются сигналы на выходах 28 всех блоков 7 и соответственно на выходе 18 элемента И 3, говорит о том, что весь резерв каналов 8 исчерпан и существует группа (группы) мажоритарно-резервированных каналов не укомплектованных полностью исправными каналами 8. I

Элемент НЕ 67 предназначен для вьфаботки сигнала на своем выходе при передаче информации между каналами 8 в направлении младших номеров каналов 8. Необходимо дополнительно подчеркнуть J. что упоминаемая в тексте нумерация каналов 8 задается в счетчиках 39 номерами от нуля до значения, равного (М-1), причем в исходном состоянии в счетчик 39, соответствующий каналу 8 с индексом М (фиг.1), заносится нулевой код. Нумерация каналов 8 кодами в соответствующих счетчиках 39 возрастает от нуля до (М-1) для ка- йалов 8,имеющих (фиг. 1) индексы М, ... 2,1 соответственно.Поэтому в исходном состоянии в счетчик 39 блока 7.1 заносится код M-l,блока 7.2-код М-2 и так далее, а блока 7.М - код О. Данная нумерация иллюстрируется позицией (фиг.5), где в квадратах приведена нумерация каналов 8 (обозначение 39 следует понимать как содержимое счетчика 39), когда число каналов 8 в обменнике 6 информации равно девяти. Из этих девяти каналов 8 образованы две группы мажори13

тарно-реэервированных каналов с номипп ноч ,, ii-jii л t

рами О , 1 , i и J , ч , i и группа резервных каналов 8 с номеII/- г 11-711 ,, II Q II

рами о , / и а .

Каналы 8 и их работа абсолютно идентична каналам известного устройства и осуществляется следующим образом.

При наличии сигнала на входе 31 осуществляется передача информации на входы 35 и 32 канала 8с выходов регистра 85, а при отсутствии сигнала - с входов 33, 3 i канала 8 соответственно. При наличии (отсутствии) сигнала на входе 11 на перву группу А информационных входов регира 85 информация передается с группы информационных входов 33 и 34. Запись информации в регистр 85 проиходит по заднему фронту синхросигна ла, поступающего на вход 9, если на его вход 27 подается сигнал. В зависимости от состояния сигнала на входе 10 запись информации в регистр 8 производится либо с выходов мультиплексора 88, либо с информационных входов 26.

Функционирование устройства 38 происходит следующим образом под управлением разнесенных во времени неперекрывающихся синхросигналов и на входах 114 и 115. В ко41це выполнения очередной микропрограммы на выходе 104 конца команды регистра 90 подается сигнал, обеспечивающий занесение в регистр 91 начального адреса очередной микропрограммы с входов 98. Все последуюпще адреса микрокоманд микропрограммы заносятся в регистр 91 с выходов 101 (сигнал на выходе 104 отсутствует), причем если мультиплексором 93 логических условий не производится проверка логических условий на выходах 18-20 устройства, то модифицируемый разряд очередного адреса микрокоманды передается на выход 103 мультиплексора 93 (и соответствующий вход реНа вход 10 подается потенциал.

гистра 91) без изменения под управле- сп устанавливающий регистры 85 в режим

50

ния соответствующего кода на выходе 100. При проверках мультиплексором 93 соответствующих логических условий на . выходах 18-20 устройства под управлением соответствующего кода на выходах 100 значение модифицированного разряда адреса очередной микрокоманды на выходе 103 мультиплексора 93 определяется значением

99

14

сигнала на выходе 18, 19 или 20. Таким образом, осуществляется ветвление в микропрограмме и перевод на соответствующую ее ветвь. Запись адреса очередной микрокоманды в регистр 91 производится по заднему фронту сигнала на входе 114, а запись операционной части микрокоманды в регистр 90 с выходов 99 происходит по заднему фронту сигнала на входе 115. Микрооперации, запоминаемые в регистре 90, управляют подачей сигналов на соответствующие входы 9-17 устройства, причем для формирования импульс

ных сигналов на соответствукяцих входах устройства используются злементы И 95-97 и дешифратор 94, тактируемые синхросигналом с входа 114.

Устройство работает в двух режи- мах; нерезервированном (аналогично работе известного устройства) и мажоритарно-резервированном с подключением резервных каналов 8 взамен отказавших каналов 8, Под отказом канала 8 следует понимать как отказ отдельных узлов канала 8 (регистра 85, мультиплексора 88 и мультиплексоров 86 и 87 по передаче информации с выходов регистра 85 на выходы 35 и 32 канала 8) так и отказ подключаемых к устройству процессорных элементов 37.

В нерезервированном режиме устройство работает следующим образом.

Счетчик 39, регистр 44 и триггеры 47-49 находятся в нулевом состоянии, сигналы на входы 16 не подаются и логические условия на выходах 18-20 устройства не проверяются, поэтому состояние сигналов на входах 27 и 31 определяется кодами регистров 2 и 1. Информация с информационных входов 23 передается через коммута- торы 45 на информационные входы 26 каналов 8, а коды с входов 17 передаются на кодовые выходы 24 устройства.

На вход 10 подается потенциал.

устанавливающий регистры 85 в режим

устанавливающий регистры 85 в режим

записи информации по входам 26, и

производится запись информации из процессорных элементов 37. Затем на вход 10 подается потенциал, устанав- ивающий регистры 85 в режим приема информации с выходов мультиплексора 88.

Элементарный цикл работы устройства состоит в следующем.

151322299

На вход 11 подается потенциал, соответствующий выбранного направлению

ег

пересыпки информации в обменнике 6. По входам 12-15 производится запись управляющей информации в регистры 1 и 2. После этого на вход 9 подается синхросигнал, обеспечивающий запись информации в регистры 85 с выходов мультиплексоров 88.

При этом запись новой информации происходит в каналах 8, указанных отсутствием единиц в соответствующих разрядах регистра 2 маски, записываемая информация поступает из ближайшего по выбранному направлению пе ресьлки канала 8, указанного регистром 1 состояний.

При работе устройства пауза между двумя смежными синхросигналами на вхо де 9 должна гарантировать правильную работу устройства. Поэтому величина паузы определяется временем распространения фронта сигнала с выхода регистра 85 первого канала 8 до входа регистра 85 последнего канала 8 при передаче информации через мультиплексоры 87 или с выхода регистра 85 последнего канала 8 до входа регистра 85 первого канала 8 при передаче информации через мультиплексоры 86 и должна быть больше этого времени.

Если тpeбye вJй обмен информацией между каналами 8 не удается провести за один элементарный цикл, на регистры 1 и 2 заносится новая информация и производится следующий элементарный цикл обмена информацией

При использовании устройства в многопроцессорной вычислительной системе при необходимости осуществления обмена между процессорными элементами 37 устройство 38 инициирует запись информации в обменник 6 выдачей сигналов по входам 9-15. Затем, в соответствии с программой обмена, устройство 38 организует несколько элементарных циклов обмена информацией между каналами 8, управляя перегрузкой регистров 1 и 2.

После завершения программы обмена устройство 38 инициирует перепись информации t из каналов 8 в

соответствующие им процессорные эле- 55 входе 10 каналов 8 разрешает прием

менты 37.

В мажоритарно-резервированном режиме устройство работает следуюощм образом.

информации в регистр 85 с выходов мультиплексора 88. Таким образом, и форма1шя канала с номером 5 пает в резервный канал с

посту номером 6

9

16

В начале.работы устройства все его элементы и узлы, также как

10

15

25

-20 30

и процессорные элементы 37, к которым подключается устройство, исправ- 5 ны, а триггеры 47-49 обнулены. Работа устройства начинается с формирования групп мажоритарно-резервированных каналов и резервных каналов. А в процессорных элементах 37 хранятся их физические номера, которые через информационные входы 23 подаются на информационные входы счетчиков 39 и записываются в них по синхросигналам на входе 16.4 и подаче потенциала на вход 16.2(позицияа фиг.5). Код самого старшего номера канала 8 из групп мажоритарно-резервированных каналов 8 (для примера, приведенного на фиг.5, этот код равен 5) аналогичным образом из процессорного элемента 37 подается на входы регистра 44 и записывается в него при подаче синхросигнала на вход 16.5 устройства.

При дальнейшей работе до определения отказавших каналов 8, если они

есть, и перестройки структуры устройства сигналы на входы 16 не подаются, и устройство функционирует аналогично описанному нерезервированному режиму с той лишь разницей, что в резервных каналах 8 управляющие коды с входов 17 на группы выходов 24 не передаются. При этом функционирование резервных каналов 8 происходит обычным образом, соответствующим остальным каналам. I

Проверка исправности каналов 8 может производитьсяJнапример, периодически через заданные интервалы времени и происходит следующим образом.

Регистры 1 и 2 обнулены. Контрольные коды с процессорных элементов 37 записываются в регистры 85 соответствующих каналов 8.Затем производится элементарный цикл передачи информации из регистров 85 каналов 8 в регистры 85 соседних каналов 8, имею- щих номер на единицу больший. Управение передачей производится путем выработки потенциалов на входах 11j27 и 31 и синхросигнала на вхое 9 каналов 8. При этом сигнал на

входе 10 каналов 8 разрешает прием

информации в регистр 85 с выходов мультиплексора 88. Таким образом, ин- форма1шя канала с номером 5 пает в резервный канал с

посту- номером 6,

17

а в канал с номером О поступает информация из резервного канала с номером 8, не несущая смысловой нагрузки. В следующем элементарном цикле производится передача информации между каналами 8 в сторону младших номеров и производится замыкание малого кольца подачей сигнала на вход 16.3. В этом цикле каналы 8 с номерами 1, 2, А и 5 работают на передачу, информации с входов 34 на выходы 32 и не изменяют состояния регистров 85. В регистр 85 канала 8 с номером О поступает информация канала 8, имеющего номер 3, а в канал 8 с номеромканала с номером

llQtl

lep

3 - информация из резервного

6. Таким образом,

после данных двух злементарньк циклов обмена смещение информации в кана- лах 8 произошло следующим образом: , , ,

tiTii л и

В следующем (третьем) элементарном цикле в блоке 41 сравнивается код соседнего канала, подаваемый по входам 25 из регистра 85 с аналогичным кодом, подаваемым на информационные входы 23 устройства с выхода своего процессорного элемента 37. На вход 16.6 подается сигнал, который поступает на синхровход триггера 47 через элемент И 55, если он не заблокирован, как описано. При равенстве сравнивае

мых кодов (низкий сигнал на выходе 76 35 соответствующих сигналов на входах блока 41 сравнения) в триггере 47 9-11 и 16.1 и выходах 27 и 31 эле- подтверждается нулевое состояние, а ментов ИЛИ-НЕ 61 и 62 производится при неравенстве - в триггер 47 запи- запись содержимого счетчика 39 в ре- сана единица, причем триггер 47 уста- гистр 85 соответствующего канала 8, навливается в единицу в блоке 7 отка- 40 после чего в следующем элементарном завшегося канала (фиг.5, канал с но- блоком 42 производится сравнение содержимого своего счетчика 39 с увеличенным на единицу на сумматоре 40 содержимым счетчика 39 соседнемером ,1) и одного из соседних исправных каналов (фиг.5, канал с номером 2) ,

Затем производится йьшолнение трех элементарных циклов аналогично описанному с той лишь разницей, что в первом элементарном цикле информация между каналами передается в сторону каналов 8 с младшими номерами, во втором элементарном цикле при замыкании малого кольца - в сторону каналов со старшими номерами, а в третьем элементарном цикле синхросигнал вырабатывается нд входе 16,7, а не на входе 16.6. Поэтому информация между каналами перемещается следующим

образом: 2

1I .

и

322299

О llQtl

18

и / (I

- 4 .

4 --«.з

и

20

, ), а триггеры 48 для примера (фиг,5) устанавливаются в единицу в каналах с номерами 1 и О. Та5 КИМ образом, оба триггера 47 и 48 включаются только в блоке 7 соответствующего отказавшему каналу (в нашем примере - каналу 8 с номером 1).

)0 Поскольку при сравнении кодов на выходе 75 блока 41 сравнения, например в канале с номером 1, сигнал отсутствует, то на выходе 29 и соответственно на выходе 19 вьфабатыва15 ется сигнал 1,который определяет переход микропрограммы микропрограммного запоминающего устройства 89 на соответствующую ветвь, работа по которой производится как описано. Если же отказавшие каналы отсутству- .ют, то переход микропрограммы производится на ветвь, соответствующую окончанию реконфигурации устройства. При наличии отказавших каналов бота устройства происходит следующим образом.

В следующем цикле на вход 16,8 подается синхросигнал, по которому 30 включается триггер 49 только в том из блоков 7, в котором включены оба триггера 47 и 48 (соответствующего отказавшему каналу 8 с номером 1). В следующем цикле под управлением

35 соответствующих сигналов на входах 9-11 и 16.1 и выходах 27 и 31 эле- ментов ИЛИ-НЕ 61 и 62 производится запись содержимого счетчика 39 в ре- гистр 85 соответствующего канала 8, 40 после чего в следующем элементарном блоком 42 производится сравнение содержимого своего счетчика 39 с увеличенным на единицу на сумматоре 40 содержимым счетчика 39 соседне 5 го канала 8, записанным в регистре 85 своего канала. В этом же элементарном цикле производится обнуление своего счетчика 39 или уменьшение его содержимого на единицу,или содер50 жимое счетчика 39 остается без изменения в зависимости от того, на каком из выходов 71-73 блока 42 вьфа- ботан сигнал (фиг.5в, поясняется соответствующими цифрами справа от квад55 ратов и стрелкой перехода в соответствующее состояние счетчика 39, пояснение приводится под обозначе- ння 42 состояния выходов блока 42 сравнения).

19

R этом же элементарном lyiKJie про- врряется состояние логнческог о уровня на выходе 20 элемента ПНИ 5. Поскольку включенный триггер 49 блока 7 канала 8 с номером 1 запрещает пе- редачу содержимого регистра 85 на его выходы (канал 8 с номером 1 настраивается на передачу информации с входов 33 и 34 на выходы 35 и 32), то в канале 8 с номером 2 в регистр 85 записан код О, соответствующий содержимому счетчика 39 с номером О. В этом случае в блоке 7, соответствующем каналу 8 с номером 2, сигнал вырабатывается на выходе 72 блока 42 и по синхросигналу на входе 16.4 содержимое счетчика 39 уменьшается на единицу. Отсутствие сигналов на выходах 71 и 73 блока 42 в данном цикле опреде- ляет выработку сигнала на выходе 30 элемента ИЛИ-НЕ 64 и соответственно на выходе 20 элемента ИЛИ 5, что при проверке данного логического условия сигнализирует о том, что дан- ,ная итерация (например, итерагщя ь фиг.5) не является последней, так как не завершено формирование групп мажоритарно-резервированных каналов путем замены неисправных каналов 8 исправными из числа резервных.

Описанная итерация обмена содержимым счетчиков 39 между каналами, анализа их содержимого и модификации содержимого счетчиков 39 повторяет- ся до тех пор, пока на выходе 20 элемента ИЛИ 5 в соответствунщий момент времени отсутствует сигнал. Это означает, что сформированы группы Ме1жоритарно-резервированных каналов, укомплектованные исправными каналами 8, и нумерация каналов 8 этих групп и резервных кангшов 8 осуществляется без пропуска последовательных номеров. Повторение итераций показа- но обозначениями bj (фиг.5).

По окончании итераций реконфигурации каналов 8 обменника 6 (после итерации Ь«) происходит проверка на- личия групп мажоритарно-резервированных каналов, не полностью укомплектованных исправными каналами. Данная ситуация возникает, если на выходах 2

всех блоков 7 и соответственно на выходе 18 вырабатьшается единичный сигнал. В примере (фиг.5) отсутствует сигнал на выходах 28 блока 7, соответствующего каналам 8 с вновь

5 0 (5 0 -5 0

5 0 5

Q

5

29920

образованными номерами 5, 6 и 7. Поэтому сигнал отсутствует и на выходе 18 элемента И 3 и при проверке мультиплексором 93 соответствующего логического условия микропрограмма блока 89 переходит на ветвь, в которой осуществляется обнуление триггера 47(48) в канале с номером 2(0). Поскольку при выработке сигнала на входе 16.9 обнуляются все триггеры 47-49 во всех блоках 7, то обнуление триггера 47(48) в канале с номером 2(0) производится сравнением контрольных кодов как но, так как группы мажоритарно-резервированных каналов укомплектованы исправными каналами 8, то при сравнении кодов и записи их результатов в триггеры 47 и 48 все триггеры 47 и 48 групп мажоритарно-резервированных каналов установлены в нулевое состояние.

На фиг.6 показан пример, когда после настройки обменника 6, приведенной на фиг.5, произошли отказы в ка- напах, идентифицированных кодами О и 5 в соответствующих счетчиках 39.

В данном случае контроль, обнаружение отказавших каналов и реконфигурация устройства производится аналогично описанному. Настройка обменника 6 и формирование групп мажоритар- но-ре§ервированных каналов, укомплектованных полностью исправными каналами, происходит за семь итераций , Состояния, которые принимают выходы счетчиков 39 и блоков 42 приведены под обозначениями 42. Выход из микропрограммы в данном случае производится аналогично описанному (как и в примере, показанном на фиг.5, поскольку низкий уровень сигнала на выходе 28 блока 7, соответствующего каналу 8 с вновь образованным, номером 5 обусловливает отсутствие сигнала на выходе 18 элемента И 3.

На фиг.7 показан пример, когда после настройки обменника 6, приведенной в примере, произошел отказ в идентифицированном номере 3 в соответствующем счетчике 39.

В данном случае контроль, обнаружение отказавшего канала 8 и реконфигурация устройства производится аналогично описанноьгу. Настройка обменника 6 и формирование групп мажоритарно-резервированных каналов заканСосчивается за три итерации , тояния, которые принимают выходы счетчиков 39 и блоков 42, приведены цифрами под обозначениями :39 Обозначением :5 О (фиг. 7) показано, что настройка обменника 6 окончена, так как на выходе элемента ИЛИ 5 в соответствующий момент времени присутствует нулевой сигнал. .После последнего элементарного цикла третьей итерации d, устройство переходит к циклу, обозначенному позицией е (фиг.7) в котором мультиплексором 93 проверяется логическое условие отсутствия резерва, т.е. состояния сигнала на выходе 18 элемента И 3 отсутствия резерва.

Поскольку наибольший номер исправного канала 8 равен четырем, т.е меньше величины 5, записанной в регистре 44 предела резерва, то на выходах 28 всех блоков 7 и соответственно на выходе 18 вьфабатывается единичньш сигнал (на фиг.7 данная ситуация отражена обозначением 3 1), указывающий на то, что существует мажоритарно-резервированная группа каналов, не укомплектованная исправными каналами 8. В этом случае работа устройства может быть остановлена либо исправные каналы 8 группы, не укомплектованной исправными каналами, переводятся в разряд резервных каналов 8 для остальных групп мажоритарно-резервированных каналов.

Формула изобретений

Устройство для обмена информацией, содержащее регистр состояний и регистр маски, информационные и синхронизирующие входы которых являются соответствую1цими входами устройства для подключения групп выходов кодов задания режима обмена и маски и тактирования регистров состояний и маски устройства управления вычислительным процессором системы, и М каналов, причем первые и вторые группы информационных входов i-ro канала (i-1,M) соединены соответственно с первой группой инфор 1ацион ных выходов (i-l)-ro канала и второй группой выходов ()-ro канала, первая группа информационных входов и вторая группа информационных выходов первого канала подключены соответственно к пepнo y информационному выходу и второму информационному входу АА -го канала, третья группа информационных выходов

i-ro канала является i-й группой выходов устройства для подключения i-ro процессорного элемента, вход синхронизации, вход задания направле- ния передачи и вход задания источника i-ro канала являются соответствующими входами устройства для подключения выходов синхронизации, задания направления передачи и задания источника устройства управления

вьтислительным процессором системы, причем каждый канал содержит информационный регистр и три мультиплексора, причем выходы первого, второго и третьего мультиплексоров соединены соответственно с второй и

первой группами информационных выходов канала и первой группой информационных входов информационного регистра, группа выходов которого

подключена к третьей группе информационных выходов канала и первым группам информационных входов первого и второго мультиплексоров, управляющие входы которых образуют вход

задания режима обмена канала, а вторые входы соответственно соединены с второй и первой группами информационных входов канала, управляющий вход третьего мультиплексора является входом задания направления передачи канала, а первая и вторая группы информационных входов соединены соответственно с первой и второй группами информационных входов

канала, вторая группа информационных входов, синхровход, вход разрешения записи и управляющий вход информационного регистра являются соответственно третьей группой информационных входов канала, синхровходом управления приемом и входом задания источника информации канала, отличающееся тем, что, с целью расширения класса решаемых задач устройства, путем обеспечения возможности анализа состояния и реконфигурации структуры устройства в мажоритарном режиме при отказе каналов, в него введены М блоков анализа

и реконфигурации, элемент И отсутствия резерва, элемент ИЛИ фиксации отказа и элемент ИЛИ фиксации на- стройки обменника, причем третьи группы информационных выходов и входов, вход задания режима обмена и вход управления приемом i-ro канала соединены соответственно с первой группой информационных входов, группой информационных выходов, выходом задания режима обмена и выходом управления приемом информации i-ro блока анализа и реконфигурации, маскирующий и системный входы которого подключены соответственно к i-M выходам регистра маски и регистра состояний, вход задания направления передачи информации, группы управляющих и кодовых входов блоков анализа и реконфигурации являются соответствующими входами устройства для подключения выхода задания направления передачи групп управляющих кодовых выходов устройства управления вычислительным процессом системы, первый, второй и третий управляющие выходы i-ro блока анализа и реконфигурации подключены соответственно к i-входам элемента И отсутствия резерва, элемента ИЛИ фиксации отказа и элемента ИЛИ фиксации настройки обменника, выход которых являются соответствующими выходами устройства для подключения входов отсутствия резерва, фиксации отказа и фиксации настройки обменника устройства управления вычислительным процессом системы, вторая группа информационных входов и группа кодовых выходов i-ro блока анализа и реконфигурации являются соответственно входом и выходом устройства для подключения группы информационных выходов и группы кодовых входов i-ro процессорного элемента, причем каждый блок анализа и реконфигурации включает счетчик кодов настройки, сумматор кодов настройки, три блока сравнения, регис предела резерва, коммутатор информации, дешифратор конфигурации канала, первый и второй триггеры сравнения кодов, триггер блокировки канала, блок элементов И, элементы ИЛИ старших, младпих и средних HON«epoB групп каналов, элемент И-ИЛИ, элементы И синхронизации, элемент И блокировки, элементы И старших, младших и средних номеров групп каналов элементы ИЛИ-НЕ управления приемом информации, задания режима обмена, признака неравенства информации и признака окончания реконфигурации.

5

0

5

0

5

0

5

0

5

первый и второй элементы ИЛИ анализа резерва и элемент НЕ, группа информационных входов сумматора кодов настройки подключена к первой группе информационных входов блока анализа и реконфигурации и первой группе информационных входов первого блока сравнения, вторая группа информационных входов блока анализа и реконфигурации соединена с группами информационных входов счетчика кодов настройки и регистра предела резерва, с первой группой инфсрмацион- ных входов коммутатора информации и с второй группой информационных входов первого блока сравнения, уп- равляюсций и синхронизирующий входы счетчика кодов настройки, синхровхо- ды регистра предела резерва и триггера блокировки канала, управляющий вход коммутатора информации, входы сброса первого и второго триггеров сравнения кодов и триггера блокировки канала, первый, второй и третий входы элемента И-ИЛИ и прямые входы элементов И синхронизации образуют группу управляющих входов блока анализа и реконфигурации, группа информационных входов и группа выходов блока элементов И являются соответственно группами кодовых входов и выходов блока анализа и реконфигурации, а управляющий вход блока элементов И соединен с выходом элемента И блокировки, маскирующий и системный входы блока анализа и реконфигурации соединены соответственно с первыми входами элементов ИЛИ-НЕ управления приемом информации и задания режима обмена, выходы которых образуют соответственно выходы управления приемом информации и задания режима обмена блока анализа и реконфигурации, вход задания направления передачи информации блока анализа и реконфигурации соединен непосредственно с четвертым входом и через элемент НЕ с пятым входом элемента И-ИЛИ, выход которого соединен с вторыми рходами элементов ИЛИ-НЕ управления приемом информации и задания режима обг мена и с первыми инверсными входами элементов И синхронизации, вход приращения единицы сумматора кодов настройки соединен с шиной единичного потенциала, группа выходов счетчика кодов настройки соединена с первыми группами информационных входов вто25

рого и третьего блоков сравнения, с входами дешифратора конфигурации канала и с второй группой информационных входов коммутатора информации, выходы которого образуют группу информационных выходов блока анализа и реконфигурации, группа выходов сумматора кодов настройки соединена с второй группой информационных входвв второго блока сравнения, первый выход которого соединен с втсодом установки в О счетчика кодов настройки и первым входом элемента ИЛИ-НЕ признака окончания реконфигурации, второй и третий выходы второго блока сравнения соединены соответственно с вычитающгим входом счетчика кодов настройки и с вторым входом элемента ИЛИ НЕ признака окончания реконфигурации, группа выходов регистра предела резерва соединена с второй группой информационных входов третьего блока сравнения, выходы равенства и неравенства кодов первого блока сравнения соединены соответственно с первым входом элемента ИЛИ-НЕ признака неравенства информации и с информационными входами первого и второго триггеров сравнения кодов, первый выход третьего бло- 30 ми элементов ШШ-НЕ признака неравенка сравнения соединен с первыми входами первого и второго элементов ИЛИ анализа резерва, второй вход третьего блока сравнения соединен с вторым входом первого элемента ИЛИ анализа резерва, выход которого соединен с первыми входами элементов И старших, младших и средних номеров групп каналов и с первым

2229926

входом элемента И блокировки, третий выход третьего блока сравнения соединен с вторым входом элемента ИЛИ-НЕ признака неравенства инфор5 мации и с вторым инверсным входом элементов И синхронизации, выходы которых соединены соответственно с синхровходами первого и второго триггеров сравнения кодов, выходы пер 0 вого и второго триггеров сравнения кодов соединены с первым и вторым информационными входами триггера блокировки канала, группы выходов старших, мпадших и средних номеров

5 групп каналов дешифратора конфигурации канала соединены соответственно с группами входов элементов ИЛИ старших, младших и средних номеров групп каналов, выходы которых соединены со20 ответственно с вторыми входами элементов И старших, мпадших и средних номеров групп каналов, выходы которых соединены соответственно с шестьм, седьмым и восьмым входами элемен25 та И-ИЛИ, единичный выход триггера блокировки канала соединен с девятым и десятым входами элемента И-ИЛИ, с вторым входом второго элемента ИЛИ анализа резерва и третьими входаства информации и признака окончания реконфигурации, выходы которых образуют соответственно первый, второй и третий управляющие выходы бло- 35 ка анализа и реконфигурации, нулевой выход триггера блокировки каналов соединен с вторым входом элемента И блокировки, выход которого соединен с управляющим входом блока элементов И.

т

ct

iilLJC

Jl

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

| Система для программного управления резервированными объектами и их диагностирования | 1989 |

|

SU1741295A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Резервированное устройство | 1980 |

|

SU928685A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Резервированное устройство | 1982 |

|

SU1102068A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении отказоустойчивых многопроцессорных вычислительных систем. Целью изобретения является расширение класса решаемых задач путем обеспечения возможности анализа состояния и реконфигурации структуры устройства в мажоритарном режиме при отказе каналов. Устройство содержит регистр состояний, регистр маски, элемент И отсутствия резерва, элемент ИЛИ фиксация отказа, элемент ИЛИ фиксации настройки обменника-информации, включающего М блоков анализа и реконфигурации и М объединенных в кольцо каналов. Каждый блок анализа и реконфигурации содержит счетчик кодов настройки, сумматор кодов настройки, первый, второй и третий блоки сравнения, регистр предела резерва, коммутатор информации, дешифратор конфигурации канала, первый и второй триггеры сравнения кодов, триггер блокировки канала, блок элементов И, элементы ИЛИ старших, младших и средних номеров групп каналов, элемент И-ИЛИ, элементы И синхронизации, элемент блокировки, элементы И старших, младших и средних номеров групп каналов, элементы ИЛИ-НЕ управления приемом информации, задания режима обмена, признака неравенства информации и признака окончания реконфигурации, первый и второй элементы ИЛИ анализа резерва, элемент НЕ и шину единичного потенциала. Новыми элементами в устройстве являются М блоков анализа и реконфигурации, элемент И отсутствия резерва, элемент ИЛИ фиксации отказа, элемент ИЛИ фиксации настройки обменника информации. 7 ил. (Л

MJL

91 US

|Ш HVX

Ш

90

fios

Щ

т

КШ

107

pyo i

109

109 110

fj A|

96 A

10

11 ttU /J /4U f5 . fr

Я6

W

I ffygp i т

т

113

97 A

is.t-t3

ДР

S.te.9

/e17

19

18

« I

И

tf

зв

| Быстродействующий коммутационный аппарат | 1980 |

|

SU943895A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена информацией | 1983 |

|

SU1118997A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-19—Подача