(54)

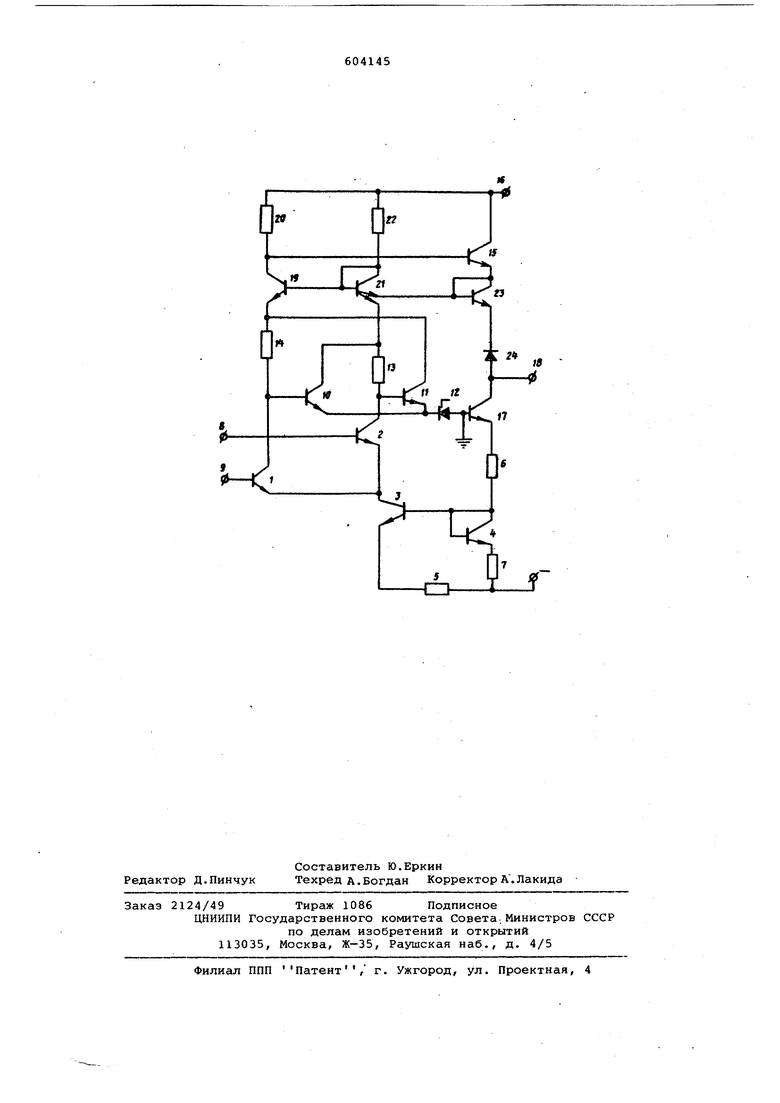

КОМПАРАТОР эмиттеры которых подсоединены к выходу генератора постоянного тока, выпол ненного на транзисторах 3,4 и реэис торах 5, 6,7. Базы транзисторов 1 и подключены к входным клеммам 8 и 9, а коллекторы подсоединены к базам s3:D.attaH.C.a;SEoj3 Ю к Ц промежуточного .каскада, эмиттеры которых объединены и через стабилитрон 12 подсоединены к общей шине,. Коллекторы транзисторов 10 и 11 через резисторы 13 и 14 соот.ветственно соединены с коллекторами транзисторов 1 и 2 дифференциального усилителя. Коллектор выходного транзистора 15 соединен с шиной 16 источ:ннка положительного Напряжения. База нагрузочного транзистора 17 соединена с общей ШИНОЙ, эмиттер соединен со вх дом генератора постоянного тока ( с резистором 6), а коллектор подсоединен к выходной клемме 18.. Эмиттер смещающего транзистора 19 соединен с коллектором транзистора 11 промежуточного каскада, коллектор сое динен с базой выходного транзистора 1 и через нагрузочный резистор 20 - с положительной шиной 16 источника пита ния.База смещающего транзистора 19 со единена с объединенными базой и колле тором двyxэ шттepнoгo транзистора 21, коллектор которого через нагрузочный резистор 22 соединен с шиной 16 источ ника питания, первый эмиттер соединен с коллектором транзистора 10 промежуточного каскада,, а второй эмиттер сое динен с объединенными эмиттером выходного транзистора 15, базой и коллектором ограничивающего транзистора 23, эмиттер которого через стабилитрон 24 подсоединен к выходной,клемме 18. Компаратор работает следующим образом. Подача на входы 8 и 9 дифференциального сигнала напряжения вызывает увеличение тока через транзистор 1 М уменьшение тока через транзистор 2 на ту же величину. .Благодаря этому на входах промежуточного каскада в первый момент появляется напряжение, которое приводит к уменьшению тока черФ транзистор 10 и увеличению тока через транзистор 11 на ту же величину.Следствием этого изменения является изме нение напряжения на переходах эмиттербаза транзисторов 19 и 20. Так как потенциал объединенных баз транзисторов 19 и 21 фиксирован, то напряжение, в виде; дифференциального сигнала, ослабленного делителем, образованным резисторами 13 и 14 и вход ным сопротивлением транзисторов 10 и 11, появляется на входах промежуточнбго каскада. Таким образом, начальное изменение напряжения на входах промежуточного каскада благодаря передаче по петле положительной обратной связи вызывает на входах промежуточного каскада дополнительное дифференциальное нэп- ряжение,которое в свою очередь привоН ит к возникновению еще большегонапряжения и так далее. В результате этого суммарный сиг-нал напряжения на входах промежуточного каскада может значительно .превысить исходный сигнал. Формула изобретения Компаратор, содержащий дифференциальный усилитель на транзисторах,эмиттеры которых подсоединены к выходу генератора постоянного тока, базы - к входным клеммам, а коллекторы подсоединены к базам транзисторов промежуточного каскада, эмиттеры которых объединены и через опорный стабилитрон подсоединены к общей шине, коллекторы транзисторов промежуточного каскада через резисторы соединены с коллекторами транзисторов дифференциального усилителя, смещающий транзистор, выходной транзистор, коллектор которого соединен с источником положительного напряжения, нагрузочные резисторы и нагрузочный транзистор, база которого соединена с общей шиной, эмиттер соединен со входом генератора постоянного тока, а коллектор подсоединен к выходной клетле, отличающийся тем, что, с целью повышения быстродействия и увеличения коэффициента усиления при одновременном уменьшении потребляемой мощности, эмиттер смещающего транзистора соединен с коллектором второго транзистора промежуточного каскада, коллектор соединен с базой выходного транзистора и через первый нагрузочный резистор с положительной шиной источника питания, а база смещающего транзистора соединена с объединенными базой и коллектором введенного двухэмиттерного транзистора, коллектор которого через второй нагрузочный резистор соединен с источником положительного напряжения, причем первый эмиттер соединен с коллектором первого транзистора промежуточного каскада, а второй эмиттер соединен с объединенными эмиттером выходного транзистора, базой и коллектором введенного ограничивающе.го транзистора, эмиттер которого через стабилитрон подсоединен к выходной клемме. . Источники информации, принятые вЬ внимание при экспертизе: 1. Data book, Spring 19721973, компаратор М А фирмыHaircKiW semi .

| название | год | авторы | номер документа |

|---|---|---|---|

| Компаратор | 1979 |

|

SU813753A1 |

| Каскад со схемой стробирования | 1984 |

|

SU1193791A1 |

| Быстродействующий компаратор | 1973 |

|

SU515272A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Стробируемый компаратор | 1982 |

|

SU1056445A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1993 |

|

RU2060564C1 |

| ПАРАЛЛЕЛЬНЫЕ АПЕРИОДИЧЕСКИЕ УПЧ | 1993 |

|

RU2118063C1 |

| Устройство для регулирования температуры | 1988 |

|

SU1594503A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ТЕМПЕРАТУРЫ | 1992 |

|

RU2032209C1 |

Авторы

Даты

1978-04-25—Публикация

1975-01-03—Подача