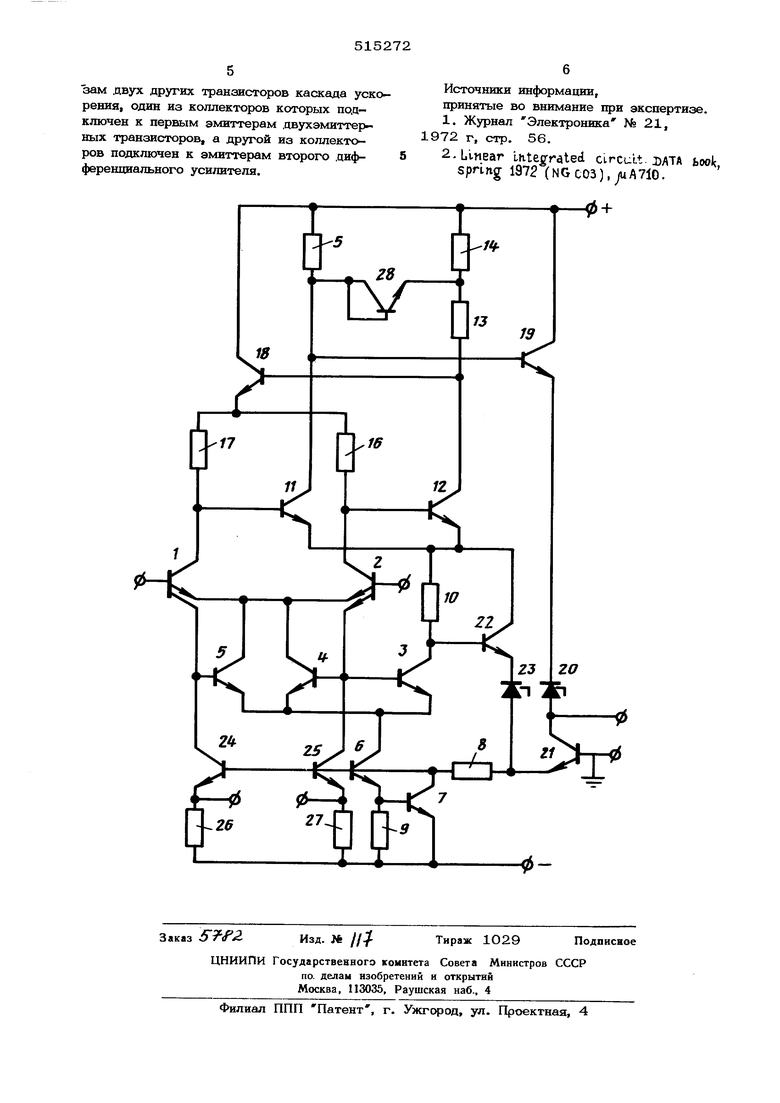

эмиттеры которых объединены и o6paajrjoT первый ДУ, а вторые эмиттеры подключены к входам каскада ускорения, на транзисторах 3-5 с объединенными эмиттерами, подключенными к выходу первого СИПТ, построенного на транзисторах 6 и 7 и резисторах 8, 9, причем второй эмиттер транзистора 1 пацключен к базе транзистора 5, коллектор которого подклю чен к объединенным эмиттерам транзисто ров 1 и 2, а второй эмиттер транзистора 2подключен к объединенным базам транзисторов 3 и 4. Коллектор транзистора 4 подключен к объединенным эмиттерам тра зисторов 1 и 2, а коллектор транзистора 3через резистор 1О подключен к объединеннъ1М эмиттерам транзисторов 11 и 12 образуюишх второй ДУ. В коллекторных цепях транзисторов 11 и 12 соответстувенно включенъ нагрузочнъю резисторы 13, 14 и 15, а в цепях коллекторов транзисторов 1 и 2 - резисторы 16 и 17 Коллекторы транзисторов 1 и 2 по,дключены базам соответственно транзисторов 11 и 12 образуют второй дифференциальный усилительный каскад, причем коллектор транаиг стора 12 по,дключен к базе транзистора 18, коллектор которого соединен с поло жительной шиной питания, а эмиттер - с резисторами 16 и 17. Коллектор транзи- стора 11 по.дключен к базе транзистора 19, к лектор которого сое,динен с положительной ш ной питания, г эмиттер - через стабилитрон с коллектором транзистора 21, база которого заземлена, а эмиттер соединен резистором 8. Эмиттеры транзисторов 11 и 12 соединены с коллектором транзистора 22, база которого подключена к коллектору транзистора 3, а эмиттер - через стабилитрон 23 к эмиттеру транзистора 21. К базам транзисторов 4 и 5 по,цключенъ1 коллекторные выходы второго и третьего управляемых СИПТ на транзисторах 24 и 25, базы которых объединен и подключены к базе транзистора 6, а эмиттеры через резисторы 26 и 27 соединены с отрицательной шиной питания. Между резисторами 13 и 15 включен диод 28. При подаче на базы транзисторов 1 и 2 равных напряжений на выходе устройства - коллекторе транзистора 21 устанавливается выходное напряжение, превышающее порог срабатывания подключенной к нему логической схемъ. Поступление на входы транзисторов 1 и 2 дифференциального сигнала приводит к однозначному переходу выходного напряжения в уровни, соответствующие ло гическому О или 1. Ток в первом ДУ равен сумме коллекторных токов транзисторов 4 и 5, так как токи через транзисторы 24 и 25 сравнительно малъь Ток во втором ДУ равен сумме коллекторных токов транзисторов 3 к 22. Причем сумма коллекторных токов транзисторов 3-5 постоянна и определяется током транзистора 6. Все транзисторы компаратора работают в активном режиме. При подаче отрицательного сигнала на базу транзистора 1 при заземленной базе транзистора 2 напряжение на входе второго ДУ в первый момент достигает большой величины и на выходе компаратора устанавливается О. Транзистор 11 начинает насыщаться, однако практически одновременно начинает запираться транзистор 5, что приводит к уменьшению тока через первый ДУ, стремящегося к величине коллекторного тока транзистора 4. Из-за уменьшения тока в первом ДУ уменьшается дифференциальный сигнал на его выходе, а следовательно, и степень насыщения транзистора 11. Благодаря эачэму в канале усиления компаратора отсутствуют транзистсры в режиме глубокого насыщения при подаче отрицательного сигнала на вход и длительность переходного процесса из одного логического состояния в другое ограничивается только временем перезаряда паразитных емкостей и на практике не превъш1ает 2 О нсек. Формула изобретения Быстродействующий компаратор, содержащий два диффаренциальнъ1х усилителя и стабилизированный источник постоянного тока, отличающийся тем, что, с целью повышения быстродействия и чувствительности, входной дифференциальнъ1Й каска.д выполнен на двух двухэмиттерных транзисторах, первые эмиттеры которых объединены и образуют первый дифференциальнъ1Й усилитель, вторые эмиттеры двухэмиттернъ1х транзисторов подключенъ к каска.цу ускорения, выполненному на трех транзисторах с объединенными амит терами и подключенному к стабилизированному источнику постоянного тока, причем первые эмиттеры двухэмиттернъ1х транзисторов соединенъ с коллектором одного из транзисторов каска,ца ускорения, база которого по.дключена ко второму эмиттеру первого двухэмиттерного транзистора, а второй эмиттер второго двухэмиттерного транзистора подключен к объединенным ба

| название | год | авторы | номер документа |

|---|---|---|---|

| Компаратор | 1975 |

|

SU604145A1 |

| Компаратор напряжений | 1978 |

|

SU902238A1 |

| Стробируемый формирователь | 1977 |

|

SU622199A1 |

| Стробируемый формирователь с парафазными ттл-выходами | 1978 |

|

SU758502A1 |

| Компаратор | 1979 |

|

SU813753A1 |

| Дифференциальный усилитель | 1983 |

|

SU1146792A1 |

| Стробируемый компаратор | 1982 |

|

SU1056445A1 |

| Устройство для управления поляризованным электромагнитным реле | 1983 |

|

SU1686696A1 |

| Дифференциальный усилитель | 1983 |

|

SU1124427A1 |

| Каскад со схемой стробирования | 1984 |

|

SU1193791A1 |

Авторы

Даты

1976-05-25—Публикация

1973-11-22—Подача