(54) УСТРОЙСТВО ДЛЯ ВРЕМЕННОГО УПЛОТНЕНИЯ ДИСКРЕТНЫХ КАНАЛОВ СВЯЗИ

12

вому и второму входам второго сумматора, выхрд которого соединен со входом первого накопителя и дополнительным входом декодера, выход которого подключен ко входу узла расширеймя формата, выход первого сумматора соединен со входом передатчика.

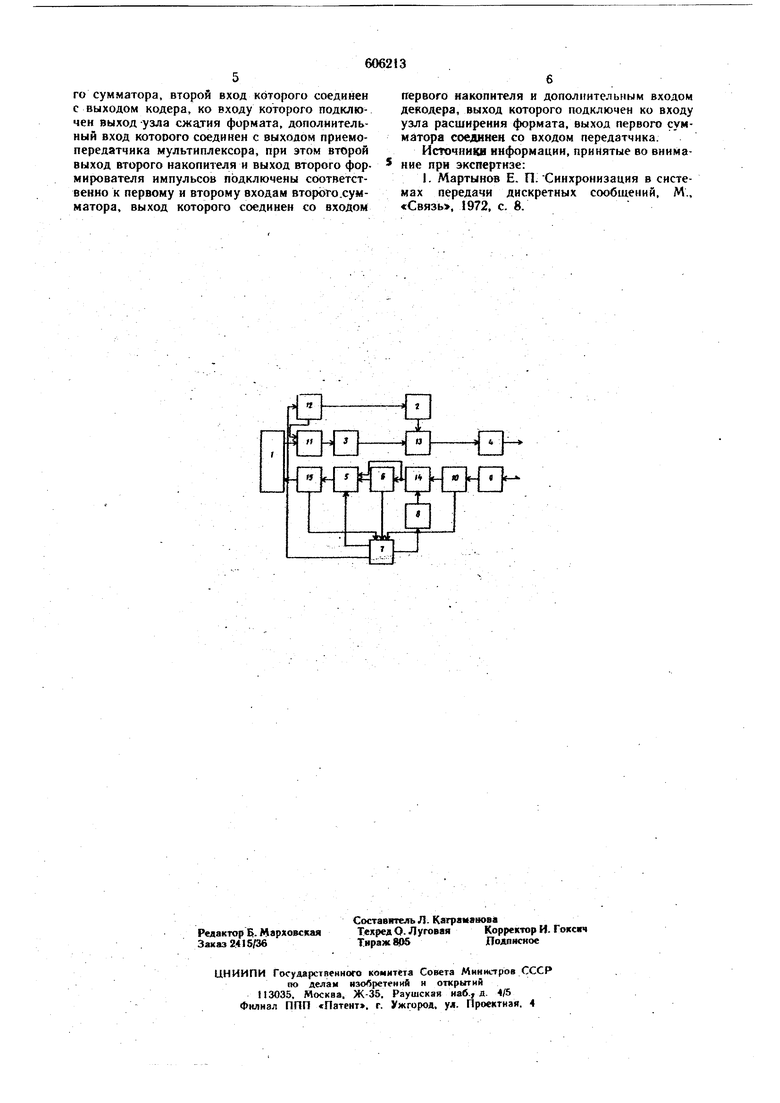

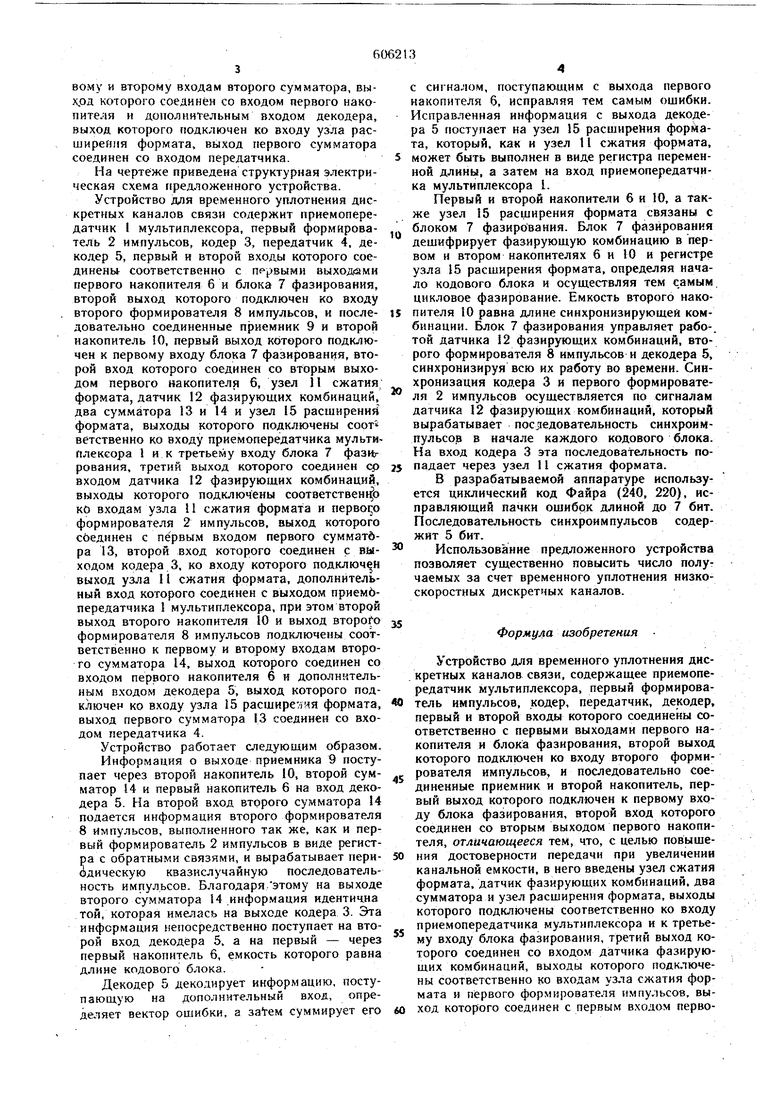

На черте же приведена структурная электрическая схема предложенного устройства.

Устройство для временного уплотнения дискретных каналов связи содержит приемопередатчик 1 мультиплексора, первый формирователь 2 импульсов, кодер 3, передатчик 4, декодер 5, первый и второй входы которого соединены соответственно с первыми выходами первого накопителя 6 и блока 7 фазирования, второй выход которого подключен ко входу второго формирователя 8 импульсов, и последовательно соединенные приемник 9 и второй накопитель 10, первый выход которого подключен к первому входу блока 7 фазирования, второй вход которого соединен со вторым выходом первого накопителя б, узел 11 сжатия; формата, датчик 2 фазирующих комбинаций, два сумматора 13 и 14 и узел 15 расширений формата, выходы которого подключены соот ветственно ко входу приемопередатчика мультиплексора 1 и к третьему входу блока 7 фазцг рования, третий выход которого соединен ср входом датчика 12 фазирующих комбинаций, выходы которого подключены соответственф ко входам узла П сжатия формата и nepBoijo формирователя 2 импульсов, выход которого соединен с первым входом первого сумматбра 13, второй вход которого соединен с выходом кодера 3, ко входу которого подключен выход узла 1 i сжатия формата, дополнительный вход которого соедкнен с выходом приембпередатчика 1 мультиплексора, при этом второй выход второго накопителя 10 и выход второго формирователя 8 импульсов подключены соответственно к первому и второму входам второго сумматора 14, выход которого соединен со входом первого накопителя 6 н дополнительным входом декодера 5, выход которого подключен ко входу узла 15 расшире:)ИЯ формата, выход первого сумматора 13 соединен со входом передатчика 4.

Устройство работает следующим образом.

Информация о выходе приемника 9 поступает через второй накопитель 10, второй сумматор 14 и первый накопитель 6 на вход декодера 5. На второй вход второго сумматора 14 подается информация второго формирователя 8 импульсов, выполненного так же, как и первый формирователь 2 импульсов в виде регистра с обратными связями, и вырабатывает периодическую квазислучайную последовательность импульсов. Благодаря этому на выходе второго сумматора 14 информация идентична той, которая имелась на выходе кодера 3. Эта информация непосредственно поступает на второй вход декодера 5, а на первый - через первый накопитель 6, емкость которого равна длине кодового блока.

Декодер 5 декодирует информацию, поступающую на дополнительный вход, определяет вектор ошибки, а загем суммирует его

с сигналом, поступающим с выхода первого накопителя 6, исправляя тем самым ошибки. Исправленная информация с выхода декодера 5 поступает на узел 15 расширения форйата, который, как и узел 11 сжатия формата, может быть выполнен в виде регистра переменной длины, а затем на вход приемопередатчика мультиплексора I.

Первый и второй накопители 6 и 10, а также узел 15 расширения формата связаны с блоком 7 фазирования. Блок 7 фазирования дешифрирует фазирующую комбинацию в первом и втором накопителях 6 и 10 и регистре узла 15 расширения формата, определяя начало кодового блока и осуществляя тем с.амым цикловое фазирование. Емкость второго накопителя 10 равна длине синхронизирующей комбинации. Блок 7 фазирования управляет рабо-. той датчика 12 фазирующих комбинаций, второго формирователя 8 импульсов и декодера 5, синхронизируя всю их работу во времени. Синхронизация кодера 3 и первого формирователя 2 импульсов осуществляется по сигналам датчика 12 фазирующих комбинаций, который вырабатывает пос 1едовательность синхроимпульсоэ в начале каждого кодового блока. На вход кодера 3 эта последовательность попадает через узел 11 сжатия формата.

В разрабатываемой аппаратуре используется циклический код Файра (240, 220), исправляющий пачки ощибрк длиной до 7 бит. Последовательность синхроимпульсов содержит 5 бит.

Использование предложенного устройства позволяет существенно повысить число получаемых за счет временного уплотнения иизкоскоростиых дискретных каналов.

Формула изобретения

Устройство для временного уплотнения дис. кретных каналов связи, содержащее приемопередатчик мультиплексора, первый формирователь импульсов, кодер, передатчик, декодер, первый и второй входы которого соединены соответственно с первыми выходами первого накопителя и блока фазирования, второй выход которого подключен ко входу второго формирователя импульсов, и последовательно соединенные приемник и второй накопитель, первый выход которого подключен к первому входу блока фазирования, второй вход которого соединен со вторым выходом первого накопителя, отличающееся тем, что, с целью повыщеиия достоверности передачи при увеличении канальной емкости, в него введены узел сжатия формата, датчик фазирующих комбинаций, два сумматора и узел расширения формата, выходы которого подключены соответственно ко входу приемопередатчика мультиплексора и к третьему входу блока фазирования, третий выход которого соединен со входом датчика фазирующих комбинаций, выходы которого подключены соответственно ко входам узла сжатия формата и первого формирователя импульсов, выход которого соединен с первым входом первого сумматора, второй вход которого соединен с выходом кодера, ко входу которого подключен выход -узла сжатия формата, дополнительный вход КОТОРОГО соединен с выходом приемопередатчика мультиплексора, при этом второй выход второго накопителя и выход второго формирователя импульсов подключены соответственно к первому и второму входам второго .сумматора, выход которого соединен со входом

ггервого накопнтеля и дополнительным входом декодера, выход которого подключен ко входу узла расшнрення формата, выход первого сумматора соединен со входом передатчика.

Источники ннформацин, принятые во внимание при экспертизе:

I. Мартынов Е. П: Сннхронизация в системах передачи дискретных сообщений, М., «Связь, 1972, с. 8.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1974 |

|

SU510792A1 |

| Адаптивная система передачи дискретных сообщений | 1986 |

|

SU1497755A1 |

| МОДУЛЬ УПЛОТНЕНИЯ РЕЧЕВЫХ СООБЩЕНИЙ ПАКЕТАМИ ДАННЫХ | 1995 |

|

RU2103825C1 |

| Устройство цикловой синхронизации для блочных кодов | 1975 |

|

SU565403A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| Устройство для контроля системыТЕлЕМЕХАНиКи | 1979 |

|

SU849274A2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| Устройство для проверки работоспособности аппаратуры передачи данных | 1977 |

|

SU690635A1 |

Авторы

Даты

1978-05-05—Публикация

1976-03-09—Подача