1

Изобретение относится к технике связи и может использоваться в устройствах передачи синхронных двоичных сигналов по цифровым трактам, в частности по цифровым трактам в системах с имиульсно-кодовой модуляцией.

Известно устройство асинхронного сопряжения синхронных двоичных сигналов, содержащее на передающем конце фазовый компараjrop, датчик фазирующей комбинации и блок памяти, к одному из входов записи служебных сигналов которого подключен выход датчика фазирующей комбинации, а на приемном конце коммутатор, блок фазирования по циклам, схему фазовой автоподстройки частоты (ФАПЧ) и блок памяти, к входам записи информации которого подсоединены информационные выходы коммутатора, а фазирующий выход коммутатора соединен с входом блока фазирования по циклам, управляющий выход которого подключен к сдвигающему входу коммутатора.

Однако известное устройство обладает недостаточно высокой помехоустойчивостью.

С целью увеличения помехоустойчивости в предлагаемом устройстве на передающем конце введен кодер фазы, вход которого соединен с первым выходом фазового компаратора, и управляемый распределитель, управляющий вход которого подключен к второму выходу

фазового компаратора, а выходы кодера фазы и управляемого распределителя подсоединены соответственно к выходам записи служебных сигналов и входам записи информации блока памяти, а на приемном конце введен декодер фазы, информационные входы которого соединены с выходами служебных сигналов коммутатора, а управляющий вход подключен к выходу опорных сигналов блока фаГзирования по цикла.м, и управляемый распределитель, управляющий вход которого вместе с входом схемы ФАПЧ соединен с выходом декодера фазы, тактирующий вход управляемого распределителя подключен к выходу схемы ФАПЧ, а выходы управляемого распределителя подключены к входам считывания блока памяти.

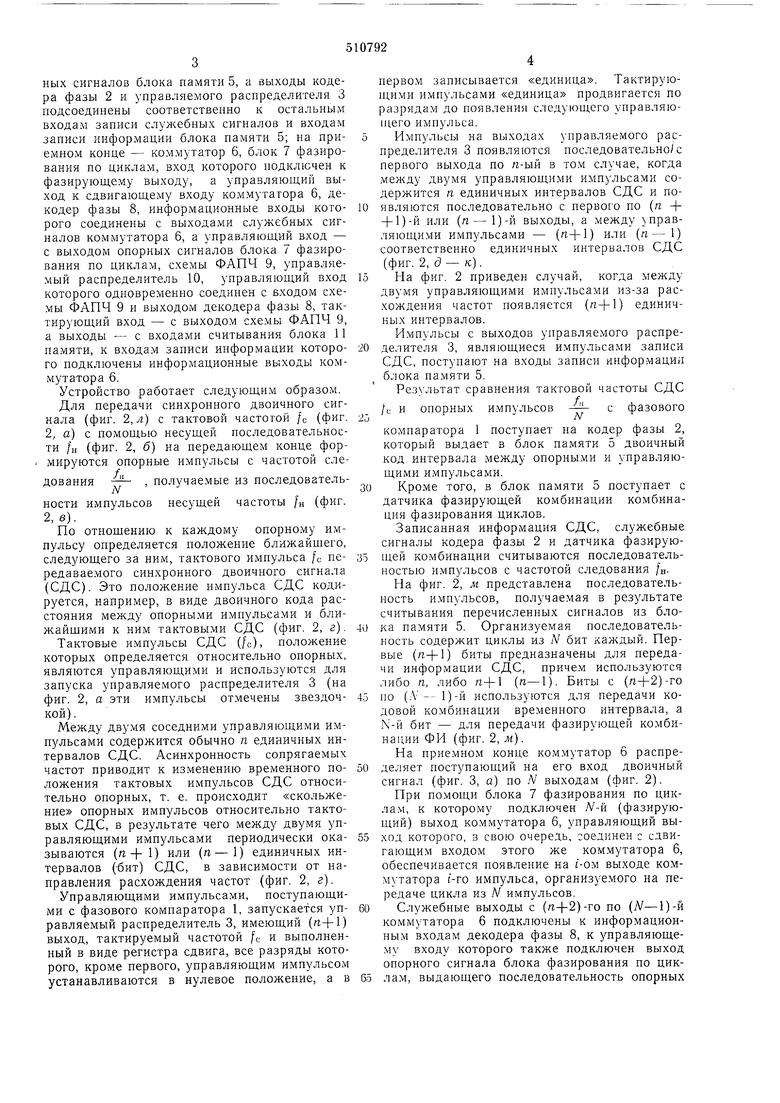

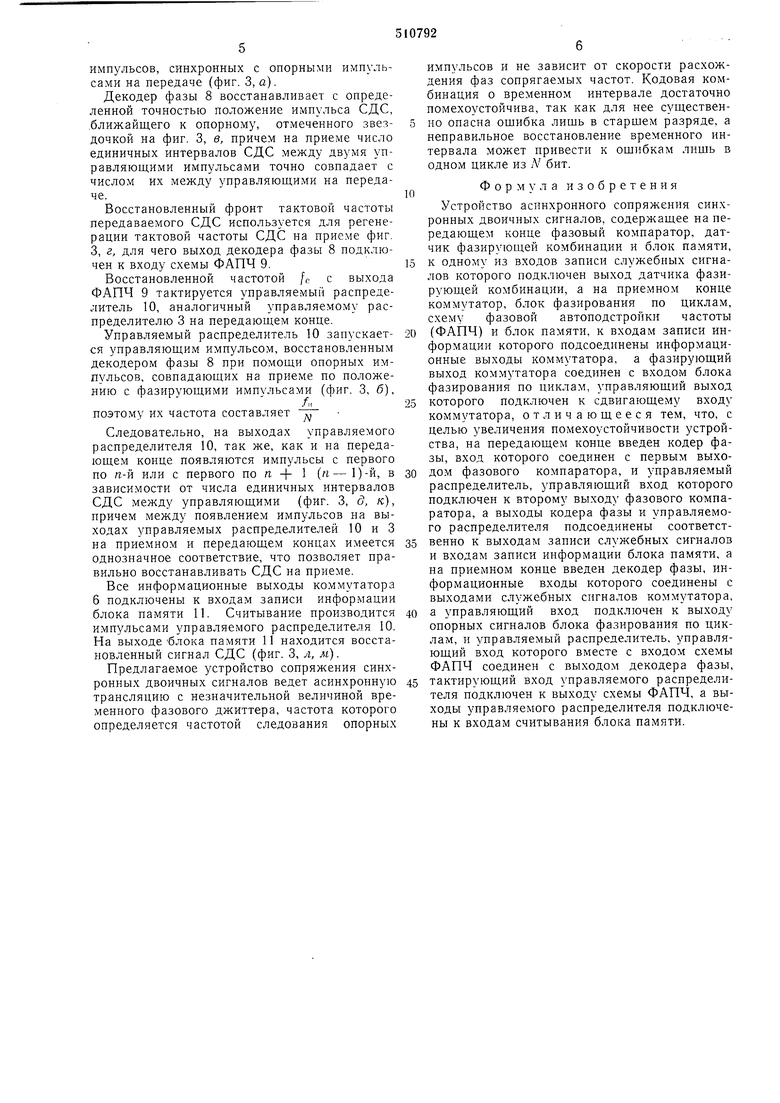

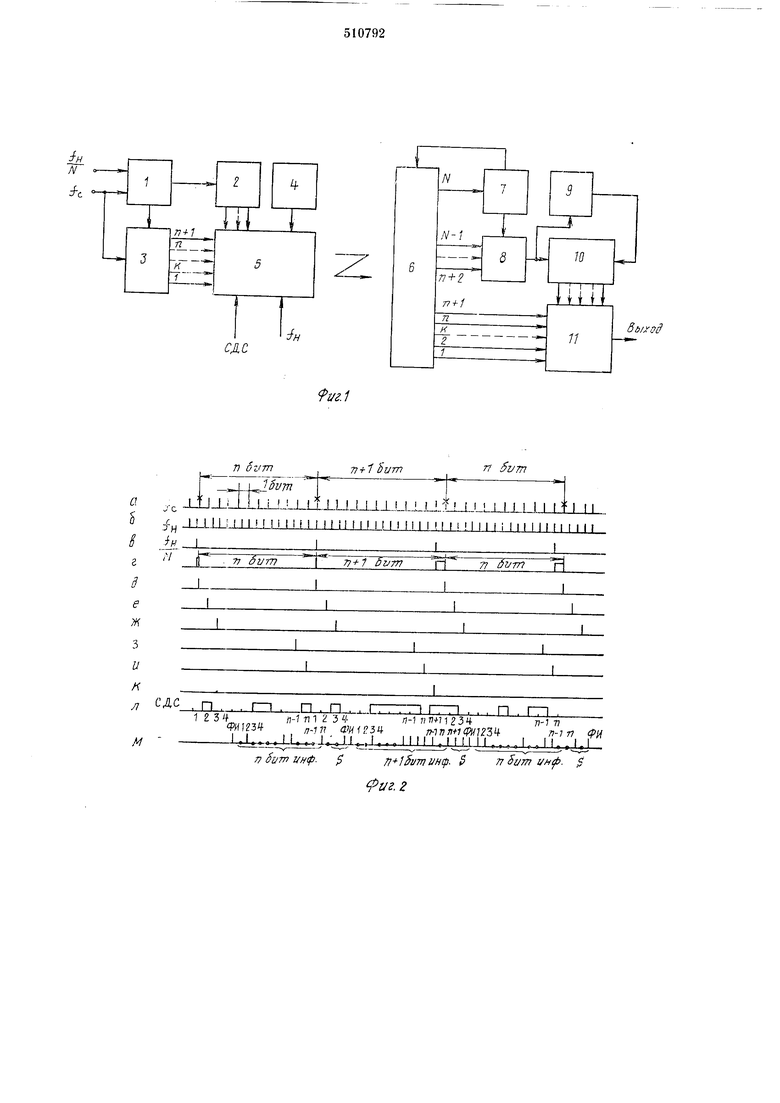

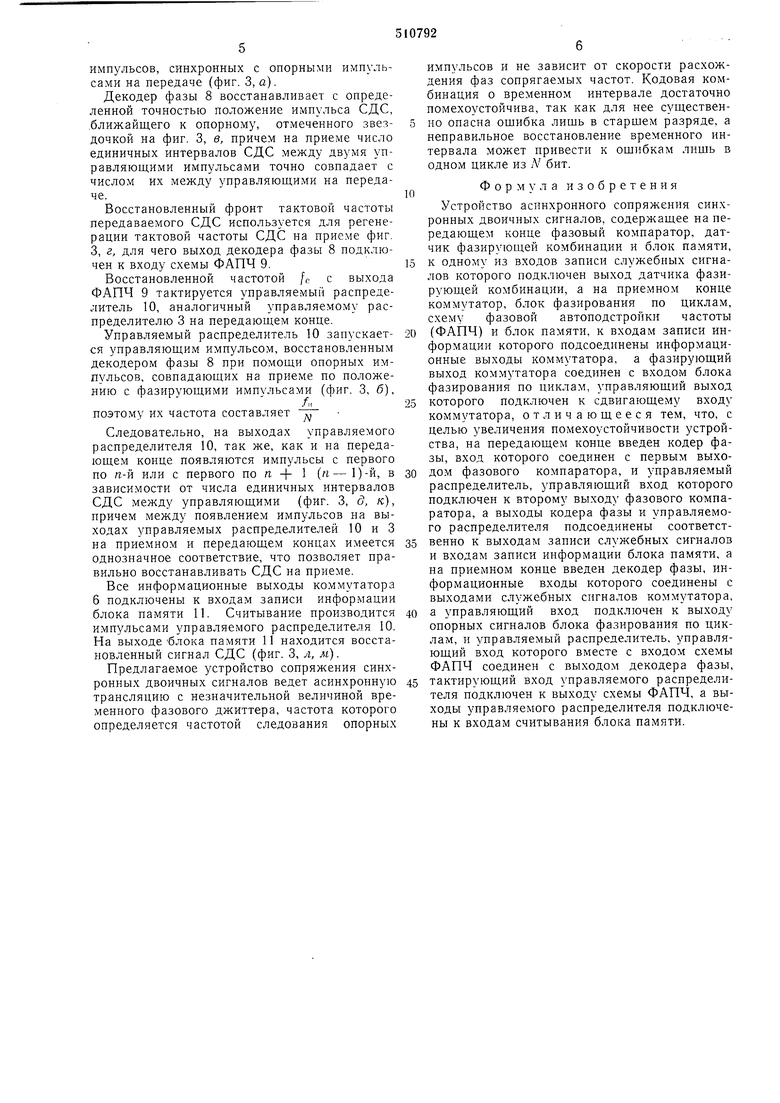

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 -

временные диаграммы процессов, происходящих на передающем конце устройства; на фиг. 3 - то же, на приемном конце.

Устройство асинхронного сопрялчения синхронных двоичных сигналов содержит на передающем конце фазовый компаратор 1, первым выходом соединенный с кодером фазы 2, а вторым выходом - с управляющим входом управляемого распределителя 3, дагчик 4 фазирующей комбинации, выход которого подключей к ОДНОМУ из входов записи служебных сигналов блока памяти 5, а выходы кодера фазы 2 и управляемого распределителя 3 подсоединены соответствепно к остальным входам записи служебных сигналов и входам записи информации блока памяти 5; на приемном конце - коммутатор 6, блок 7 фазирования по циклам, вход которого подключен к фазирующему выходу, а управляющий выход к сдвигающему входу коммутатора 6, декодер фазы 8, информационные входы которого соединены с выходами служебных сигналов коммутатора 6, а управляющий вход - с выходом опорных сигналов блока 7 фазирования по циклам, схемы ФАПЧ 9, управляемый распределитель 10, управляющий вход которого одновременно соединен с входом схемы ФАПЧ 9 и выходом декодера фазы 8, тактирующий вход - с выходом схемы ФАПЧ 9, а выходы - с входами считывания блока 11 памяти, к входам записи ипформации которого подключены информационные выходы коммутатора 6.

Устройство работает следующим образом.

Для передачи синхронного двоичного сигнала (фиг. 2., л) с тактовой частотой /с (фиг. 2, а) с помощью несущей последовательности /„ (фиг. 2, б) на передающем конце формируются опорные импульсы с частотой следования - , получаемые из последовательN

ности импульсов несущей частоты /н (фиг. 2, в).

По отношению к каждому опорному импульсу определяется положение ближайщего, следующего за ним, тактового импульса fc передаваемого синхронного двоичного сигнала (СДС). Это положение импульса СДС кодируется, например, в виде двоичного кода расстояния между опорными импульсами и ближайшими к ним тактовыми СДС (фиг. 2, г).

Тактовые импульсы СДС (fc), положение которых определяется относительно опорных, являются управляющими и используются для запуска управляемого распределителя 3 (на фиг. 2, а эти импульсы отмечены звездочкой).

Между двумя соседними управляющими импульсами содержится обычно п единичных интервалов СДС. Асинхронность сопрягаемых частот приводит к изменению временного положения тактовых импульсов СДС относительно опорных, т. е. происходит «скольжение опорных импульсов относительно тактовых СДС, в результате чего между двумя управляющими импульсами периодически оказываются (п+1) или (п-1) единичных интервалов (бит) СДС, в зависимости от направления расхождения частот (фиг. 2, г).

Управляющими импульсами, поступающими с фазового компаратора 1, запускается управляемый распределитель 3, имеющий (n+l) выход, тактируемый частотой /с и выполненный в виде регистра сдвига, все разряды которого, кроме первого, управляющим импульсом устанавливаются в нулевое положение, а в

первом записывается «единица. ТактируюН1,ими импульсами «единица продвигается по разрядам до появления следуюи;его управляющего импульса.

Импульсы на выходах управляемого распределителя 3 появляются последовательно/с первого выхода по я-ый в то.м случае, когда .между лТ,вумя управляющими импульсами содержится п единичных интервалов СДС и появляются последовательно с первого по (п + + 1)-й или (п- 1)-й выходы, а между управляющими импульсами - (п.-|-1) или (п- 1) соответственно единичных интервалов СДС (фиг. 2, (9 -к).

На фиг. 2 приведен случай, когда между двумя управляющими импульсами из-за расхождения частот появляется (п+1) единичных интервалов. Импульсы с выходов управляемого распределителя 3, являющиеся импульсами записи СДС, поступают на входы записи информации блока памяти 5.

Результат сравнения тактовой частоты СДС

/о и опорных импульсов - с фазового

yv

компаратора 1 поступает на кодер фазы 2, который выдает в блок памяти 5 двоичный код интервала между опорными и управляющими импульсами.

Кроме того, в блок памяти 5 поступает с датчика фазирующей комбинации комбинация фазирования циклов.

Записанная информация СДС, служебные сигналы кодера фазы 2 и датчика фазирующей комбинации считываются последовательностью импульсов с частотой следования /н.

На фиг. 2, м представлена последовательность импульсов, получаемая в результате считывания перечисленных сигналов из блока памяти 5. Организуемая последовательность содержит циклы из Л бит каждый. Первые (п+1) биты предназначены для передачи информации СДС, причем используются либо п, либо n-f-l (п-1). Биты с (л+2)-го

по (Л-- 1)-й используются для передачи кодовой комбинации временного интервала, а N-й бит - для передачи фазирующей комбинации ФИ (фиг. 2, м).

На приемном конце коммутатор 6 распределяет поступающий на его вход двоичный сигнал (фиг. 3, а) по ,V выходам (фиг. 2).

При помощи блока 7 фазирования по цикла.м, к которому подключен Л-й (фазирующий) выход коммутатора 6, управляющий выход которого, в свою очередь, соединен с сдвигающим входом этого же коммутатора 6, обеспечивается появление на J-ом выходе коммутатора (-ГО импульса, организуемого на передаче цикла из Л импульсов.

Служебные выходы с (п+2)-го по ()-й коммутатора 6 подключены к информационным входам декодера фазы 8, к управляющему входу которого также подключен выход опорного сигнала блока фазирования по циклам, выдающего последовательность опорных

импульсов, синхронных с опорными имп мьсами на передаче (фиг. 3, а).

Декодер фазы 8 восстанавливает с определенной точностью положение импульса СДС, .ближайщего к опорному, отмеченного звездочкой на фиг. 3, в, причем на приеме число единичных интервалов СДС между двумя управляющими импульсами точно совпадает с числом их между управляющими на передаче.

Восстановленный фронт тактовой частоты передаваемого СДС используется для регенерации тактовой частоты СДС на приеме фиг. 3, г, для чего выход декодера фазы 8 подключен к входу схемы ФАПЧ 9.

Восстановленной частотой с с выхода ФАПЧ 9 тактируется управляемый распределитель 10, аналогичный управляемому распределителю 3 на передающем конце.

Управляемый распределитель 10 запускается управляющим импульсом, восстановленным декодером фазы 8 при помощи опорных импульсов, совпадающих на приеме по положению с фазирующими импульсами (фиг. 3, б),

поэтому их частота составляет j

Следовательно, на выходах управляемого распределителя 10, так же, как и на передающем конце появляются импульсы с первого по ге-й или с первого по п + 1 (п- 1)-й, в зависимости от числа единичных интервалов СДС между управляющими (фиг. 3, д, к, причем между появлением импульсов на выходах управляемых распределителей 10 и 3 на приемном и передающем концах имеется однозначное соответствие, что позволяет правильно восстанавливать СДС на приеме.

Все информационные выходы коммутатора 6 подключены к входам записи информации блока памяти 11. Считывание производится импульсами управляемого распределителя 10. На выходеблока памяти 11 находится восстановленный сигнал СДС (фиг. 3, л, м}.

Предлагаемое устройство сопряжения синхронных двоичных сигналов ведет асинхронную трансляцию с незначительной величиной временного фазового джиттера, частота которого определяется частотой следования опорных

импульсов и не зависит от скорости расхождения фаз сопрягаемых частот. Кодовая комбинация о временном интервале достаточно помехоустойчива, так как для нее существенно опасна ошибка лишь в старшем разряде, а неправильное восстановление временного интервала может привести к ошибкам лищь в одном цикле из Л бит.

Форму л а изобретения

Устройство асинхронного сопряжения синхронных двоичных сигналов, содержащее на передающем конце фазовый компаратор, датчик фазирующей комбинации и блок памяти,

к одному из входов записи служебных сигналов которого подключен выход датчика фазирующей комбинации, а на приемном конце коммутатор, блок фазирования по циклам, схему фазовой автоподстройки частоты

(ФАПЧ) и блок памяти, к входам записи информации которого подсоединены информационные выходы коммутатора, а фазирующий выход коммутатора соединен с входом блока фазирования по циклам, управляющий выход

которого подключен к сдвигающему входу коммутатора, отличающееся тем, что, с целью увеличения помехоустойчивости устройства, на передающем конце введен кодер фазы, вход которого соединен с первым выходом фазового компаратора, и управляемый распределитель, управляющий вход которого подключен к второму выходу фазового компаратора, а выходы кодера фазы и управляемого распределителя подсоединены соответственно к выходам записи служебных сигналов и входам записи информации блока памяти, а на приемном конце введен декодер фазы, информационные входы которого соединены с выходами служебных сигналов коммутатора,

а управляющий вход подключен к выходу опорных сигналов блока фазирования по циклам, и управляемый распределитель, управляющий вход которого вместе с входом схемы ФАПЧ соединен с выходом декодера фазы,

тактирующий вход управляемого распределителя подключен к выходу схемы ФАПЧ, а выходы управляемого распределителя подключены к входам считывания блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1986 |

|

SU1401629A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1979 |

|

SU860326A1 |

| Устройство асинхронного ввода-вывода синхронной информации | 1982 |

|

SU1053307A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1978 |

|

SU786024A1 |

| Адаптивная система передачи дискретных сообщений | 1986 |

|

SU1497755A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1987 |

|

SU1649681A1 |

| Устройство для передачи ипРиЕМА диСКРЕТНОй иНфОРМАциипО пАРАллЕльНыМ КАНАлАМ СВязипЕРЕМЕННОй длиНы | 1978 |

|

SU794753A1 |

п бгтл Г -:..5m

.,.,I Т I i I М J I f 1 и I I и I М I t м I I I I I I I I f I I I

t

I M in Ml И II li I I I 11 III I M i II I Ml M l I I I i I II I I i II I I I I

h IIII СДС . П 12

п $vm

Т7+1 Sum SvJTj П . П . . I . . . ... fя- я123 - Л-1ППЯ123Ч- Л-) тг ФЯггз -/,-j7 (J«f 34л-1пл 1 1г34г -тп cfn LJ. .11.. ,. ji 111. J J Mii..., I., .I.L л Sum VHip- $n+T5vmuHcp. ё 7 dvrrT 71+1 биТП , . , п . 77 Sum UH. s 11 г. 2

И гЗЧп-гп WI234-fl-J/77(l ifl234п-1 п РИ

I.IT..- I I,.. I.. I I., I,.. I и 11.111 II 1,,,„1,.11, .1, L-,.,

4 -1I L Ь«F S- ath

Пп 5угпItj+1 Sum П 77 ог/7П П

. J f I I I I I I I I I I I f I I I I I I I 1 I 1 I I f I I I I I I I I I I I f I

II1L

IIIL

III

III

,

.1III, . II I I I 1. 1 I II .. I I . .

.П...1-1П.П.Г.1 |-П ... п.

123fЯ-1П123}/)-1пП+1123Ч-л-Т n

V3.2

Авторы

Даты

1976-04-15—Публикация

1974-06-07—Подача