Изобретение относится к технике связи и может использоваться в устройствах защиты от ошибок аппаратуры передачи данных.

Известно устройство цикловой синхронизации для блочных кодов, содержащее на передаче кодирующее устройство корректирующего кода, соединенное с сумматором по модулю два, к второму входу которого подсоединен генератор, управляемый цикловым распределителем, а на приеме - входной регистр сдвига с узлом вычисления проверок кода и дешифратором, генератор тактовых импульсов, соединенный .с делителем частоты, управляющим декодирующим устройством корректирующего кода и генератором смежного класса, соединенного с сумматором по модулю два, расположенным в цепи выходом регистра сдвига и входом декодирующего устройства.

СЗднако кодирование информации, осуществляемое смежными классами (п, k кодов позволяет обеспечить защиту от ложной установки цикловой синхронизации только на некоторых несинхронных сдвигах.

Известно также устройство цикловой синхронизации для блочных кодов, содержащее на -передающей стороне кодер, выход которого подключен к первому входу сумматора по модулю два, и ключ, к одному из входов которого подключен выход линии задержки.

причем к управляющим входам кодера и ключа подключен выход циклового распределителя, а на приемной стороне - последовательно соединенные входной регистр, выходы разрядов которого подключены к соответствующим входам блока вычисления проверок кода (ВПК), основной сумматор по модулю два и декодер, к управляющему входу которого подключен генератор тактовых импульсов через делитель частоты, а также накопитель, выходы которого подключены соответственно к входам ключа непосредственно, а к входам дешифратора - через дополнительные сумматоры по модулю два.

Такое устройство обладает недостаточной точностью установления цикловой синхронизации.

С целью повыщения точности установления цикловой синхронизации в предлагаемое устройство цикловой синхронизации для блочных кодов на передающей стороне введены узел определения ненулевых компонент (ОНК), формирователь элементов смежного кода (ЭСК) и элемент ИЛИ, при этом меладу

управляющим входом и выходом ключа включены последовательно соединенные формирователь ЭСК и элемент ИЛИ, выход которого через последовательно соединенные основной сумматор по модулю два и узел ОНК подключен к входу элемента задержки, а на приемной стороне введены узел исключения нензлевых компонент (ИНК), формирователь ЭСК и элемент ИЛИ, при этом выходы блока ВПК через узел ИНК подключены соответственно к входам накопителя, дополнительных сумматоров по модулю два и дешифратора, к дополнительным входам которого подключены соответствующие выходы накопителя, а выход дешифратора подключен к второму входу делителя частоты, выход которого подключен к соответствующим входам узла ИНК и ключа непосредственно, а ко второму входу основного сумматора по модулю два через последовательно соединенные формирователь ЭСК и элемент ИЛИ.

Такое устройство обеспечивает повышение точности установления цикловой синхронизации за счет анализа результатов проверки дешифратором сдвигов кодовой последовательности с учетом дополнительно передаваемой информации о применяемом смежном классе кода.

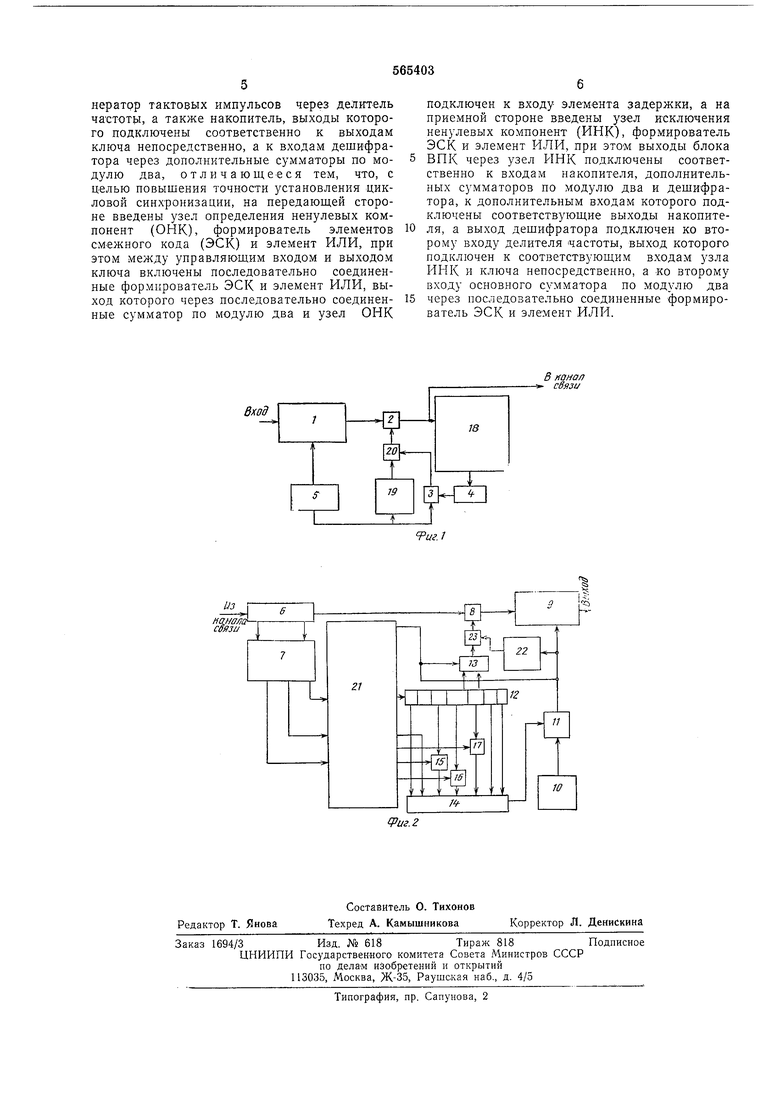

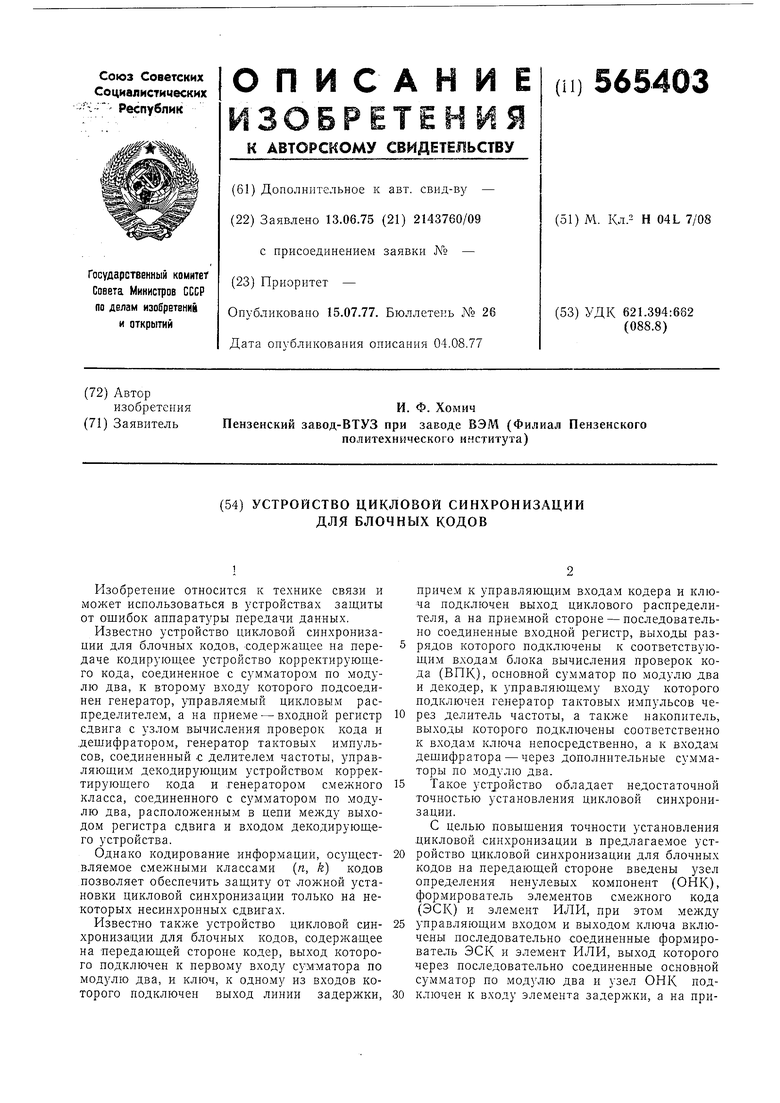

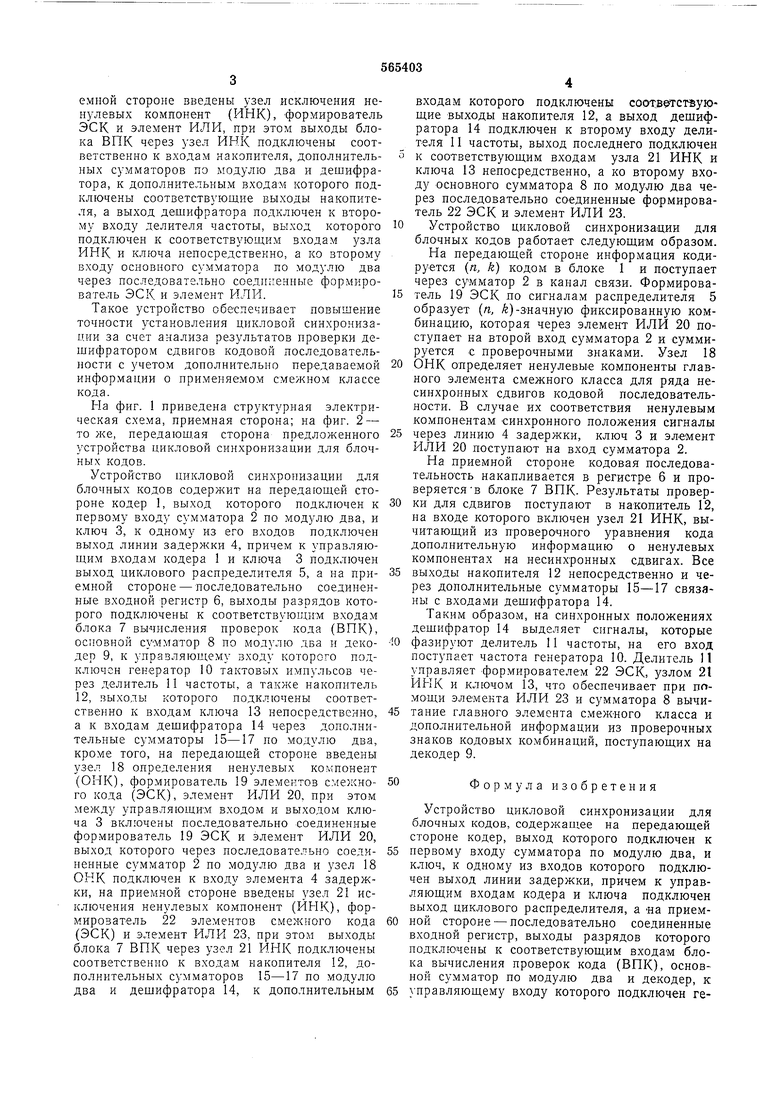

На фиг. 1 приведена структурная электрическая схема, приемная сторона; на фиг. 2 - то же, передаюшля сторона предложенного устройства цикловой синхронизации для блочных кодов.

Устройство цикловой синхронизации для блочных кодов содержит на передающей стороне кодер 1, выход которого подключен к перво.му входу сумматора 2 по модулю два, и ключ 3, к одному из его входов подключен выход линии задержки 4, причем к управляющим входам кодера 1 и ключа 3 подключен выход циклового распределителя 5, а на приемной стороне - последовательно соединенные входной регистр 6, выходы разрядов которого подключены к соответствующим входам блока 7 вычисления проверок кода (ВПК), остговной сумматор 8 по модулю два и декодер 9, к управляющему входу которого подключен генератор 10 тактовых импульсов через делитель 11 частоты, а также накопитель 12, выходы которого подключены соответственно к входам ключа 13 непосредственно, а к входам дешифратора 14 через дополнительные сумматоры 15-17 по модулю два, кроме того, на передающей стороне введены узел 18 определения ненулевых компонент (ОНК), формирователь 19 элементов смежного кода (ЭСК), элемент ИЛИ 20, при этом между управляющим входом и выходом ключа 3 включены последовательно соединенные формирователь 19 ЭСК и элемент ИЛИ 20, выход которого через последовательно соедипенные сумматор 2 по модулю два и узел 18 ОНК подключен к входу элемента 4 задержки, на приемной стороне введены узел 21 исключения ненулевых компонент (ИНК), формирователь 22 элементов смежного кода (ЭСК) и элемент ИЛИ 23, при этом выходы блока 7 ВПК через узел 21 ИНК подключены соответственно к входам накопителя 12, дополнительных сумматоров 15-17 по модулю два и дешифратора 14, к дополнительным

входам которого подключены соответствующие выходы накопителя 12, а выход дешифратора 14 подключен к второму входу делителя 11 частоты, выход последнего подключен к соответствующим входам узла 21 ИНК и ключа 13 непосредственно, а ко второму входу основного сумматора 8 по модулю два через последовательно соединенные формирователь 22 ЭСК и элемент ИЛИ 23.

Устройство цикловой синхронизации для блочных кодов работает следующим образом.

На передающей стороне информация кодируется (л, k) кодом в блоке I и поступает через сумматор 2 в канал связи. Формирователь 19 ЭСК по сигнала.м распределителя 5 образует (п, й)-значную фиксированную комбинацию, которая через элемент ИЛИ 20 поступает на второй вход сумматора 2 и суммируется с проверочными знаками. Узел 18 ОНК определяет ненулевые компоненты главного элемента смежного класса для ряда несинхронных сдвигов кодовой последовательности. В случае их соответствия ненулевым компонентам синхронного положения сигналы через линию 4 задержки, ключ 3 и элемент ИЛИ 20 поступают на вход сумматора 2.

На приемной стороне кодовая последовательность накапливается в регистре 6 и проверяетсяв блоке 7 ВПК. Результаты проверки для сдвигов поступают в накопитель 12, на входе которого включен узел 21 ИНК, вычитающий из проверочного уравнения кода дополнительную информацию о ненулевых компонентах на несинхронных сдвигах. Все выходы накопителя 12 непосредственно и через дополнительные сумматоры 15-17 связаны с входами дещифратора 14.

Таким образом, на синхронных положениях дешифратор 14 выделяет сигналы, которые фазируют делитель 11 частоты, на его вход поступает частота генератора 10. Делитель 11 управляет формирователем 22 ЭСК, узлом 21 ИНК и ключом 13, что обеспечивает при помощи элемента ИЛИ 23 и сумматора 8 вычитание главного элемента смеж«ого класса и дополнительной информации из проверочных знаков кодовых комбинаций, иоступающих на декодер 9.

Формула изобретения

Устройство цикловой синхронизации для блочных кодов, содержащее на передающей стороне кодер, выход которого подключен к первому входу сумматора по модулю два, и ключ, к одному из входов которого подключен выход линии задержки, причем к управляющим входам кодера и ключа подключен выход циклового распределителя, а яа приемиой стороне - последовательно соединенные в.ходной регистр, выходы разрядов которого подключены к соответствующим входам блока вычисления проверок кода (ВПК), основной сум.матор по модулю два и декодер, к }-правляющему входу которого подключен генератрр тактовых импульсов через делитель частоты, а также накопитель, выходы которого подключены соответственно к выходам ключа непосредственно, а к входам дешифратора через дополнительные сумматоры по модулю два, отличающе еся тем, что, с целью повышения точности установления цикловой синхронизации, на передаюш,ей стороне введены узел определения ненулевых компонент (ОНК), формирователь элементов смежного кода (ЭСК) и элемент ИЛИ, при этом между управляющим входом и выходом ключа включены последовательно соединенные формирователь ЭСК и элемент ИЛИ, выход которого через последовательно соединенные сумматор по модулю два и узел ОНК

подключен к входу элемента задержки, а на приемной стороне введены узел исключения ненулевых компонент (ИНК), формирователь ЭСК и элемент ИЛИ, при этом выходы блока ВПК через узел ИНК подключены соответственно к входам накопителя, дополнительных сумматоров по модулю два и дешифратора, к дополнительным входам которого подключены соответствующие выходы накопителя, а выход дешифратора подключен ко второму входу делителя частоты, выход которого подключен к соответствующим входам узла ИНК и ключа непосредственно, а ко второму входу основного сумматора по модулю два

через последовательно соединенные формирователь ЭСК и элемент ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации для групповых кодов | 1975 |

|

SU557502A1 |

| Устройство цикловой синхронизации для блочных кодов | 1975 |

|

SU557499A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ ДАННЫХ, ПЕРЕДАВАЕМЫХ С ИСПОЛЬЗОВАНИЕМ БЛОЧНЫХ РАЗДЕЛИМЫХ КОДОВ, ОТ ИМИТИРУЮЩИХ ДЕЙСТВИЙ ЗЛОУМЫШЛЕННИКА | 2019 |

|

RU2738789C1 |

| Устройство блочной синхронизации для групповых кодов | 1980 |

|

SU932643A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ С СЕЛЕКТИВНЫМ ЗАПРОСОМ ОШИБОК | 1991 |

|

RU2019044C1 |

Вход

В канал связи

Авторы

Даты

1977-07-15—Публикация

1975-06-13—Подача