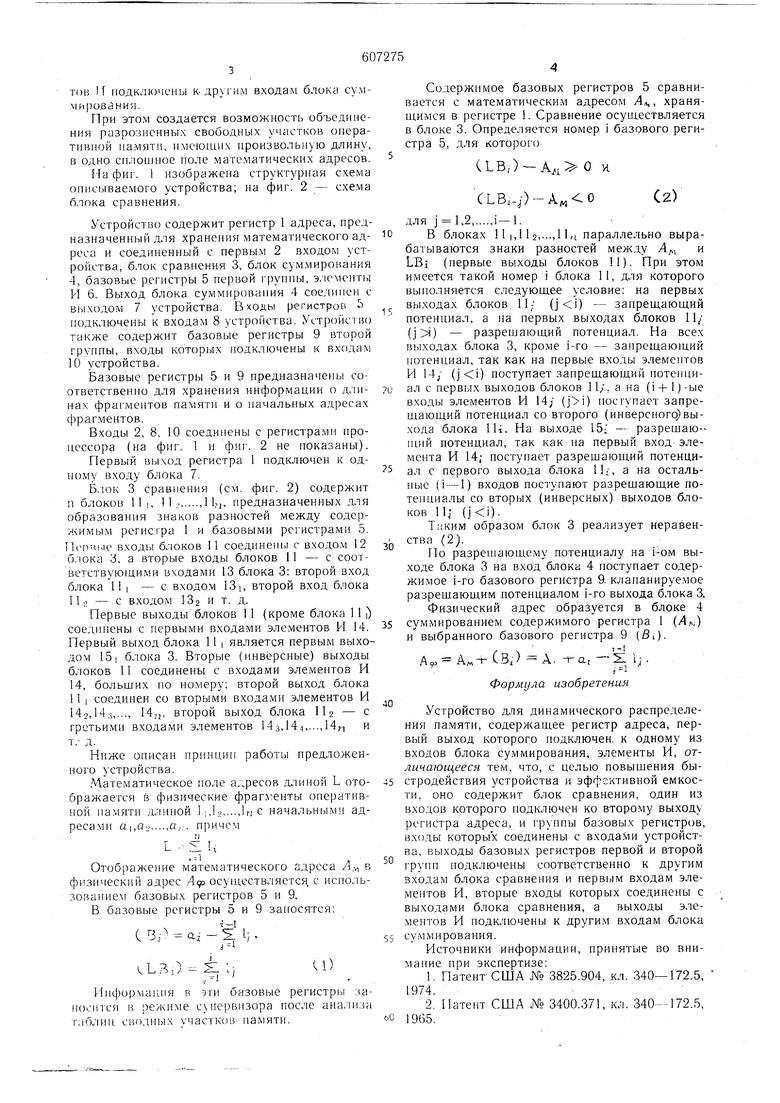

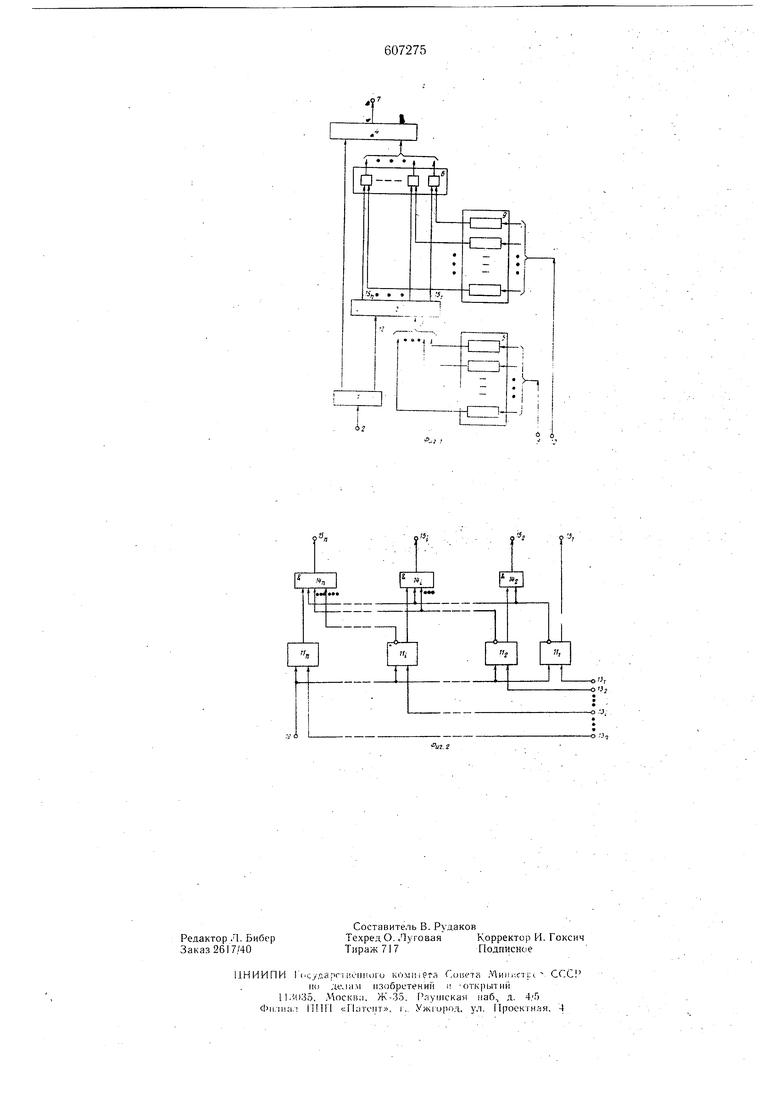

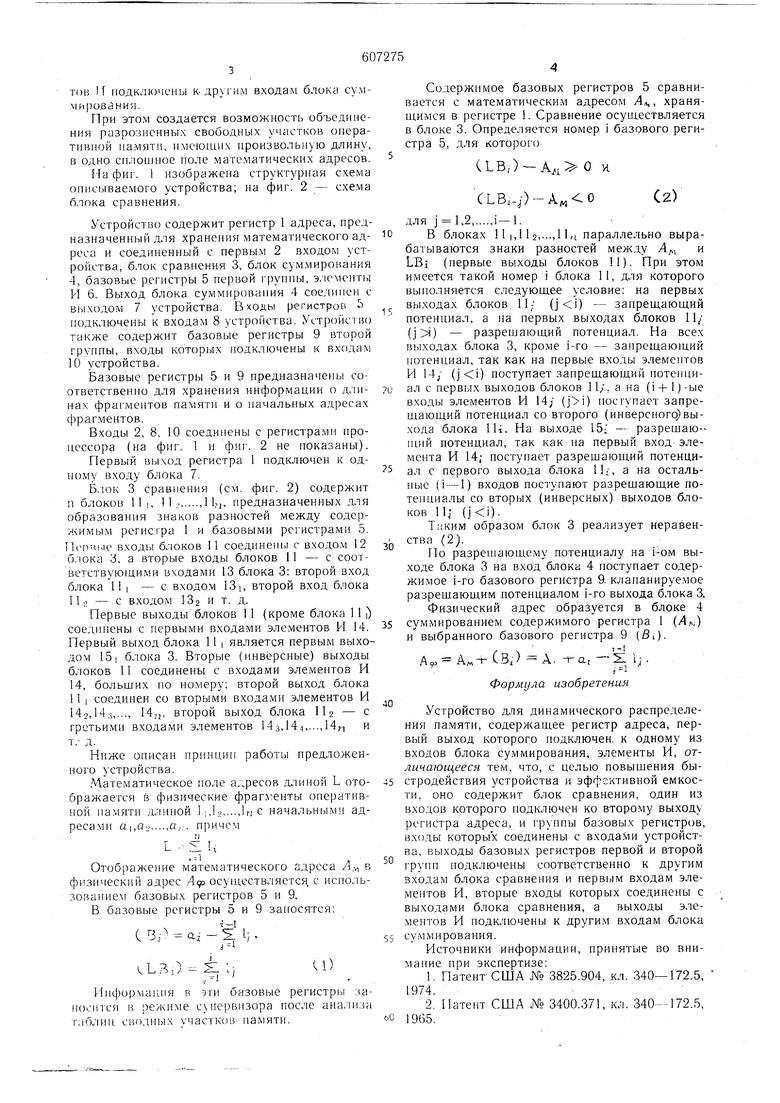

(54) УСТРОЙСТВО ДЛЯ ДИНАМИЧЕСКСЯХ) РАСПРЕДЕЛЕНИЯ ПАМЯТИ тов и подключены к-другим входам блока сумми )о.вания. При этом создается возможность объединения разрозненных свободных участков оперативной памяти, имеющих ироизвольную длину, в одно сплошное поле математических адресов. Ма фиг. 1 изображена структурная схема онисываемого устройства; на фиг. 2 - схема блока сравнения. Устройство содержит регистр 1 адреса, пре;л,назначенный для хранения математического адреса и соединенный с первым 2 входом устройства, блок сравнения 3, блок суммирования 4, базовые регистры 5 первой группы,элементы И 6. Выход блока суммирования 4 соединен с выходом 7 устройства. Входы регистров v) подключены к входам 8 устройства. Устройство также содержит базовые регистры 9 второй группы, входы которых подключены к входам 10устройства. Базовые регистры 5 и 9 предназначены соответственно для хране)ия информации о д;1инах фрагментов памяти и о начальных адресах ((фрагментов. Входы 2, 8, 10 соединены с регистрами процессора (на фиг. 1 и фиг. 2 не показаны). Первый выход регистра 1 подключен к одному входу блока 7. Блок 3 сравнения (см. фиг. 2) содержит а блоков 11 I, И ,,1 К,, предназначенных для образования знаков разностей между содержимы.м регистра 1 и базовыми регистрами 5. rieiiHMc входы боюков П соедине1п 1 с входом 12 б.,1ока 3, а вторые входы блоков 11 - с соответствующими входами 13 блока 3: второй вход блока HI - с входом 131, второй вход блока 11.1 - с входом 132 и т. д. Первые выходы блоков 11 (кроме блока 11 |) сое.чинены с первыми входами эле.ментов И 14. Первый выход блока 11 i является первым выходом 15 блока 3. Вторые (инверсные) выходы блоков 11 соединены с входами элементов И 14, больших по номеру; второй выход блока 11I соединен со вторыми входами элементов И 14.2,14:;,..., 14,;, второй ВЫХОД блока 112 - с третьими входами элементов 14з,144,..., и т.- д. Ниже описан принцип работы предложенного устройства. Математическое поле адресов длиной L отображается в физические фрагменты оперативной иа.мяти длиной I.;,l2----.lri с начальн|11ми адресами ai,,:. причем L -S U Отоб)ажеиие математического адреса А- в физический адрес . осуществляется с использованием базовых регистров 5 и 9. В базовые регистры 5 и 9 заносятся: СЗ.-а,. iLB,) - Ииформа1и я в эти базовые регистр|1| носится в режи.ме супервизора после ана, таблиц СВОДН131Х участков памяти. Содержимое базовых регистров 5 сравнивается с математическим адресом Ал,, хранящимся в регистре 1. Сравнение осуществляется в блоке 3. Определяется номер i базового регистра 5, для которого CLB,)-A,,0 (LB, для j l,2,....,i- 1.. В блоках 11 1,112,...,11,1 параллельно вырабатываются знаки разностей между Af. и LBi (первые выходы блоков 11). При этом имеется такой номер i блока 11, для которого выполняется следующее условие: на первых выходах блоков 11; (j i) - запрещающий потенциал, а на первых выходах блоков 11/ () - разрешающий потенциал. На всех выходах блока 3, кроме i-ro - запрещающий потенциал, так как на первые входы элементов И 14j () поступает запрещающий потенциал с первых выходов блоков 11;, а на (1 + 1)-ые входы элементов И 14/ () посгупает запрещающий потенциал со второго (инверсного выхода блока 111. На выходе 15; - разрешающий потенциал, так как на первый вход элемента И 14; поступает разрешающий потенциал с первого выхода блока 11/, а на остальЕ1ые (i-1) входов постунают разрещаюц ие потенциалы со вторых (инверсных) выходов блоков llj (). Таким образом блок 3 реализует неравенства (2). По разренгающему потенциалу на i-ом вы.ходе блока 3 на вход блока 4 поступает содержимое i-ro базового регистра 9. клапанируемое разрешающим потенциалом i-ro выхода блока 3. Физический адрес образуется в блоке 4 суммированием содержимого регистра 1 (Л,) и выбранного базового регистра 9 (ВО. -J. А 50 А„ + С .В|) А. -t-а, - i j . Формула изобретения Устройство для динамического распределения па.мяти, содержащее регистр адреса, первый выход которого подключен, к одному из ходов блока суммирования, элементы И, отичающееся тем, что, с целью повышения бытродействия устройства и эффективной емкоси, оно содержит блок сравнения, один из ходов которого подключен ко второму выходу регистра адреса, и группы базовых регистров, ходы которых соединены с входами устройста, выходы базовых регистров первой и второй рупп подключены соответственно к другим ходам блока сравнения и перв| 1м входам элеентов И, вторые входы которых соединены с ыходами блока сравнения, а выходы элеентов И подключены к другим входам блока у.ммнрования. Источники информации, принятые во вниание при экспертизе: 1.Патент США № 3825.904, кл. 340-172.5, 974. 2.Патент США № 3400.371, кл. 340--172.5, 965.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| Устройство для адресации блоков памяти | 1986 |

|

SU1394217A1 |

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| Запоминающее устройство | 1985 |

|

SU1325564A1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Устройство для моделирования узлов коммутации сообщений | 1986 |

|

SU1354203A1 |

| Многоканальное устройство для ввода информации | 1989 |

|

SU1612290A2 |

| Устройство буферной памяти | 1988 |

|

SU1596390A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

с,},

Авторы

Даты

1978-05-15—Публикация

1976-03-01—Подача