(54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

| Логическое запоминающее устройство | 1979 |

|

SU858103A2 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Логическое запоминающее устройство | 1986 |

|

SU1316047A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

1

Изобретение относится к запоминающим устройствам.

Известно логическое запоминающее устройство, содержащее числовые линейки, разрядные шины которых по.шслючены к выходам разрядного блока управления, линейные шины - к выходам адресного блока управления, шины чтения - ко входам выходного регистра, выходы которого соединены со входами элементов И первой группы, регистр слова, входы коi торого подключены к выходам элементов И второй группы, а выходы - ко входам разрядного блока управления, управI ляющие шины, шины индикации и ночальной установки.

Известное логическое запоминающее устройство не позволяет производить логическую обработку массивов информации распределенных произвольным образом

по объему накопителя, что ограничивает функциональные возможности устройства.

Подобная задача возникает при использовании логического запоминающего устройства в системах обработки дискретно

информации, поступающей от нескольких периферийных устройств в проиаяольиые

I моменты времени.

Описываемое устройство отяичает я

от известного тем , что оно содержит

блок модификации адреса и блок формирования массивов, входы которого пошел ючв ны к выходам регистра адреса и блока

j модификации адреса, соединенным функциональными входами элементов И вто рой группы, а выходы - соответственно ко входам адресного блока управления и шинам индикации, выходы элементов И первой группы подключены ко входам регистра адреса и одним входам блока модификации адреса, другие входы которого соединены,соответственно с управляющими шинами и шинами начальной установки. Все о позволяет расширить функциональные возможности устройства.

На чертеже изображена блок-схема логического запоминающего устройства. Оно содержит накопитель 1, состоящий из числовых линеек 2, линейные 3 и разрядньте 4 шины которых подключи-

ц,т соответственно к .ояам адресного 5 и разрядного 6 блоков управления, а шины чтения 7 соединены со входами выходного регистра 8. Выходные шины выходного регистра 8 соединены через

элементы И первой группы 10 со вхо дами 11 регистра адреса 12 и мс диф11кации адреса 13, выходы которых пс z ключены к функциональным входам ячеек 14 блока 15 формирования массивов и ко в; одам элементов И второй группы 16, И t выходы соединены с входными шинами 1 регистра слова 18, выходы которого под ключены ко входам разрядного блока упр в- Ленин 6.

Управляющие входы ячеек 14 соедине 1Ы с шинами управления 19-22, управляющ е входы элементов --И 16 подключены к i и- не управления 23, а счетные входы перв ьго и второго разрядов блока 13 соедине: ы с шинами управления 24.

Выход признака модификации 25 каждо ячейки I-t подключен к шине индикации 26.

Выход индикации состояния 27 перво{ ячейки 14 блока 15 соединен со входом запрета записи 28 втсрой ячейки 14. Вх )д запрета записи 28 каждой последующей я ей ки 14 подключен к выходу индикашш сое Х)яния 27 предыдущей ячейки 14, а выход индикации с :;тояния 27 последней ячейки 4 соединен с шиной 29 индикации сооторниi накопителя.

Управляющий выход 30 каждой ячейки 1 блока 15 подключен к соответствующекчу входу адресного блока управления 5 и, к оме последней, - к разрешающему входу с 1 последующей ячейки 14, а управляющий i ыход ЗО последней ячейки 14 соединен с разрешающим входом 31 первой ячейки 4 Кроме того, устройство содержит шины у гравления 32 адресным 5 и разрядным 6 блоками управления, шины начальной уст/ новки 33 блока 13, шину управления 34 первой группой элементов И 10. Вход запрета записи 28 каждой ячейки 14 notключен через разделительный диод 35 кс входу запрета записи 28 предыдущей яче Sки 14, а выход 27 последней ячейки 14 через разделительный диод 35 - ко вход запрета записи 28 этой ячейки.

Предложенное логическое запоминающее устройство имеет два основных режима р iботы: режим записи массивов информации и режим их логической обработки.

Каждому массиву информации .присваи ается признак, называемый начальным адр сом массива. Запись массивов информаци: производится в незанятые к моменту зап си числовые линейки 2 накопителя 1. Часть массива, записанная в следующих по пор оку числов 1х линейках 2, называется подмассивом д; иного массива информации. Каждому подмассиву присваивается соответствующий признак, называемый текущим адресом массива, представляющий собой (fe ). - разрядный код, в котором R, старших разрядов образованы полем начального адреса массива, а С младших разрядов - полем константы модификации, являющейся порядковым номером подмаосива в данном массиве информации.

Текущий адрес, соответствующий каждому последующему полмассиву некоторого массива информации, увеличивается на единицу младшего разряда по сравнению с текущим адресом предыдущего подмассива.

Будем считать, что в режиме записи различные массивы информации могут поступать от периферийных устройств (на чертеже не показаны) по частям, причем отдельные части одного и того же массива могут следовать через произвольные промежутки времени, в течение которых устройство может производить запись отдельных частей других массивов информации.

Для организации правильной очереднооти подмассивов каждого массива информации после окончания записи отдельной части массива текущий адрес увеличивается на единицу младшего разряда и хранится в одной из числовых линеек 2 накопителя 1 до поступления очередной части этого мво- сива информации.

При поступлении от перифорий1Стх уст ройств очередной части некоторюго массива информации в накопителе 1 производится выборка и считывание текущего адреса этого массива. При этом логическое упоминающее устройство работает во вспомогательном режиме - в режиме обращения к текущему адресу.

Выборка требуемой числовой 1ттнейки 2 в накопителе 1. производится по признаку. Числовые линейки 2, в которых записаны слова одного и того же подмассива, имеют одинаковый признак, представляющий собой текущий адрес, соответствующий этому полмассиву. Признак каждой числовой линейки 2 хранится в ячейке 14, соответствующей этой линейке. Числовая линейка считается выбранной, если код текущего адреса массива, формируемый в регистре адреса 12 и в блоке 13, совпадает с кодом, хранящимся в ячейке 14, соответствующей этой числовой линейке.

Признак числовой линейки, в которой хранится код текущего адреса мас..ива, преставляет собой ( h, € i ) - разрядное двоичное число, в fe старших разрядах

которого записан код начялыюго адреса массива, а в млатшем рязряде - единица, если в этой числовой пинейке хранится код текущего адреса записи массива информации, или младшем разряде записая нуль, если в этой числовой линейке хр«(йнтся код текущего адреса обработки массява информации. В остальных разрядах этого двоичного числа записаны нули.

Коды признаков тех числовых лкнеек, в которых хранятся коды текущих адресов массивов, формируются в регистре адреса 12 и блоке 13. Поэтому, обшая длина разрядной сетки регистра адреса 12 и блока 13 составляет Ь. € i ра; рядов, fe 6 старших разрядов используются для формирования текущих адресов массивов, а младший разряд - только при формировании кодов признаков числовых линеек, в которых хранятся коды текущих адресов, массивов.

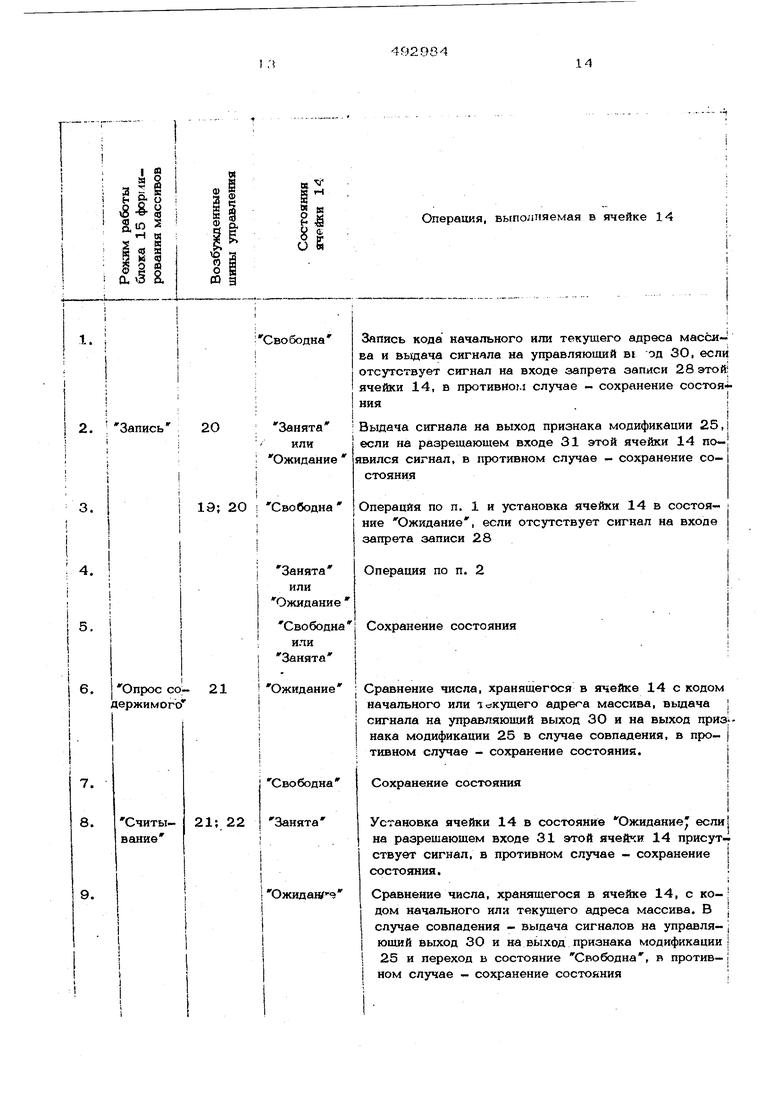

Для упрощения описания работы логического запоминающего устройства рассмотрим отдельно логику работы ячеек 14 блока 15. Он может работать в трех режимах: Запись, Считывание и Опрос содержимого (см. таблицу).

Каждая ячейка 14 может находиться в трех состояниях: Занята, Свободна и Ожидание.

При состоянии Занята в ячейке 14 записано отличное от нуля число. При состоянии Свободна в ячейке записан нуль. При состоянии Ожидание в ячейке записано отличное от нуля число и данная ячейка способна к возбуждению, если при работе блока 15 в режимах Считывание и Опрос содержимого код текущего ааjieiCa массива совпадает с кодом числа, хранящегося в ячейке 14.

Операции, выполняемые в ячейке 14 пр различных режимах работы блока 15, приведены в таблице.

Сигнал на выходе индикации состояния 27 любой из ячеек 14 присутствует в том случае, если ячейка 14 находится в состоянии Свободна.

Перед началом работы в логическом запоминающем устройстве для всех массивов формируются исходные текущие адреса записи и обработка массивов, их формирование происходит следующим образом. Перед началом работы все ячейки 14, регистр 12 и блок 13 устанавливаются в ну левое состояние,

В первом такте на входы 11 регистра адреса 12 от периферийных устройств поступает кол начального адреса массива и заносится в регистр 12, а по шинам упраления 24 во вто|;юй разряп блока 13 злмисывается единица.

Во втором такте на шину управления 23 поступает сигнал, переключающий рторук)

группу элементов И 16 в проводящее состояние и исходный текущий адрес записи или обработки массива, сформированный в регистре адреса 12 и блоке 13, заносится в регистр слова 18.

В третьем такте по шинам 33 произв одится сброс в нуль содержимого блока 13, если формируется исходный текущий «лрес обработки массива, либо сброс в нуль с записью единицы в первый разряд этого бло-

ка, если формируется исходный текущий адрес записи массива.

В четвертом такте на шины управле ния 19 и 20 поступают сигнат.1, которые настраивают одну из ячеек 14, находящихся в состояниях Свободны, на запись начального адреса записи либо начального адреса обработки, сформированного в предыдущем такте в регистре адреса 12 и в блоке 13. Если в состоянии Свободна находится несколько ячеек 14, то записать Код начального или текущего адреса сможет только ячейка 14 с наименьшим порЯдковык номером. Подобная зависимость

обеспечивается логикой работы ячеек 14 и системой подключения выходов индикации состояния 27 и входов запрета записи 28. Например, ели а ячейки 14 окажутся в состояниях Свободны, то произвести

запись сможет только первая ячейка 14, так как только на ее ьход запрета записи 28, подключенный к шине заземления 36, не будет поступат сигнал запрета.

В этом же такте подаются сигналы н«

шины управления 32, настраивающие адресный 5 и разрядный 6 блоки управлений на организацию записи содержимого регист-ра слова 18 в числовую линейку 2, соответствующую возбужденному управляющему

выход - ЗО.

В результате в одной из ячеек 14 будеТ записан код начального адреса записи или обработки. Эта ячейка перейдет в состояние Ожидание, а в соответствующей

числовой линейке 2 будет записан код исходного текущэго адреса записи или обработки.

В режиме обращения к текущему адресу работа логического запоминающего устрой-

ства происходит следующим образом.

В первом такте на входы 11 регистра адреса 12 подается код начального адреса массива и заносится в регистр, а блок 13 сигналами, поступающими по шинам 33 ничальной установки, либо устпнав.пи ается в нуль, если производится обращение к кущему адресу обработки, либо устанавл вается в пуль с эапясью единицы в перв разряд, если производится о дшение к т кушему адресу записи. В результате в р гистре адреса 12 и в блоке 13 будет С(| мировая начальный адрес обр аботки или ; писи. Во втором на шину управления поступает сигнал, по которому в ячейках яаходяшихся в состояниях Ожидание, п ИЗВОДИТСЯ операция по п. 6 (см. таблицу В этом же такте на шины управл( 3J подаются сигналы, производящие настрой |ку адресного 5 и разрядного 6 блоков : управления, организующих считьшание те кущвго адреса записи или обработки из числовой линейки 2, соответствующе й во бужденному выходу ЗО, т.е. управляющ. му выходу 30 той ячейки 14, содержимое которой совпало с иачагазным адре- ;сом записи или обработки. Результат сч {тывания поступает в выходной регистр На этом заканчивается работа устройств в «жнме обращения к текущему адресу. Р«;с лтуим работу логического запоминающего устройс- ва в режиме записи массивов информации. Будем считать, чт в накопителе 1 перед началом записи иь ются числовые линейкн 2, хранящие заш санную ранее информацию (%дем называть эти числовые линейки 2 занятыми) и, что ячейки 14, соответствующие заш тым числовым линейкам 2, находятся, в состояниях Заняты либо Ожидание, а остальные ячейки 14 - в состоянии Свободны. При работе устройства в р жиме записи массивов информации имею место три цикла (функционирования устрс ства: начальный, текущий, и конечный. Рассмотрим начальный цикл функцио рования устройства. В первом такте на шину управления поступает сигнал, разрешающий работу первой группы элементов И 10. В этом же такте по входным шинам в регистр слова 18 поступает первое слово подмассива записываемой информ цйи, а по входам 11, подключенным ч& рез открытые элементы И 1О, к вых ным шинам 9, в регистр адреса 12 и Е , блок 13 поступает считанный с выходи го регистра 8 код текущего адреса зап |си, занесенный .в выходной регистр 8 г окончании работы устройства в режиме обращение к текущему адресу. Во втором такте-на щиньг управления и 2О подаются сигналы, в соответствн : скоторыми в той ячейке 14, из числа J t находящихся в состояниях Свободны, которая, имеет наименьший порядковый но- мер, выполнится операция по п. 3 (см. таблицу). В этом же такте на шины управления 32 поступают сигналы, настраивающие адресный 5 я разрядный 6 блоки управления на выполнение операции записи содерхшмого регистра слова 18 в числовую линейку 2, соответствующую возбужденному управляющему выходу ЗО. С него сигнал поступает также на разрешающий вход 31 последующей ячейки 14, в которой выполняется операция по п. 4, если эта ячейка 14 находится в состс нии Занята или Ожидание. Если же последующая ячейка 14 находится в состоянии Свободна, то она сохранит свое состояние, так как сигнал на ее входе запрета записи 28, подключенном к выходу индикации состояния 27 ячейки 14, записавшей коп текущего адреса записи, исчезнет только по окончаний второго теиста. Результатом начального цикла является з 1пись первого слова записываемого подмассива информации в одну из числовых линеек 2, запись текущего вдреса записи массива в соответствующую этой числовой линейке 2 ячейку 14, установка этой ячейки 14 в состояние Ожидание и формирование на шине индикашш 26 сигнала в случае, если последующая ячейка 14 находится в состоянии Занята или Ожидание. За начальным циклом функционирования устройства в режиме записи следуют теку- шие циклы по числу оставшихся слов в записываемом подмассиве. Работа устройства в текущем цикле осуществляется следующим образом. В первом такте по входным шинам 17 .в регистр слова 18 заносится очередное слово записываемого подмассива, а по шинам управления 24 на счетный вход второго разряда блока 13 поступает сигналг увеличивающий текущий адрес записи на единицу второго разряда, если в последнем такте предыдущего начального или текущего цикла был сформирован сигнал на шине индикации 26, в противном случае текущий адрес записи остается без изм&нения. В этом же такте на шину управления 21 подае1ся сигнал, переводяшлй блок формирования массивов 15 в режим Опрос содержимого , и в ячейках 14 выполняются операции по пп. 5 .и 6 (см. таблицу). Опрос содержимого ячеек 14 производится для того, чтобы выявить возможное совпадение текущих адресов записи одного и того же массива при переполне|ыии блока 13. В этом спучаё, появление сигнала на шине индикации 26 говорит о том, что необходимо либо вывести из нэкопителя часть записываемого массива, либо приступить к его обработке. j Второй такт протекает аналогично вто|рому такту начального цикла, если во вто 1 ром такте предыдущего цикла на шкне ин днкации 26 был сформулирован сигнал, в ;противном случае во втором такте сигналы подаются не по шинам управления 19, 2О и 32, а только по шинам управлвв ния 20 и 32. Вследствие этого в ячейках 14 будут выполняться операции по пп. 1 и 2 (см. таблицу). В результате выполнения текущего цикла функционирования устройства в режиме записи осуществляется запись очередного слова записываемого подмассива в одну из числовых лкнеек 2, запись текущего адреса записи массива в соответствуюшую этой числовой ячейке 2 ячейку 14, перевод этой ячейки в состояние Ожидание или Занята в зависимости JT того, был ли сформирован во втором такте предьщушего цикла сигнал на шине индикации 26 или нет, и формирование на шине индикации 26 сигнала в случае, если последующая ячейка 14 находится в состоянии Ожидание или Занята. После записи последнего слова подмес- сива следует конечный цикл функционирования устройства в режиме записи. В первом такте по шинам 24 во второ разряд-блока 13 заносится единица, что увеличивает текущий адрес записи массива на единицу второго разряда. Второй, третий и четвертый такты протекают аналогично второму, третьему и четвертому тактам работы устройства при формировании исходных текущих адресов записи или обработки. По завершении конечного цикла записываемый подмассив информации окажется распределенным произвольным образом по ранее свободным числовым линейкам 2 накопителя логического запоминающего устройства, а в ойной из числовых линеэк 2 будет записан код текущего адреса записи Следует отметить, что, если часть маю- сива записана в следующих друг з другом числовых линейках 2, то в соответствующих им ячейках 14 будут записаны одинаковые текущие адреса и эти ячейки будут находиться в состояниях Занять , кроме той нз них, которая имеет младший 11оряяковый номер. Эта ячейка будет находиться в состоянии Ожидание, Если в режиме записи массиве информации все числовые линеГдси 2 окажу11 зя занятыми, то на шине 29 индикации состояния накопителя, подключенной к выходам индикации состояния 27 ячеек 14, сигнал будет отсутствовать, что .лужит признаком прекращения работы в режиме записи массивов информации. Работа логического запоминающего ycTv ройства в режиме логической обработки массивов информации осуществляется сл&дующим образом. При работе устройства в этом режиме азличаются три цикла функционирования: н&ч чальный, текущий и конечный. Существует три вида логической обработки; массив - массив (последовательно по словам), маесив - слово (последовательно по словам) и массив - слово (параллельно по словам). Рассмотрим работу логического запоми нающего устройства в режиме логической обработки вида массив - массив (последовательно по словам). Будем полагать, что один из обрабаты- ваек4ых массивов информации распределен произвольным образом по числовым 2 накопителя, а второй массив ннфо1 мации поступает извне -последоьательно по словам на регистр слова 18. Б первом тахте начатьного цикла на щину управления 34 подается сигнал, разрешающий работу элементов И 10. По входным шинам 17 в регистр слова 18 поступает первое слово второго 1 йСсйва, а по входам 11 черев элементы И 10 в регистр адреса 12 н в блок 13 посту- пает считанный с выходного регистра 8 код текущего адреса обработка, занесе ный в этот регистр по окончании работы устройства в режиме обращения к техущр му адресу. Во втором такте поступают сигналы на шины управления 21 и 22, в соответст ааий с которыми в ячейках 14, находящихся в состояниях Ожидание, выполняется операция по п. S (см. таблицу). Отсутствне сигнала на щяне нндикации 26 указь вает на то, что в накопителе отсутствует массив информации, имеющий начальный адрес, записанный в регистр адреса 12. В этом случае устройство прекращает логическую обработку заданных массивов информации, В 9ТОМ же те&те на шины управления 32 подаются еЯР 1впь1, настраивающие адреоНЫЙ 5 и ра |рЯ }|Ь1Й О блоки управления на вьшолкев 1е в «(гдаловой линейке 2 соответ ствующей возбужденному упраэлякяце лу ЕЬ ходу 30 зй13АНШ Л операюти над содержимым этой чйюдяовой линейки 2 н солержи- мым регистс 31 слова 18.Результат операil

ции либо остается в этой числовой лине - ке 2, либо поступает на выходнь;е шины Э. Кроме того, сигнал с возбужденного упр laляюшего выхода ЗО поступает и на раэр шакший вход 31 последующей ячейки 14 , в которой выполняется операция по п. 8 (см. таблицу).

Результатом uratiia являет :я выполнение операция над первыми словак и обрабатываемых массивов информации и leревод последующей ячейки 14 в состояш е Ожидание, если она находится в COCTOJ НИИ Занята. Если же последующая ячей ка 14 находится в состоянии Свободна или Ожиданче, то состояние этой ячейки 14 сохраняете.

По окончании начального цикла следу т текущие циклы функционирования устройс ва в режиме логической обработки масси.

ВОВ.

В первом такте текущего цикла под ются сигналы на щину управления 21, и блок формиро1вания массивов 15 г в режим бпрюс с одержйШго 7 в ячейках 14 находящихся в состоянии Ожидание, выполняется операция по П.6 (см. таблицу). Появление сигнала на шине индикации 26 указывает на то, что по данному текущек f адресу можно производить логическую обьработку, а отсутствие сигнала - на необх - димость увеличения текущего адреса обр& ботки. В этом же такте в регистр слова 1 В заносится очередное слоРо второго массив а

Во втором такте содержимое блока 13 либо остается неизменным, либо увеличив етсТ на единицу второго разряда сигналам i, поступающими по шинам управления 24 в зависимости от того, присутствовал или нет в первом такте сигнал на шине индик ции 26.

В остальном второй такт протекает аи. логично второму такту начального цикла функционирования устройства в режиме лог i ческой обработки. Отсутствие сигнала на шине индикации 26 по окончапии второго такта говорит о том, что масрив инфорМа.ции, хранящийся в накопителе, обработан полностью.

Переход к конечному циклу осуществляется в двух случаях: либо кончился массив, поступающий на регистр слова, либо закончилась обработка массива, хранящегося в накопителе.

1

12

В первом случае функционированир ус i ройства протекает аналогично кор чному циклу режима записи массивов информации, а во втором случае в первом такте по щинам 33 производится начальная установка блока 13 в нуль. Во втором такте управляющие сигналы подаются по щинам управления 24 и производят запись единицы во второй разряд блска 13.

В третьем такте по шине управления 2 3 поступает сигнал, переводящий вторую группу элементов И- 16 в открытое состояние, и исходный текущий адрес, сфор, мированный во втором такте, поступает из ретнстра адреса 12 и блока 13 в регистр слова 18.

В четвертом такте по шинам 33 производится установка блока 13 в нуль. Одновременно на щину управления 21 подается сигнал, настраивакяций блок формирования массивов 15 на Опрос содержимого, в ячейках 14 которого выполняется операция по п.6 {см. таблицу).

В этом же такте на шины управления 32 подаются сигналы, в соответствие с которыми в числовой линейке 2, хранившей ранее текущий адрес обработки, записывается исходный текущий адрес, находящийся в регистре слова 18.

Аналогичным образом происходит логическая обработка массивов вида массив - слово (последовательно по словам). Однако в этом случае в регистре слова 18 постоянно хранится одно и то же слово, участвующее в логическом обработке массива, записанного в накопитель.

При организации логической обработки вида массив - слово (параллельно по словам) необходшио, чтобы в текущем цикле при функционировании устройства в режиме записи управляющие сигналы во втором такте постоянно подавались по шинам управления 19, 2О и 32. В результате все ячейки 14, в которых записан текущий алрес массива, окажутся в состоянии Ожидание, Кроме того, при записи массива остается неизменный текущий адрес. При этом будет производиться одновременная логическая о аботка всех слов массива, хранящегося в накопителе.

Операция, выполняемая в ячейке 14

Запись кода начального или текущего адреса массива и вьщача сигнала на управляющий В1 од 30, если отсутствует сигнал на входе запрета записи 28 этой| ячейки 14, в противном случае - сохранение состоя ния

Вьщача сигнала на выход признака модификации 25, | если на разрешающем входе 31 этой ячейки 14 по-; явился сигнал/в противном случае - сохранение состояния

Операция по п. 1 и установка ячейки 14 в состояние Ожидание, если отсутствует сигнал на входе запрета записи 28

Операция по п. 2

Сохранение состояния

Сравнение числа, хранящегося в ячейке 14 с кодом начального или itsKymero адреса массива, выдача сигнала на управляющий выход 30 и на выход приз нака модификации 25 в случае совпадения, в про- j тивном случае - сохранение состояния.j

Сохранение состояния;

Установка ячейки 14 в состояние ОжиданиеJ если на раарешаюшем входе 31 этой ячейки 14 присутствует сигнал, в противном случае - сохранение { состояния.i

Сравнение числа, храшпцегося в ячейке 14, с кодом начального или текущего адреса массива. В случае совпадения - выдача сигналов на управляющий выход 30 и на выход признака модификации 25 и переход в состояние Свободна, в противном случае - сохранение состояния П р е д м е т и а о б р f т р и и я Лотическое запоминающее устройство, содержащее 4HcJj5i6ltie линейки, разрядные шины которых подключены к выходам раэ рядного блока управления, линейные шиньь. к выходам адресного блока, гпраэления, шины чтения - ко вхоДак ВБОсодногЬ регистра выходы которого соединены со входами элементов И первой группы, регистр сло ва, входы которого подключены к выходам элементов второй группы, а выходь ко входам разрядного блока управления, управляющие шины, шины индикации и шины начальной установки, отличаю ше - 4 е с я тем, что, с целью расширения циональных возможностей, оно содержип блок модификации адреса и блок фбрмировя ния массивов, входы которого подключены к выходам регистра адреса и блока модификации адреса, соединенным со входами элементов И второй группы, а выходы соответственно ко входам адресного блока управления н шинам индикации, выходы элементов -W первой группьг подключены ко входам регистра адреса и одним входам бпока моаи {япса1Ьга адреса, другие входы Которого соединены соответственно с управляющими шинами и шинами начальной установки. I

Г

-N

п

«а -V

Авторы

Даты

1975-11-25—Публикация

1974-04-01—Подача