Изобретение относится к области вычиспитепьной техники и может быть использовано гфи построении устройств хранения и переработки дискретной и фopмaци По основному авт. св. № 649О37 известно логическое запоминающее устрой ство, содержащее группы одноразрядных блоков памяти, управляющие блоки памяти и шины группсеого стробирования по чисяу групп одноразрядных блоков памяти, подключённые к стробирующим входам одноразрядных блоков памяти и к стробирук щему входу управляющего блока памяти соответствующей групш 1, шину общего стробирования, .соединенную со стробирующими входами одноразрядных блоков памяти, информационные входы и выходы которых соединены соответственно с выходами входного и со входами выходного регистров, управляющую щину стробирюва- кия, подключекную к стробируюшнм входам управляющих блоков памяти, щцну ввода константы и илгау индикации, соединенные соответственно с информационными входа- МИ управляющих блоков памяти и с информационным выходом управлякяцачэ блока nastHTji последней группы, шину признака гр тшового стробировашш, подключенную к шине группового стробирования первой груп-; пы блоков памяти, первый адресные ишны и шину записи, соединенные соответствекно с адресными входами и со входами записи всех одноразрядных и управляющих блоков памяти, шину считывания, подключенную ко входам считывания одноразрядных блоков памяти и ко входам записи управляющих блоксж памяти, шину опроса, соединенную со входами считьюания управляющих блоков памяти, информационные выходы каждого КЗ которых, кроме последнего, подключены к шине группсеого стробирования последующей группы 1 . Недостатка, известного устройства явттяется низкое быстродействие, обусловленное отсутствием возможности совмещения процессов приема, буферизации, выдачи и обработки иаЬормации.

Цель изобретения - повышение быстродействия логического запоминающего устройсша.

Поставленная цель достигается тем, что устройство содержит переключатель адресных шин, дешифратор адреса и блоки памяти магазинного типа по числу адресов одноразрядных блоков памяти, первые и вторые адресные, входы переключателя адресных шин подключены соответственно к первым и вторым адресным шинам устройства, управляющий вход и выходы - соответственно к шине выбора адреса и ко входам дешифратора адреса, управляющий вход которого соединен с шиной управления дешифратором, каждый выход дешифратора адреса подключен к управляющим входам регистров соответствующего блока памяти магазинного типа, информационные входы первых и информационные выходы последних регистров каждого блока памяти магазинного типа подключены соответственно к выходам выдачи слова выходного и ко входам приема слова входного регистргав.

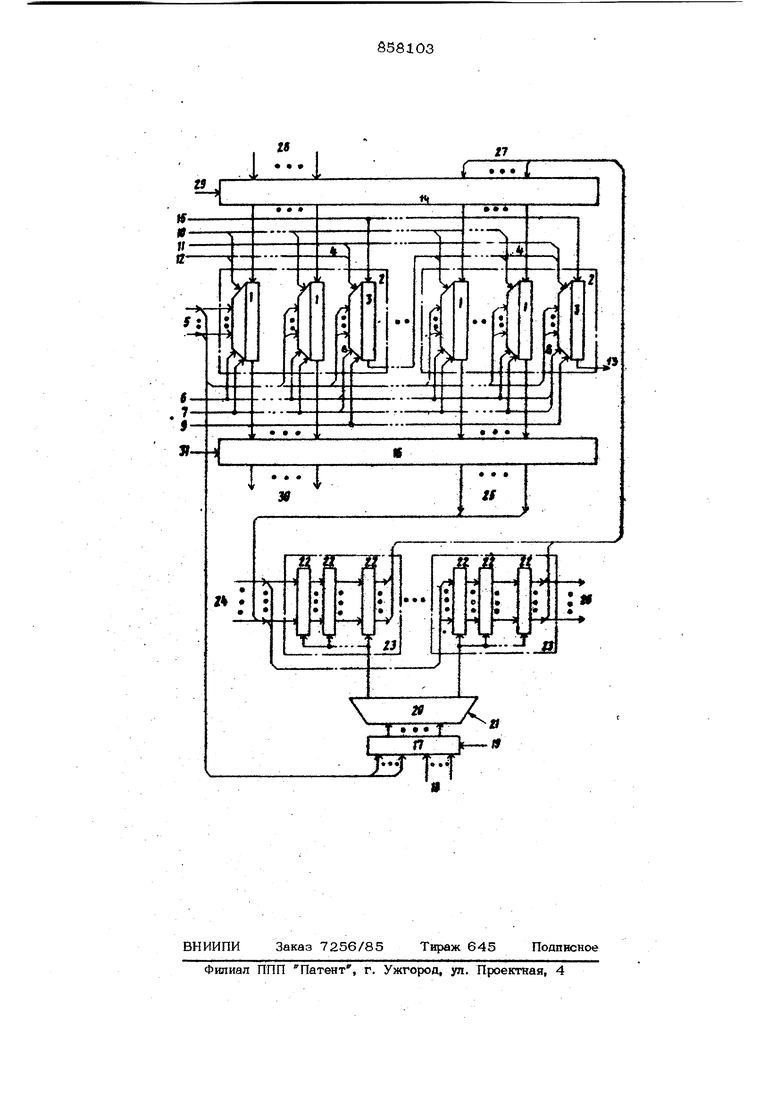

На чертеже приведена cx«via предложенного устройства.

Устройство содержит одноразрядные блоки 1 памяти, объединенные в группы 2 каждая из которых содержит управляющий блок 3 памяти, шину 4 группового стробирования. Адресные входы блоке 1 и 3 памяти подключены к первым адресным шинам 5, Входы записи и считывания блоков 1 памяти соединены с одноименными шинами записи 6 и считывания 7, а вход 8 записи блоков 3 памяти подключен как к шине 6 записи, так и к шине 7 считывания. Входы 8 считывания всех блоке памяти соединены с шиной 9 опроса. Стробирующие входы блоков 1 памяти каждой из групп 2 подключены к шине 10 общего стробирования, а стробируклпий вход каждого блока 3 памяти соединен с соответствующей шиной 4 группсеого стробиршания и с управляющей шиной И стробирования. Шина 4 группового стробирсжания первой группы 2 подключена к шине 12 признака группового стробирсеания, а информационный выход блока 3 последней группы 2 соединен с шиной 13 индикации.

Информационные входы блок(ж 1 памяти подключены к информационным выходам входного регистра 14, информацио ные входы блоков 3 памяти - к шине 15 ввода константы, а информационные выходы блоков 1 памяти соединены с информационными входами выходного регистра 1

В состав устройства входит также переключатель 17 адресных шив, подключенный к первым 5, ко вторым 18 адресным шинам и к шине 19 выбора адреса. Выходы переключателя адресных шин соединены со входами дешифратора 2О адреса, управляющий вход которого подключен к шине 21 управления дешифратором, а выходы - к управляющим входам регистров 22 соответствующего блока 23 памяти магазинного типа. Информационные входы всех, кроме первых регистров

22блоков 23 памяти магазинного типа, соединены с информационными выходами предыдущих регистров. Информационные входы первых регистров 22 блоков 23 памяти подключены к шинам 24 приема слова и к выходам 25 выдачи снова выходного регистра 16. Информационные выходы последних регистров 22 блоков

23памяти подключены к шинам 26 выдачи слева и ко входам 27 приема слева входного регистра 14. Входы приема байта и управляющий вход входного регистра 14 соединены с шинами 28 приема байта и с управляющей шиной 29 байтового прий,1а соответственно. Выходы выдачи байта и управляющий вход выходного регист ра 16 подключень соответственно к шинам

30выдачи байта и к управттяющей шине

31байтсжой выдачи.

Считаем, что до начала работы во всех ячейках блоков 3 памяти записаны нули. Выполнение операций записи или считывания в блоках 1 и 3 памяти происходит только в том случае, если они находятся в активном состоянии. Переход каждого из блоков 1 и 3 в активное состояние осуществляется по сигналу, поступающему на стробирующий вход этих блоке. После выполнения операций записи или считывания блоки 1 и 3 памяти переходят в пассивное сеютояние.

Регистры 22 блоков 23 памяти при низком уровне напряжения на irx управляющих входах находятся в состоянии выдачи информации, а при высоком напряжения - в состоянии информации, .причал, время сохранения информации на выходах регистров 22 при смене уровня напряжения на их управляющих входах с низкого на высокий больше времени записи входной информации.

В каждой числовой линейке одноразрядных блоков 1 памяти операции приема или выдачи байта возможны в тех байтовых группах 2, в соответствующих ячейках которых управляющих блоков 3 памяти записан признак обработки байта, например логическая единица. Организуя последовательную перезапись единицы из одной ячейки памяти блоков 3 памяти в другую в какой-либо числовой линейке можно управлять выдачей или записью последовательно следующих байтов ин- формации, что эквивалентно расформиров нию на байты или формированию из байто полноформатного информационного слова. Предложенное устройство имеет четыр режима работы: режим формирования слов режим расформирования слова, режим при ема слова и режим выдачи слова. Каждый из первых двух режимов может быть совмешен во времени с последними двумя режимами. В режиме формирования слова устройс-гео работает следующим образом. В первом такте на шину 12 признака группового стробирования поступает сигнал, активизирующий числовую линейку в блоках 1 и 3 памяти группы 2, соогаер ствующую коду адреса, присутствующему на первых адресных шинах 5. В этом же такте по сигналу на управляющей шине 29 байтового приема записывается байт информации, присутствующий на шинах 28 байтового приема, в соответствующие инфс мационным входам каждой группы 2 разрядь входного регистра 14. Во втором такте по сигналу на шине 6 записи осуществляется запись байта информации из входного регистра в ячейки одноразрядных блоксж памяти первой группы 2, соответствующие коду адреса на первых адресных шинах 5. Одновреме но в той же числовой линейка производить ся запись логической единицы в ячейку управляющего блока 3 памяти, поступающей на его информационный вход с шины ввода константы. В третьем такте по сигналам на управляющей шине 11 стробирования и шине 9 опроса осущес.твляется опрос содержимого управляющих блоков 3 памяти. Считывание информации из управляющих блоков 3 памяти при этом производится с разрушениет г. Считанный сигнал поступает на шину 4 группового стробирсеания последующей гfyппы 2 блоков памяти. В дальнейшем в режиме формирования слова данные три такта псеторяются при записи очередного байта информации до тех пор, пока после очередного третьего такта на шине 13 индикации не появится сигнал, готорый говорит о том, что полноформатное слово в выбранной числовой линейке одноразрядных блоков 1 памят1т сформировано. Тогда в четвертом такте данного режима стробирующие входы всех одноразр5ащных блоков 1 памяти по шине общего стробирования поступает сигнал, активизирующий в них ячейки памяти выбранной числшой линейки. В этом же такте по сигналу на шине 19 выбора адреса переключателя 17 адресных шин на входы дешифратора 2О адреса поступает код адреса с первых адресных шин 5. В пятсм такте на шину 21 управления дешифратором 20 поступает сигнал, по которому на одном из его выходсж появтгается сигнал, активизирующий блок 23 памяти магазинного типа, соответствующий выбранной в одноразряднь1х блоках 1 памя - ти числовой линейке . В этом же такте по сигналу на шине 7 считывания полноформатное информационное слово через выходной репютр 16 поступает на информационные входы первого регистра 22 выбранного блока 23 памяти магазинного типа. В этом же такте по сигналу, поступающему с выхода дешя} ратора 2О адреса на управляющие входы регистров 22, происходит сдвиг информации в направлении от первого регистра к последн&лу. При этом сформированное в данном режиме полноформатное слово записывается в пердаый регистр, содержимое первого регистра переписывается во второй регистр, второго - в третий и т.д. с последнего регистра 22 поступает на шины 26 выдачи слова. На этo режим ормирования слова заканчивается. В режиме расформирования слова устройство работает следующим образом. В первом такте по сигналам на шине 19 выбора адреса и шине 21 управления дешифратором на одном из вы содсю деш1фратора 20 пояиаляется сигнал, соответстующий коду адреса на первых адресных инах 5, по которому осуществляется двиг информации в выбранном блоке 23 амяти магазинного типа. При этом инфор 4 ационное слово вз последнего регистра 22 перепнсьшается во входной регистр 14. этом же такте на шину 1О общего тробирования поступает сигнал, активиирующий одноразрядные блоки 1 памяти. Во втором такте по сигналу на шине записи полноформатное слово из входого регистра 14 переписывается в сответстаующую коду адреса на первых дресных шинах 5 числовую линейку ОДЕЮазрядкых блоков 1 памяти. 85 В третьем такте на шину 12 признака группового стробирования поступает сигнал активизирующий числовую линейку в блоках 1 и 3 памяти группы 2, соответствующий коду адреса, присутствующему на первых адресных шинах 5. Четвертый и пятый такт режима расформирования слова аналогичны соответ ственно второму н третьему тактам режима формирежания слова. Отличие соетоит в TGM, что в четвертом такте сигнал поступает не на шину 6 записи, а на шину 7 считывания. В результате по сигналу на шине 31 байтовой выдачи байт информации считывается в выходной регистр 16 и поступает на шины 30 выдачи байта. В режиме приема слова устройство работает следующим образом. Переключатель адресных шин 17 по соответствующэчту сигналу на шине 19 выбора .адреса передает на входы дешифратора 20 адреса код адреса со вторых адресных шин 18. По сигналу на шин 21управления деши||ратором 20 на одном на его выходов появляется сигнал, по кото- рому осуществляется запись полноформат ного слова с шин 24 приема слова и одновременный сдвиг ннформащт в регистра 22выбранного блока 23 памяти магазинного Tjma. Затем сигнал на управляющем входе 21 дешифратора 20 снимается. Подавая на вход 21 управления дешнфраторсл 2О требуемое число сигналсж запнсьтают в выбранный блок 23 памяти магазинного типа соответствующее количество попнофор матных спов, предназначенных для расформирования на байты. Б режкме выдачи слова устройство работает аналогично. Отличие состоит в том., что выдаваемые с последнего регистра 22 выбранного блока 23 магазинного типа сформированные ранее слова посту пают к пользователю на шины 26 выдачи спова. Решгмы выдачи сформированных слсж и приема слов для расформирования, на байты могут выполняться одновременно. Кроме TorOj введенные отличительные 3 признаки позволяют организовать параллель, ную работу устройства в режимах формирсюания или расформирования слов в одноразрядных блоках 1 памяти и приема и i выдачи полноформатных слов в блоках 23 памяти магазинного типа. Это позволяет при обмене массивами слов между устрой. ством и множеством пользсеателей уменьшить потери времени на вхождение в связь и выхождение из свякэи в п раз, где п число регистров в каждом из блоков 23 К1агазинного типа. Полученный выигрыш во времени прямопропорционален числу регистров в блоках 23 памяти магазинного типа, максимальная величина которых определяется количеством слов, которое за один прием может обработать пользователь. Формула изобретения Логическое запоминающее устройство по авт.св. № 649037, отличающееся тем, что, с целью псеышения быстродействия устройства, оно содержит переключатель адресных шин, дешифратор адреса и блоки памяти магазинного типа по числу адресов одноразрядных блоков памяти, первые и вторые адресные входы переключателя адресных шин подключе 1Ы соответственно к первым и вторым адресным шинам устройства, управляющий вход и выходы - соответственно к шине выбора адреса и ко входам деши:})ратора адреса, управляющий вход которого соединен с шиной управления дешифраторе, каждый вход дешифратора адреса подключен к управляющим входам регистре соответствующего блока памяти магазинного типа, а информационные входы первых и информационные выходы последнтпс регистре каждого блока памяти магазинного типа подключены соответственно к выходам выдачи слсжа выходного и ко входам приала слова входного регистров. Источники информаюш, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 649037 кл. q 11 С 15/00.,

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1975 |

|

SU649037A1 |

| Логическое запоминающее устройство | 1980 |

|

SU947910A2 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1989 |

|

SU1689961A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1508225A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

Авторы

Даты

1981-08-23—Публикация

1979-11-02—Подача