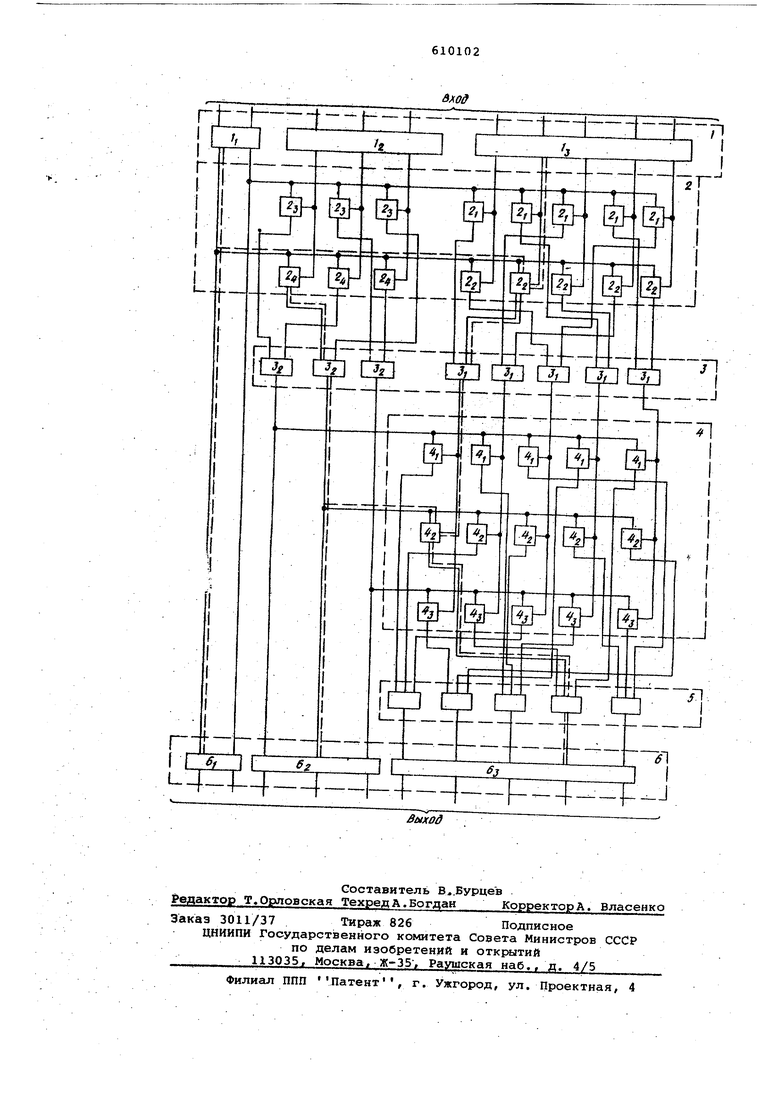

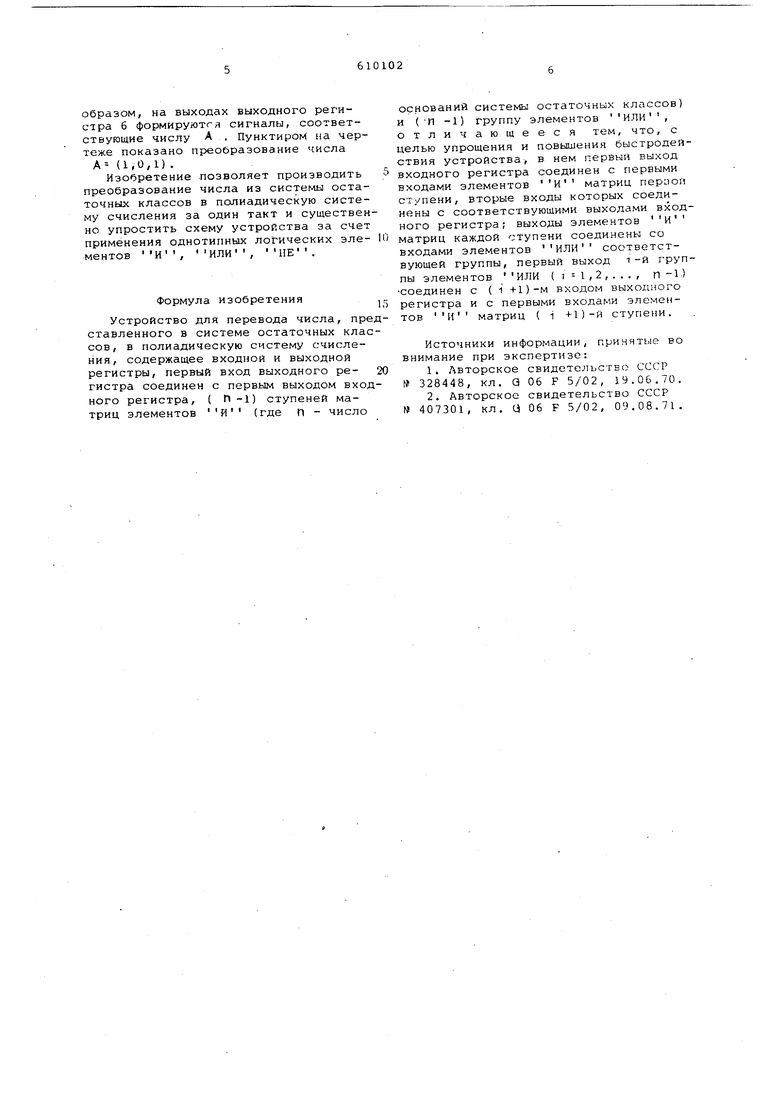

адическую систему счисления, состо щего из трех оснований , Рз5. Схема содержит входной регистр состоящий из входных регистров каждому основанию, матрицу 2 эл тов И первой ступени, состоящу из элементов И 2 - 2., первую пу 3 элементов ИЛИ, состоящую элементов ИЛИ 3, матрицу элементов И второй ступени, со тоящую из элементов И 4, рую группу 5 элементов ИЛИ , вы . ой регистр 6, состоящий из регист S- ЬУстройство реализует перевод чи следующим образом. Любое число в полиадической сис ме счисления может быть представле Q виде P.aaPvPj - anPvPi-Prvf , где , основания полиадиче ской системы счисления; - «а V ( , 2,, .., П) - коэффициен Пусть А :(Л, ,л,,...сЛ. „) - представление числа в системе остаточных к сов с основаниями Р,, п чем PI PZ--- п Тогда а, Amod Р, , где Для вычисления значения а необ ходимо найти величину СП - i-rtiod P,j ( j 2,3,. ..,« где оС , sр- т.е. О oL . Для вычисления значения а необх димо найти величину где с. 1 S mod Р : U i,4,...,n), 2 т.е. с Аналогично и далее. Для вычислени значения «„. необходимо найти велиП-З Л-2 ) . (n-i) / (n-ilЧ . ). (п-zl где Г ( 9 п--(,п ), . Для вычисления значения необх димо найти величину 1ПН1 А„., рЛ„ , где ,оар„. т.е. Устройство работает следующим образом. Код числа А , которое необходимо предстабить в полиадической системе счисления, при.нимается на входной регистр 1. Во входных регистрах Ij по каждому основанию представлены остатки (Л. , d. 2 ri Л числа А по модулям , , Рз 5. Сигнал с первого выхода входного регистра 1 подается на первый вход выходного регистра б и на один из входов элементов И 24.матрицы 2 элемей.ов И первой ступени. На вторые вхоДЬ элементов И 2 подаются сигналы, соответствующие остаткам по Основаниям Р и Р, со второго и Третьего выходов входного регистра 1 . Аналогично, в случае преобразования числа по 1 -основаниям на один из входов элементов И j подается сигнал, соответствующий остатку по основанию Р , а на вторые входы - сигналы по основаниям Pj ( ,3,...,M 1 . 0,1,..., Р-Д ; 1,2,..., ) . Каждому элементу соответствующему матрице 2 элементов И первой ступени, приписываются значения результатов (а. - Л )mod , которые с матрицы 2 выходов элементов элементов И первой ступени поступают на входы первой группы 3 элементов ИЛИ. Каждому элементу ИЛИ у3, ЗУ первой группы элементов ИЛИ приписываются значения результатов а . - 01. (1) -1 -i-mod Рз-«2Для основания 2 Выходные сигналы элементов ИЛИ 3 , соответствующие 3Начения|м результатов сХ. 2 , поступают на второй вход ыходного регистра 6 и на один из вхоов элементов И. матрицы 4 элевторой ступени. На втоентов U 4 - 4 ые входы элементов И ч оступают сигналы с выхода элементов ИЛИ,- 3. Каждому элементу И.,-,- 4 риписываются значения результатов (.)п1о(3 PJ , которые с их выходов оступают на вход второй группы 5 элеентов ИЛИ . Каждому элементу ИЛИ.- второй руппы 5 элементов ИЛИ приписыаются значения результатов (a,-a)modPj . Выходные сигналы второй группы элеентов ИЛИ 5, соответствующие знаению результата а, поступают на треий вход выходного регистра-6. Таким

образом, на выходах выходного регистра 6 формируются сигналы, соответствующие числу А . Пунктиром на чертеже показано преобразование числа

АМ1,0,1) .

Изобретение позволяет производить преобразование числа из система остаточных классов в полиадическую систему счисления за один такт и существенно упростить схему устройства за счет применения однотипных логических злементов И, ИЛИ, НЕ.

Формула изобретения ...

Устройство для перевода числа, представленного в системе остаточных классов, в полиадическую систему счисления, содержащее входной и выходной регистры, первый вход выходного ре- 20 гистра соединен с первым выходом входного регистра, ( П-1) ступеней маИ

(где П - число

триц элементов

оснований системы остаточных классов) и (И -1) группу элементов ИЛИ, отличающееся тем, что, с целью упрощения и повышения быстродействия устройства, в нем первый выход входного регистра соединен с первыми входами элементов И матриц перпои ступени, вторые входы которых соединены с соответствующими выходами входИ

ного регистра; выходы элементов

матриц каждой ступени соединены со входами элементов ИЛИ соответствующей группы, первый выход i-и группы элементов ИЛИ (,2,..., п-1) соединен с ( 1 +1)-м входом выходного регистра и с первыми входами элемен

матриц ( i +1)-й ступени.

тов

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР

№ 328448, кл, Q 06 F 5/02, 19.06.70.

2.Авторское свидетельство СССР

407301, кл, U 06 F 5/02, 09.08.71.

Г

fl

бГ

L.

&

Т-1-- -4- -J

Авторы

Даты

1978-06-05—Публикация

1975-12-29—Подача