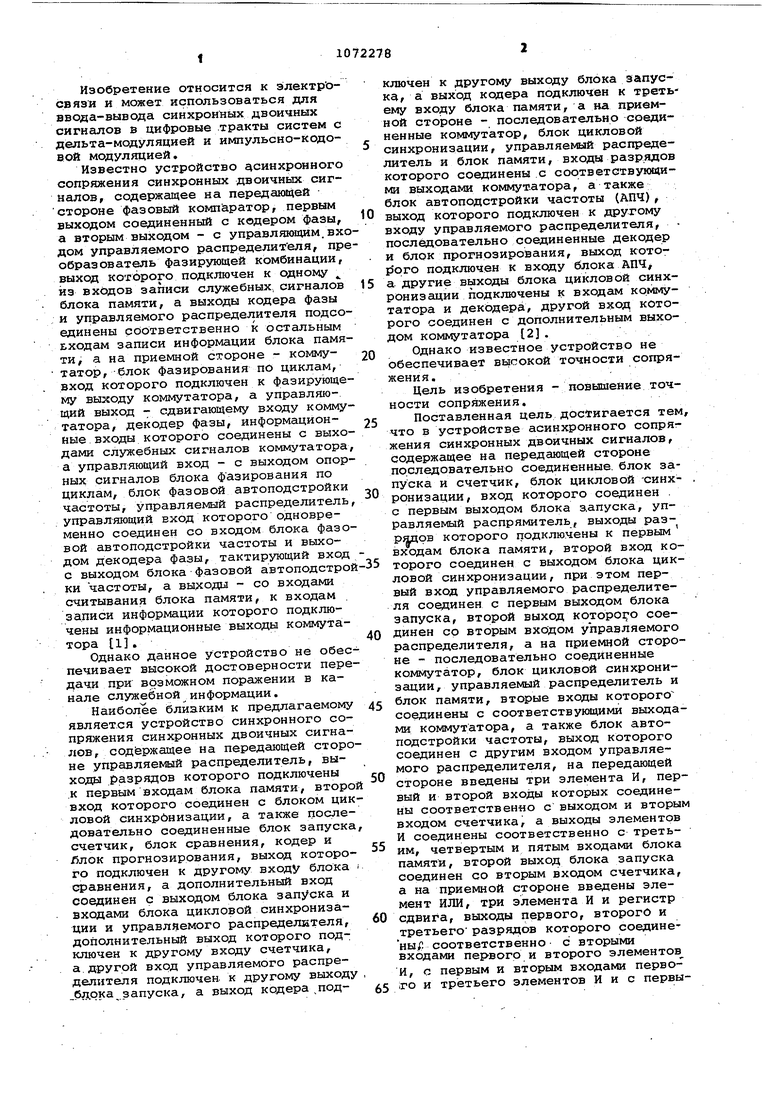

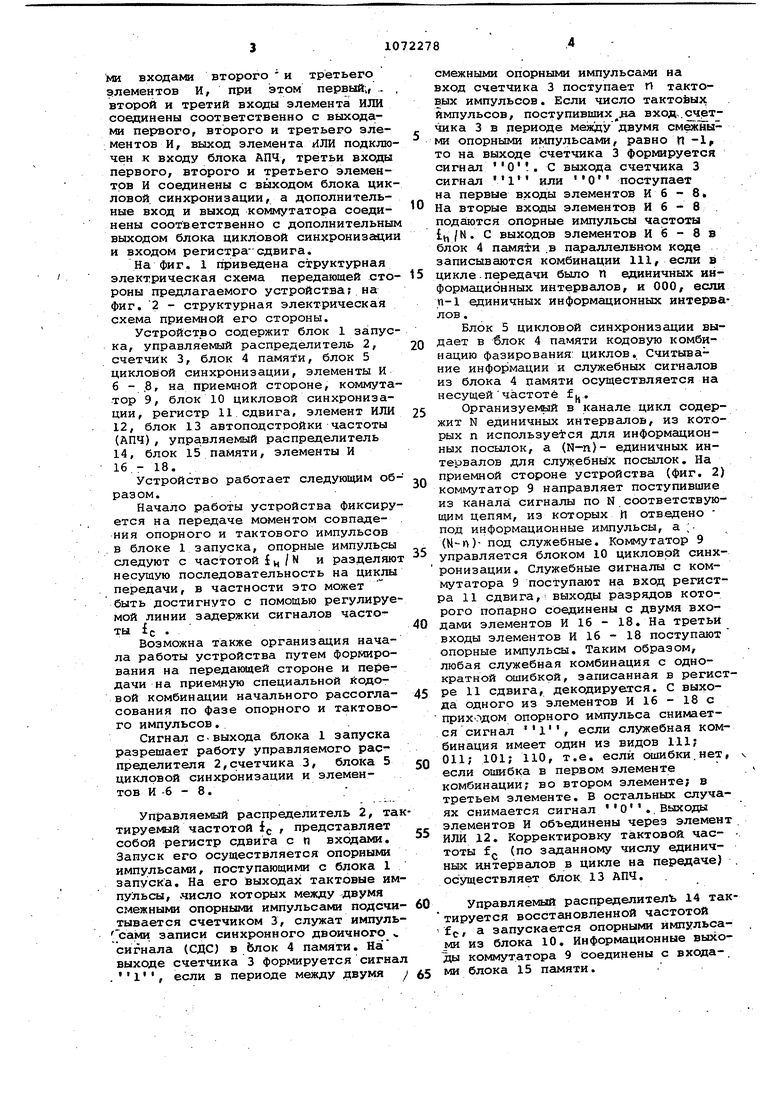

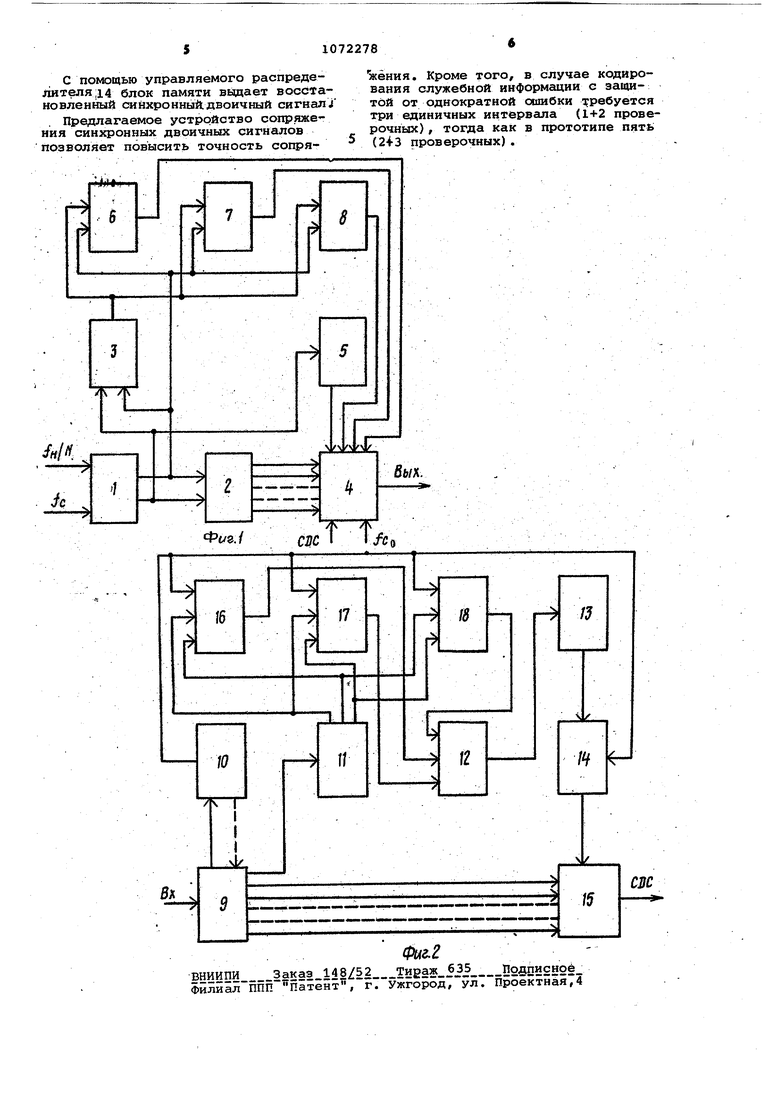

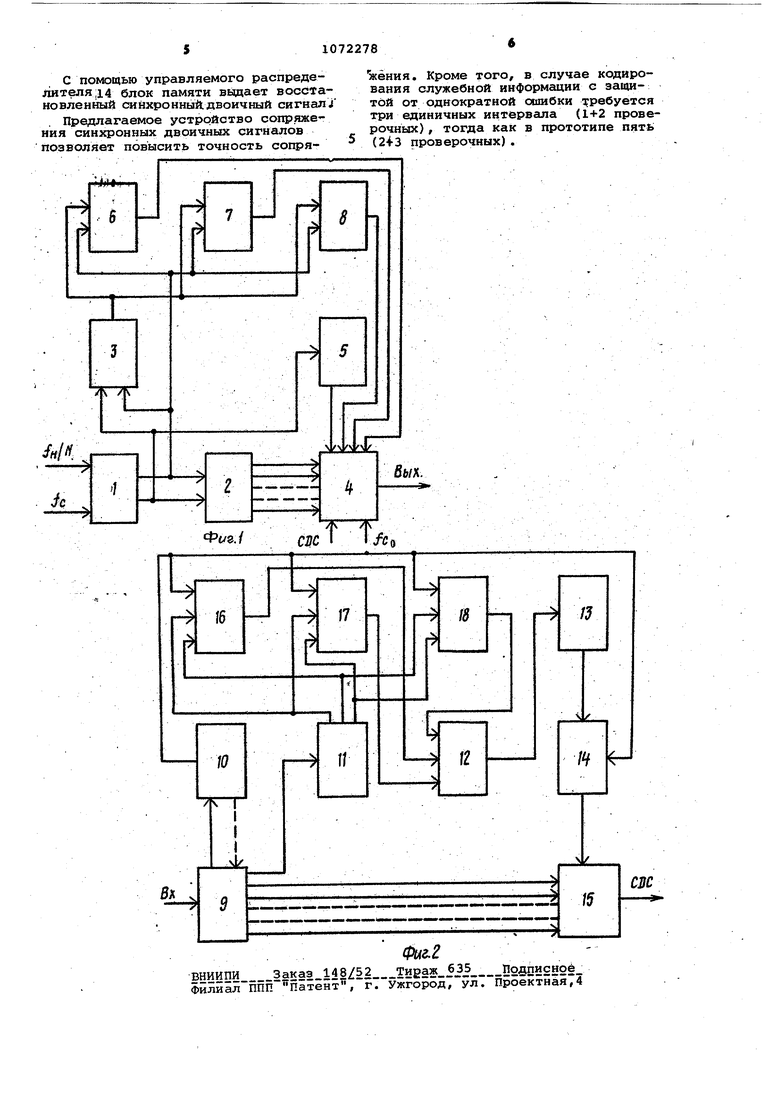

Изобретение относится к электросвязи и может использоваться для ввода-вывода си и хронных двоичных сигналов в цифровые тракты систем с дельта-модуляцией и импульсно-кодовой модуляцией. Известно устройство синхронного сопряжения синхронных двоичных сигналов, содержащее на передающей стороне фазовый комп&ратор, первым выходом соединенный с кодером фазы, а вторым выходом - с управляющим.вх дом управляемого распределителя, пр образОватель фазирующей комбинации, выход которого подключен к одному из входов записи служебных, сигналов блока памяти, а выходы кодера фазы и управляемого распределителя подсо единены соответственно к остальным Бходам записи информации блока памя ти, а на приемной стороне - комму татор, блок фазирования по циклам, вход которого подключен к фазирующе му выходу коммутатора, а управляющий выход - сдвигающему входу комму татора, декодер фазы, информационные входы которого соединены с выхо дами служебных сигналов коммутатора а управляющий вход - с выходом опор ных сигналов блока фазирования по циклам, блок фазовой автоподстройки частоты, управляемый распределитель управляющий вход которого одновременно соединен со входом блока фазо вой автоподстройки частоты и выходом декодера фазы, тактирующий вход с выходом блока фазовой автоподстрой ки частоты, а выходы - со входами считывания блока памяти, к входам . записи информации которого подключены информационные выходы коммутатора 1. Однако данное устройство не обеспечивает высокой достоверности передачи при возможном поражении в канале служебной информации. Наиболее близким к предлагаемому является устройство синхронного сопряжения синхронных двоичных сигналов, содержащее на передающей стороне управляемый распределитель, выходы разрядов которого подключены .к первым входам блока памяти, второй вход которого соединен с блоком цикловой синхрбнизации, а также последовательно соединенные блок запуска счетчик, блок сравнения, кодер и Длок прогнозирования, выход которого подключен к другому входу блока i сравнения, а дополнительный вход соединен с выходом блока запуска и входами блока цикловой синхронизации и управляемого распределителя, дополнительный выход которого подключен к другому входу счетчика, а,другой вход управляемого распределителя подключен, к другому выходу бл.рка запуска, а выход кодера ,подключей к другому выходу блока запуска, а выход кодера подключен к третьему входу блока памяти, а на приемной стороне - последовательно соединенные коммутатор, блок цикловой синхронизации, управляемый распределитель и блок памяти, входы разрядов которого соединены с соответствующими выходами коммутатора, а также блок автоподстройки частоты (АПЧ), выход которого подключен к другому входу управляемого распределителя, последовательно соединенные декодер и блок прогнозирования, выход котоl5qro подключен к входу блока АПЧ а другие выходы блока цикловой синхронизации подключены к входам коммутатора и декодера, другой вход которого соединен с дополнительным выходом коммутатора 2. Однако известное устройство не обеспечивает высокой точности сопряжения. Цель изобретения - повышение точности сопряжения. Поставленная цель достигается тем, что в устройстве асинхронного сопряг жения синхронных двоичных сигналов, содержащее на передающей стороне последовательно соединенные, блок запуска и счетчик, блок цикловой -синх- . ронизации, вход которого соединен . с первым выходом блока запуска, управляемый распрямитель, выходы разрядов которого подключены к первым входам блока памяти, второй вход которого соединен с выходом блока цикловой синхронизации, при этом первый вход управляемого распределителя соединен с первым выходом блока запуска, второй выход котороз о соединен со вторым входом управляемого распределителя, а на приемной стороне - последовательно соединенные коммутатор, блок цикловой синхронизации, управляемый распределитель и блок памяти, вторые входы которого соединены с соответствукидими выходами коммутатора, а также блок автоподстройки частоты, выход которого соединен с другим входом управляемого распределителя, на передающей стороне введены три элемента И, первый и второй входы которых соединены соответственно с выходом и вторым входом счетчика, а выходы элементов И соединены соответственно с третьим, четвертым и пятым входами блока памяти, второй выход блока запуска соединен со вторым входом счетчика, а на приемной стороне введены элемент ИЛИ, три элемента И и регистр сдвига, выходы первого, второго и третьего разрядов которого соединены. соответственно с вторыми входами первого и второго элементов И, с первым и вторым входами первого и третьего элементов И и с первыми входами второго и третьего элементов И, при этом первЕЛй;, . второй и третий входы элемента ИЛИ соединены еоответственно с выходами первого, второго и третьего элементов И, выход элемента ИЛИ подклю чен к входу блока АПЧ, третьи входы первого, второго и третьего элементов и соединены с выходом блока цик ловой синхронизации, а дополнительные вход и выход коммутатора соедииены соответственно с дополнительны выходом блока цикловой синхронизгщи и входом регистра- сдвига. На фиг, 1 приведена структурная электрическая схема передающей сто роны предлагаемого устройства; на фиг. 2 - структурная электрическая схема приемной его стороны. Устройство содержит блок 1 запус ка, управляемый распределитель 2, счетчик 3, блок 4 памяти, блок 5 цикловой синхронизации, элементы И б - ,8, на приемной стороне, коммута тор 9, блок 10 цикловой синхронизации, регистр 11 сдвига, элемент ИЛИ 12, блок 13 автоподстройки частоты (АПЧ), управляемый распределитель 14, блок 15 памяти, элементы И 16.- 18. Устройство работает следующим об разом. , Начало работы устройства фиксиру ется на передаче моментом совпадения опорного и тактового импульсов .в блоке 1 запуска, опорные импульсы следуют с частотой ц / N и разделяю несущую последовательность на циклы передачи, в частности это может быть достигнуто с помощью регулируе мой линии задержки сигналов частоты с . Возможна также организация начала работы устройства путем формирования на передакидей стороне и передачи на приемную специальной йодовой комбинации начального рассогласования по фазе опорного и тактового импульсов. Сигнал с.выхода блока 1 запуска разрешает работу управляемого распределителя 2,счетчика 3, блока 5 цикловой синхронизации и элементов И -6 - 8. Управляемый распределитель 2, та тируемый частотой fJ. , представляет собой регистр сдвига с п входами. Запуск его осуществляется опорными импульсами, поступающими с блока 1 запуска. На его выходах тактовые им пуйьсы, .число которых между двумя смежными опорными импульсами подсчи тывается счетчиком 3, служат импуль сами записи синхронного двоичного v сигнала (СДС) в Ьлок 4 памяти. На выходе счетчика 3 формируется сигна .1, если в периоде между двумя смежными опорными импульсами на вход счетчика 3 поступает п тактовых импульсов. Если число тактовых импульсов, поступивших jia вход,.счетчика 3 в периоде междудвумя см ТГыми опорными импульсами, равно п -If то на выходе счетчика 3 формируется сигнал О. С выхода счетчика 3 сигнал Ч или О поступаем; на первые входы элементов И б - 8. На вторые входы элементов И 6 - 8 подаются опорные импульсы частоты IH/N. С выходов элементов И iS - 8 в блок 4 памяти .в параллельном коде записываются комбинации 111, если в цикле-передачи было П единичных информационных интервалов, и 000, если п-1 единичных информационных ин1 ервалов, Блок 5 цикловой синхронизации выдает в блок 4 памяти кодовую комбинацию фазирования: циклов.. Считывание информации и служебных сигналов из блока 4 памяти осуществляется на несущейчастоте f. Организуемый в канале цикл содержит N единичных интервалов, из которых п используемся для информационных посылок, а (N-п)- единичных интервалов для служебных посылок. На приемной стороне устройства (фиг. 2) коммутатор 9 направляет поступившие из каналй сигналы по N соответствующим цепям, из которых Я отведено под информационные импульсы, а ;(М-п)- под служебные. Коммутатор 9 управляется блоком 10 цикловой синхронизации. Служебные сигналы с коммутатора 9 поступают на вход регистра 11 сдвига, выходы разрядов которого попарно соединены с двумя входами элементов И 16 - 18.На третьи входы элементов И 16 - 18 поступают опорные импульсы. Таким образом, любая служебная комбинация с однократной ошибкой, загшсанная в регистре 11 сдвига, декодируется. С выхода одного из элементов И 16 - 18 с приходом опорного импульса снимается сигнал , если служебная комбинация имеет один из видов 111; 011; 101; 110, т.е. если ошибки.нет, если ошибка в первом элементе комбинации; во втором элементе; в третьем элементе. В остальных случаях снимается сигнал О.. Выходы элементов И объединены через элемент ИЛИ 12. Корректировку тактовой час- тоты f (по заданному числу единичных интервалов в цикле на передаче) . осуществляет блок 13 АПЧ. Управляемый распределитель 14 тактируется восстановленной частотой (.., а запускается опорными импульсами из блока 10. Информационные выхода коммутатора 9 соединены с входами блока 15 памяти.

С помощью управляемого распределителя д 4 блок памяти ввдает восста новленйый сяннхронный.двоичный сигнал j

Предлагаемое устройство сопряжения синхронных двоичных сигналов позволяет повысить точность сопряжёния. Кроме того, в случае ксздирования служебной информации с защитой от однократной ошибки т ребуется три единичных интервала (1+2 проверочных) , тогда как в прототипе пять (24-3 проверочных) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1978 |

|

SU786024A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1986 |

|

SU1401629A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ В ПАУЗАХ РЕЧИ | 1991 |

|

RU2015577C1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| СИСТЕМА СИНХРОННОГО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 1995 |

|

RU2096916C1 |

УСТРОЙСТВО АСИНХРОННОГО СОПРЯЖЕНИЯ СИНХРОННЫХ ДВОИЧНЫХ СИГНА ЛОВ, содержгицее на передающей стороне последовательно соединенные блок запуска и счетчик, блок цикловой синхронизации, вход которого соединен с первым выходом блока запуска, управляемый распределитель, выходы разрядов которого подключены к первым входам блока памяти, второй вход которого соединен с выходом блока цикловой синхронизации, при этом первый вход управляемого распределителя соединен с первым выходом блока запуска, второй выход которого соединен со вторым входом управляемого распределителя, а на приемной стороне - последовательно соединенные коммутатор, бло цикловой синхронизации, управляелшй распределитель и блок Пс1мяти, вторые входы которого соединены с соответствукидими выходами коммутатора, а также блок авто подстройки частоты (АПЧ), выхрд которого соединен с другим входом управляемого распределителя, отличающееся тем, что, с целью повышения точности сопряжения, на передающей стороне введены три элемента И, первый и второй входы которых соединены соответственно с выходом и вторым входом счетчика, а выходы элементов И соединены соответственно с третьим, четвертым и пятым входами блока памяти, второй выход блока запуска соединен со вт орым входом счетчика, а на приемной стороне введены элемент ИЛИ, три элемента И и регистр сдвига, выходы первого, второго и третьего разрядов| Ъ которого соединены соответственно ™ь с вторыми входами первого и второго элементов И, с первым и вторым вхои I дами первого и третьего элементов. и с первыми входами второго и третье-g го элементов И, при этом первый, второй и третий входы элемента ИЛИ соединены соответственно с выходами первого,.второго и третьего элементов И, выход элемента ИЛИ подклю-j чен к входу блока АПЧ, третьи вхо ды первого, второго и третьего элементов И соединены с выходом блбкацикловой синхронизации, а ддпблнительные вход и выход коммутатора соединены соответственно с дополнительным выходом блока цикловой синхронизации и входом регистра сдвига.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1974 |

|

SU510792A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР 789024, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-07—Публикация

1982-11-10—Подача