1

Изобретение относится к области связи и может найти применение в аппаратуре передачи данных и электронной коммутации.

Известны коммутаторы, содержащие дешифраторы адреса, регистры информации, триггер тактов, схему НЕ, блоки памяти, схемх распределения приоритетов и адресные шины, причем регистры информации и триггер тактов подключены к соответствующим входам схемы распределения приоритетов, выходы которой соединены с адресными шинами l.

-Недостатком коммутаторов являются узкие функциональные возможности,

Известен также коммутатор, содержащий адресный дешифратор, блоки адресного переключения, блок объединения, при этом первые и вторые входы блоков адресного переключения подключены- к выходам адресного дешифратора и к шине стробирующих импульсов соответственно, а выходы - ко входам блока объединения, выход которого является выходом коммут 5ора 2 .

Недостатком такого коммутатора яв ляется ограниченность функциональных возможностей..

Целью изобретения является расширение функциональных возможностей коммутатора.

Эта цель достигается тем, что в коммутатор, содержащий адресный дешифратор, блоки адресного переключения, блок объединения, при этом первы и вторые входы блоков адресного переключения подключены к выходам адресного дешифратора и к шине стробирующих имцульсов соответственно, а выходы - ко входам блока объединения. выход которого является выходом коммутатора, введены устройства блокировки общего входа, блокировки информационных входов, два элемента Запрет , при этом первые входы устройст блокировки информационных входов соединены с информационными входами коммутатора, вторые - с первым входом управления и входом первого элемента Запрет , а выходы устройств блокировки информационных входов и первого элемента Запрет подключены к третьим входам блоков адресного переключения и второму входу устройства блокировки общего входа соответственно, причем первый вход устройст ва блокировки общего входа соединен с общим входом коммутатора, а выход

устройства блокировки общего входа подключен к четвертым входам блоков адресного переключения, выходы которых соединены с первыми входами устройства блокировки информационных выходов -и соответствующими входами блока объединения, при этом выходы устройств блокировки информационных выходов являются информационными выходами коммутатора, вторые .входы устройств блокировки информационных выходов и вход второго элемента Запрет объединены со вторым входом управления, кроме того, выход второго элемента Запрет соединен с соответствующим входом блока объединения,

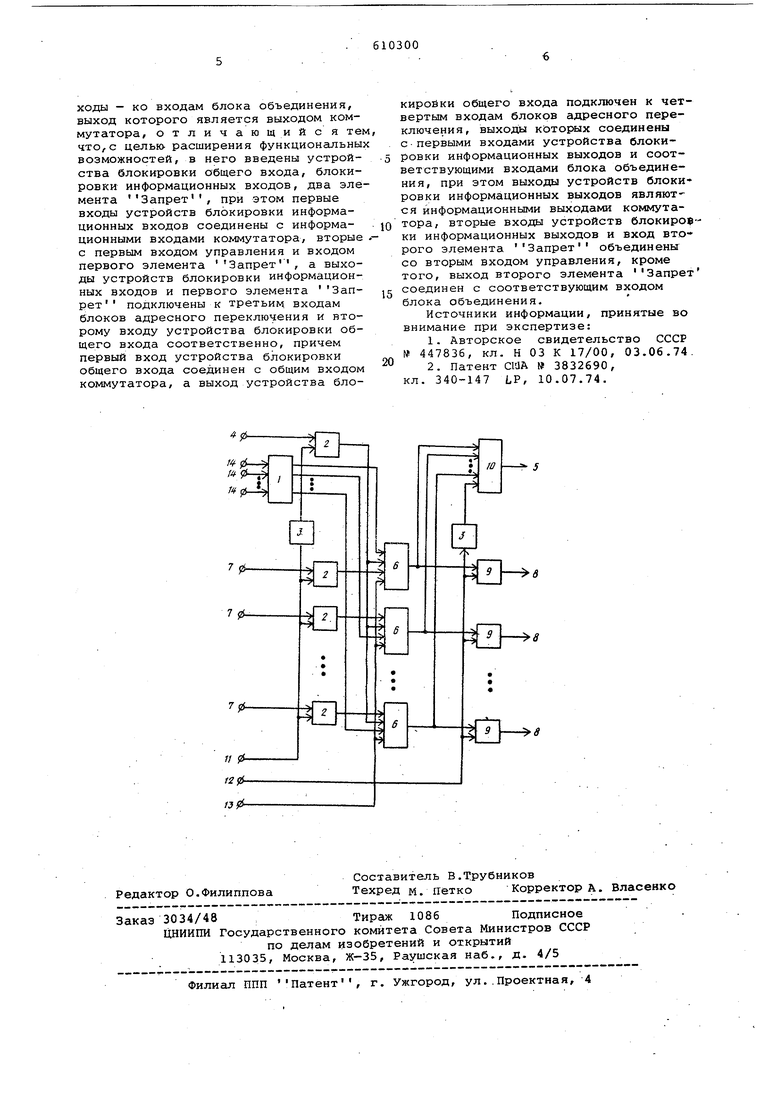

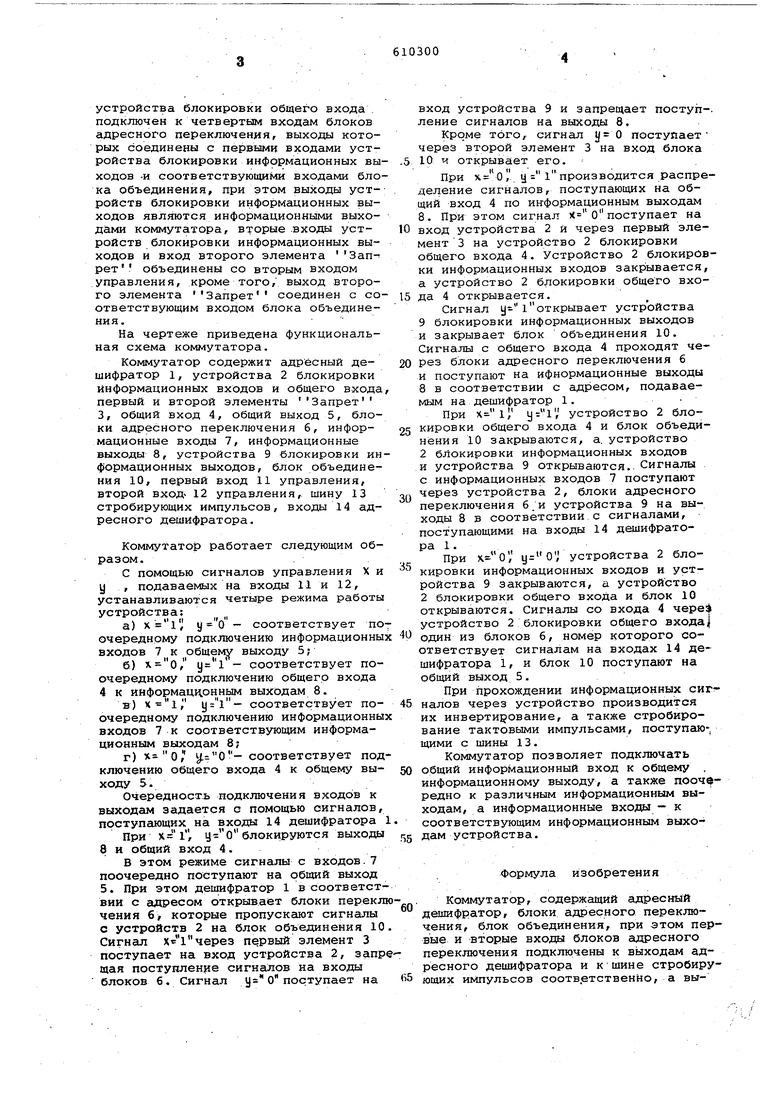

На чертеже приведена функциональная схема коммутатора.

Коммутатор содержит адресный дешифратор 1, устройства 2 блокировки информационных входов и общего входа первый и второй элементы Запрет 3, общий вход 4, общий выход 5, блоки адресного переключения 6, информационные входы 7, информационные выходы 8, устройства 9 блокировки информационных выходов, блок объединения 10, первый вход 11 управления, второй вход- 12 управления, шину 13 стробирующих импульсов, входы 14 адресного дешифратора.

Коммутатор работает следующим образом..

С помощью сигналов управления X и у , подаваемых на входы 11 и 12, устанавливаются четыре режима работы устройства:

а) у о - соответствует поочередному подключению информационны входов 7 к общему выходу 5;

б)х 0, соответствует поочередному подключению общего входа 4 к информацч. выходам 8.

в) соответсТву-ет поочередному подключению информационны входов 7 к соответствующим информационным выходам 8;

г), 1. соответствует подключению общего входа 4 к общему выходу 5.

Очередность подключения входов к выходам задается с помощью сигналов, поступающих на входы 14 дешифратора

При , блокируются выходы 8 и общий вход 4.

В этом режиме сигналы с входов.7 поочередно поступают на общий выход 5. При этом дешифратор 1 в соответствии с адресом открывает блоки переклчения 6, которые пропускают сигналы с устройств 2 на блок объединения 10 Сигнал х через первый элемент 3 поступает на вход устройства 2, запрщая поступление сигналов на входы блоков 6. Сигнал поступает на

вход устройства 9 и запрещает поступление сигналов на выходы 8.

Кроме того, сигнал 1( О поступает через второй элемент 3 на вход блока

.5 10 ч открывает его.

При О, у l производится распреде.ление сигналов, поступающих на общий вход 4 по информационным выходс1М 8. Пр1И этом сигнал )( О поступает на

10 вход устройства 2 и через первый элемент 3 на устройство 2 блокировки общего входа 4. Устройство 2 блокировки информационных входов закрывается, а устройство 2 блокировки общего входа 4 открывается.

Сигнал уь l Открывает устройства 9 блокировки информационных выходов и закрывает блок объединения 10. Сигналы с общего входа 4 проходят через блоки адресного переключения 6 и поступают на ифнормационные выходы 8 в соответствии с адресом, подаваемым на дешифратор 1.

При , устройство 2 бЛО25 кировки общего входа 4 и блок объединения 10 закрываются, а. устройство 2 блокировки информационных входов и устройства 9 открываются.. Сигналы с информационных входов 7 поступают

2Q через устройства 2, блоки адресного переключения б и устройства 9 на выходы 8 в соответствии с сигналами, поступающими на входы 14 дешифратора 1 .

При х.0, у О , устройства 2 бло35кировки информационных входов и устройства 9 закрываются, а устройство 2 блокировки общего входа и блок 10 открываются. Сигналы со входа 4 чере устройство 2 блокировки общего входа

4 один из блоков б, номер которого соответствует сигналам на входах 14 дешифратора 1, и блок 10 поступают на общий выход 5.

При прохождении информационных сиг

45 налов через устройство производится их инвертирование, а также стробирование тактовыми импульсами, поступающими с шины 13.

Коммутатор позволяет подключать

50 общий информационный вход к общему . информационному выходу, а также пооч0редно к различным информационным выходам, а информационные входаг - к соответствующим информационным выходам устройства.

Формула изобретения

Коммутатор, содержащий адресный дешифратор, блоки адресного переключения, блок объединения, при этом первые и вторые входы блоков адресного переключения подключены к выходс1М адресного дешифратора и кшине стробирук)щих импульсов соответственно, а выходы - ко входам блока объединения, выход которого является выходом коммутатора, отличающийся те что,с целью- расширения функциональны возможностей, в него введены устройства блокировки общего входа, блокировки информационных входов, два элемента Запрет, при этом первые входы устройств блокировки информационных Входов соединены с информационными входами коммутатора, вторые с первым входом управления и входом первого элемента Запрет, а выходы устройств блокировки информационных входов и первого элемента Запрет подключены к третьим, входам блоков адресного переключения и второму входу устройства блокировки общего входа соответственно, причем первый вход устройства блокировки общего входа соединен с общим входом коммутатора, а выход устройства блокировки общего входа подключен к четвертым входам блоков адресного переключения, выходы которых соединены с-первыми входами устройства блокировки информационных выходов и соответствующими входами блока объединения, при этом выходы устройств блоки ровки информационных выходов являются информационными выходами коммутатора, вторые входы устройств блокировки информационных выходов и вход второго элемента Запрет объединены со вторым входом управления, кроме того, выход второго элемента Запрет соединен с соответствующим входом блока объединения.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР № 447836, кл. Н 03 К 17/00, 03.06.74

2.Патент ClUA 3832690, кл. 340-147 LP, 10.07.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для обмена информацией между объектом контроля и электронной вычислительной машиной | 1983 |

|

SU1156078A1 |

| Устройство для адресации памяти | 1990 |

|

SU1741142A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1118995A1 |

| Устройство для автоматического контроля многоканального объекта | 1982 |

|

SU1104472A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1550523A1 |

Авторы

Даты

1978-06-05—Публикация

1976-04-08—Подача