Изобретение относится к области автоматикии вычислительной техники и может быть использовано для сопряжения двух электронно-вычислительных машин (ЭВМ) в вычислительных комплексах.

Цель изобретения - повышение скорости обмена информацией между магистралями за счет полного использования времени между обращениями к блоку памяти.

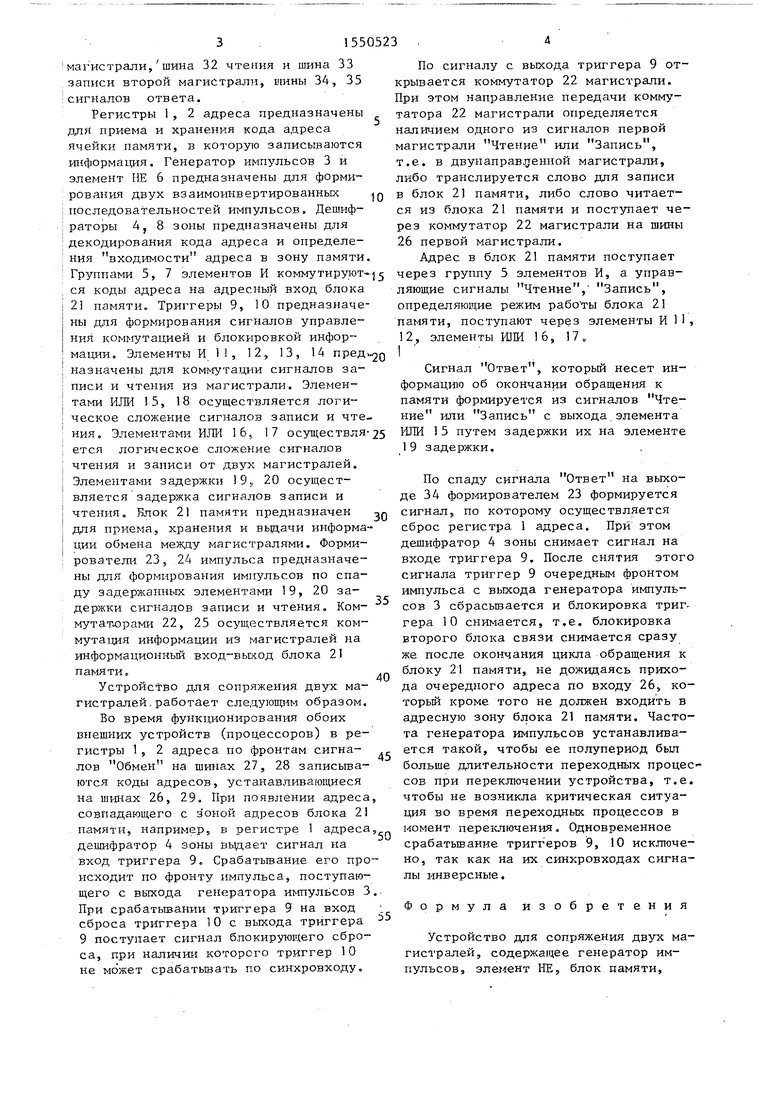

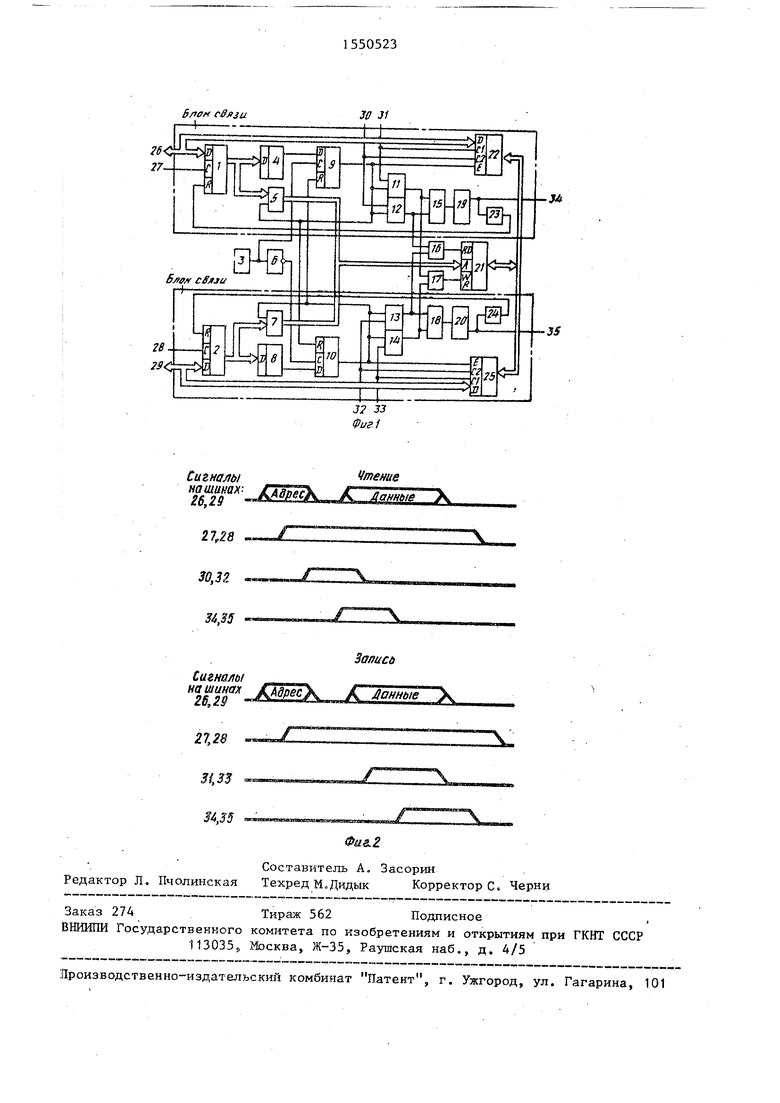

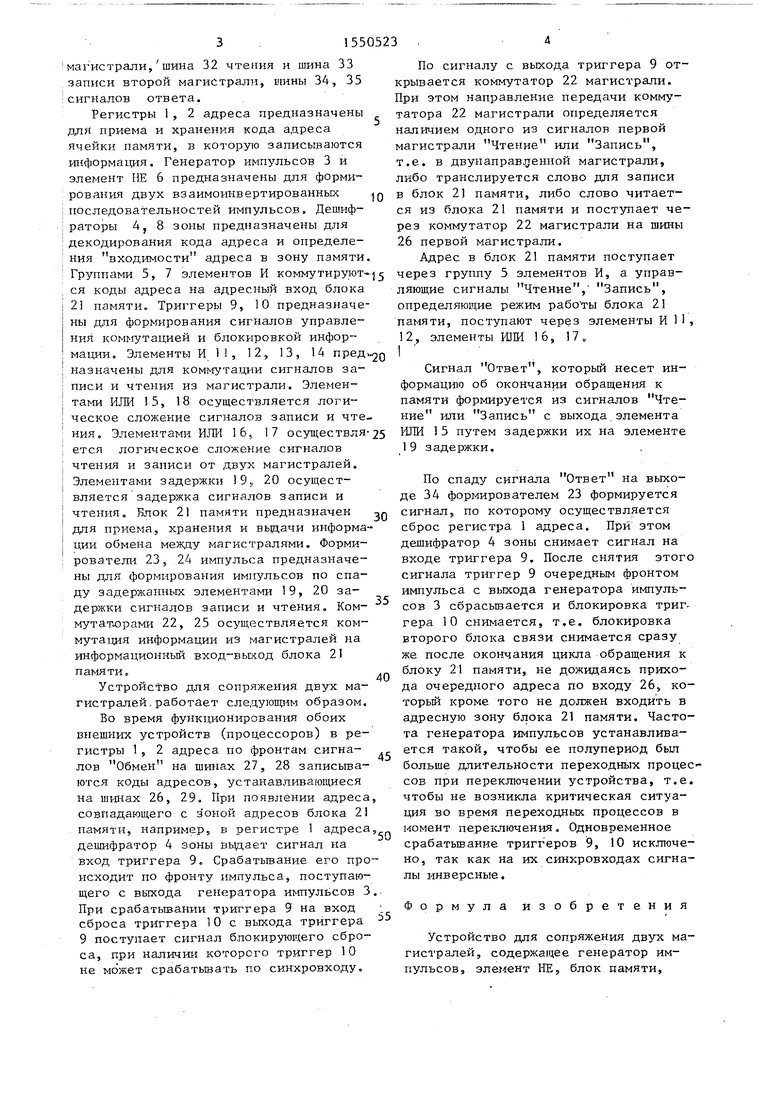

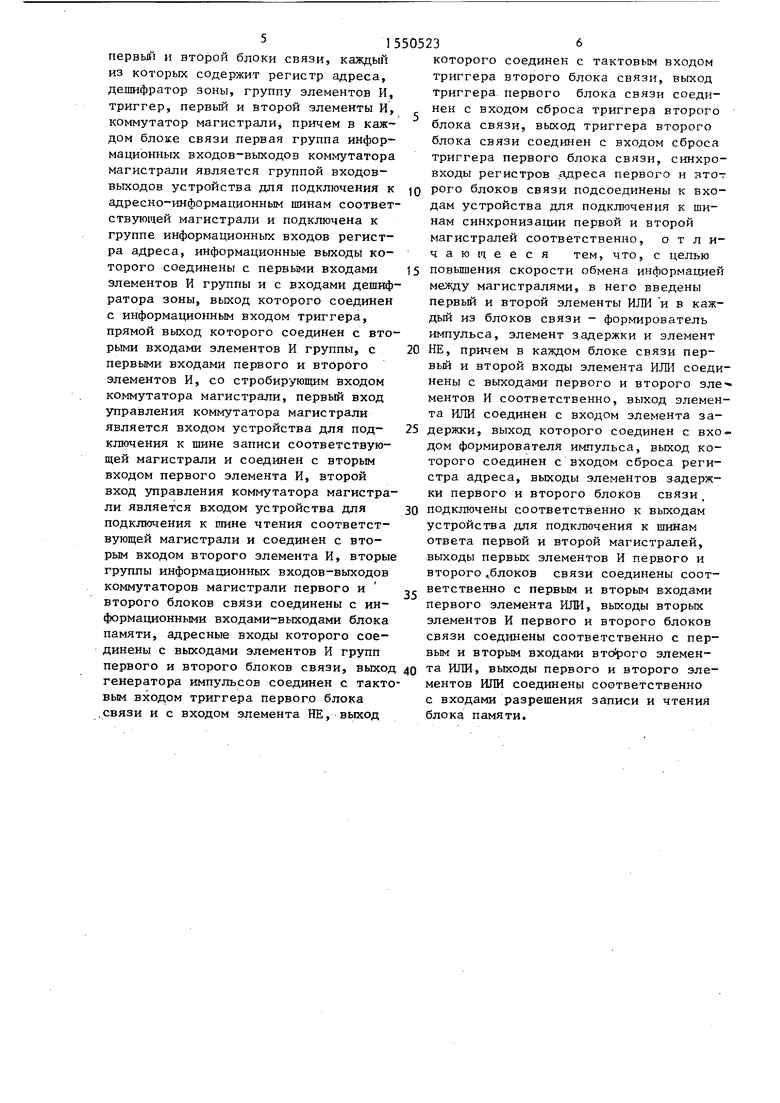

На фиг. 1 представлена схема устройства для сопряжения двух магистралей; на фиг. 2 - временные диаграммы управляющих сигналов для случая организации магистралей согласно ОСТ И 11.305.903-80.

Устройство содержит регистры 1, 2 адреса, генератор импульсов 3, дешифратор 4 зоны, группу 5 элементов И, элемент НЕ 6, группу 7 элементов И, дешифратор 8 зоны, триггеры 9, 10, элементы И 11, 12, 13, 14, элементы ИЛИ 15, 16, 17, 18, элементы 19, 20 задержки, блок 21 памяти, коммутатор 22 магистрали, формирователи 23, 24 импульса, коммутатор 25 магистрали. На фиг. 1 показаны адресно-информационные шины 26 первой магистрали, шина 27 управления обменом первой магистрали, шина 28 управления обменом второй магистрали, адресно-информационные шины 29 второй магистрали, шина 30 чтения и шина 31 записи первой

Сл

СЛ

31550523

магистрали, шина 32 чтения и шина 33

записи второй магистрали, шины 34, 35 сигналов ответа.

Регистры 1, 2 адреса предназначены для приема и хранения кода адреса ячейки памяти, в которую записываются информация. Генератор импульсов 3 и элемент НЕ 6 предназначены для формирования двух взаимоинвертированных последовательностей импульсов. Дешифраторы А, 8 зоны предназначены для декодирования кода адреса и определения входимости адреса в зону памяти.

По сигналу с выхода триггера 9 открывается коммутатор 22 магистрали. При этом направление передачи коммутатора 22 магистрали определяется наличием одного из сигналов первой магистрали Чтение или Запись, т.е. в двунаправленной магистрали, либо транслируется слово для записи в блок 21 памяти, либо слово читается из блока 21 памяти и поступает через коммутатор 22 магистрали на шины 26 первой магистрали.

Адрес в блок 21 памяти поступает

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистралей | 1990 |

|

SU1737460A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1619285A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1619286A1 |

| Устройство для сопряжения двух магистралей | 1990 |

|

SU1778760A1 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1522224A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1575193A2 |

| Устройство для сопряжения двух магистралей | 1985 |

|

SU1283781A1 |

| Специализированный процессор | 1990 |

|

SU1705834A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для сопряжения двух электронно-вычислительных машин в вычислительных комплексах. Целью изобретения является повышение скорости обмена информацией между магистралями за счет полного использования времени между обращениями к блоку памяти. Поставленная цель достигается тем, что в устройство для сопряжения двух магистралей, содержащее генератор импульсов, элемент НЕ, блок памяти и два блока связи, каждый из которых содержит регистр адреса, дешифратор зоны, группу элементов И, триггер, два элемента И, коммутатор магистрали, введены четыре элемента ИЛИ, два элемента задержки и два формирователя импульса по спаду сигнала. Введение новых элементов и связей обеспечивает сброс регистров адреса сразу после окончание обращения к блоку памяти, чем достигается полное использование времени между обращениями к блоку памяти, уменьшается время блокировки одного блока сопряжения другим и повышается быстродействия устройства. 2 ил.

Группами 5, 7 элементов И коммутируют- через группу 5 элементов И, а управ30

35

ся коды адреса на адресный вход блока 2i памяти. Триггеры 9, 10 предназначены для формирования сигналов управления коммутацией и блокировкой информации. Элементы И II, 12, 13, 14 назначены для коммутации сигналов записи и чтения из магистрали. Элементами ИЛИ 15, 18 осуществляется логическое сложение сигналов записи и чтения. Элементами ИЛИ 16, 17 осуществля-25 ется логическое сложение сигналов чтения и записи от двух магистралей. Элементами задержки 19., 20 осуществляется задержка сигналов записи и чтения. Блок 21 памяти предназначен для приема, хранения и выдачи информации обмена между магистралями. Формирователи 23, 24 импульса предназначены для формирования импульсов по спаду задержанных элементами 19, 20 задержки сигналов записи и чтения. Коммутаторами 22, 25 осуществляется коммутация информации из магистралей на информационный вход-выход блока 21 памяти.

Устройство для сопряжения двух магистралей работает следующим образом.

Во время функционирования обоих внешних устройств (процессоров) в регистры 1, 2 адреса по фронтам сигналов Обмен на шинах 27, 28 записываются коды адресов, устанавливающиеся на шинах 26, 29. При появлении адреса, совпадающего с з оной адресов блока 21 памяти, например, в регистре 1 адреса дешифратор 4 зоны выдает сигнал на вход триггера 9. Срабатывание его происходит по фронту импульса, поступающего с выхода генератора импульсов 3. При срабатывании триггера 9 на вход сброса триггера 10 с выхода триггера 9 поступает сигнал блокирующего сброса, при наличии которого триггер 10 не может срабатывать по синхровходу.

40

45

50

55

ляющие сигналы Чтение, Запись, определяющие режим работы блока 21 памяти, поступают через элементы И 11 12, элементы ИЛИ 16, 17.

Сигнал Ответ, который несет информацию об окончании обращения к памяти формируется из сигналов Чтение или Запись с выхода элемента ИЛИ 15 путем задержки их на элементе 19 задержки.

По спаду сигнала Ответ на выходе 34 формирователем 23 формируется сигнал, по которому осуществляется сброс регистра 1 адреса. При этом дешифратор 4 зоны снимает сигнал на входе триггера 9. После снятия этого сигнала триггер 9 очередным фронтом импульса с выхода генератора импульсов 3 сбрасывается и блокировка триггера 10 снимается, т.е. блокировка второго блока связи снимается сразу же после окончания цикла обращения к блоку 21 памяти, не дожидаясь прихода очередного адреса по входу 26, который кроме того не должен входить в адресную зону блока 21 памяти. Частота генератора импульсов устанавливается такой, чтобы ее полупериод был больше длительности переходных процес сов при переключении устройства, т.е. чтобы не возникла критическая ситуация во время переходных процессов в момент переключения. Одновременное срабатывание триггеров 9, 10 исключено, так как на их синхровходах сигналы инверсные.

Формула изобретения

Устройство для сопряжения двух магистралей, содержащее генератор импульсов, элемент НЕ, блок памяти,

0

5

о 5

0

5

0

5

ляющие сигналы Чтение, Запись, определяющие режим работы блока 21 памяти, поступают через элементы И 11 , 12, элементы ИЛИ 16, 17.

Сигнал Ответ, который несет информацию об окончании обращения к памяти формируется из сигналов Чтение или Запись с выхода элемента ИЛИ 15 путем задержки их на элементе 19 задержки.

По спаду сигнала Ответ на выходе 34 формирователем 23 формируется сигнал, по которому осуществляется сброс регистра 1 адреса. При этом дешифратор 4 зоны снимает сигнал на входе триггера 9. После снятия этого сигнала триггер 9 очередным фронтом импульса с выхода генератора импульсов 3 сбрасывается и блокировка триггера 10 снимается, т.е. блокировка второго блока связи снимается сразу же после окончания цикла обращения к блоку 21 памяти, не дожидаясь прихода очередного адреса по входу 26, который кроме того не должен входить в адресную зону блока 21 памяти. Частота генератора импульсов устанавливается такой, чтобы ее полупериод был больше длительности переходных процессов при переключении устройства, т.е. чтобы не возникла критическая ситуация во время переходных процессов в момент переключения. Одновременное срабатывание триггеров 9, 10 исключено, так как на их синхровходах сигналы инверсные.

Формула изобретения

Устройство для сопряжения двух магистралей, содержащее генератор импульсов, элемент НЕ, блок памяти,

первый и второй блоки связи, каждый из которых содержит регистр адреса, дешифратор зоны, группу элементов И, триггер, первый и второй элементы И, коммутатор магистрали, причем в каждом блоке связи первая группа информационных входов-выходов коммутатора магистрали является группой входов- выходов устройства для подключения к адресно-информационным шинам соответствующей магистрали и подключена к группе информационных входов регистра адреса, информационные выходы которого соединены с первыми входами элементов И группы и с входами дешифратора зоны, выход которого соединен с информационным входом триггера, прямой выход которого соединен с вторыми входами элементов И группы, с первыми входами первого и второго элементов И, со стробирующим входом коммутатора магистрали, первый вход управления коммутатора магистрали является входом устройства для подключения к шине записи соответствующей магистрали и соединен с вторым входом первого элемента И, второй вход управления коммутатора магистрали является входом устройства для подключения к шине чтения соответствующей магистрали и соединен с вторым входом второго элемента И, вторые группы информационных входов-выходов коммутаторов магистрали первого и второго блоков связи соединены с информационными входами-выходами блока памяти, адресные входы которого соединены с выходами элементов И групп

первого и второго блоков связи, выход 40 та ИЛИ, выходы первого и второго эле- генератора импульсов соединен с такто- ментов ИЛИ соединены соответственно вым входом триггера первого блока с входами разрешения записи и чтения .связи и с входом элемента НЕ, выход блока памяти.

0

которого соединен с тактовым входом триггера второго блока связи, выход триггера первого блока связи соединен с входом сброса триггера второго блока связи, выход триггера второго блока связи соединен с входом сброса триггера первого блока связи, синхро- входы регистров адреса первого и зто-т рого блоков связи подсоединены к входам устройства для подключения к шинам синхронизации первой и второй магистралей соответственно, о т л и- чающееся тем, что, с целью

5 повышения скорости обмена информацией между магистралями, в него введены первьй и второй элементы ИЛИ и в каждый из блоков связи - формирователь импульса, элемент задержки и элемент

0 НЕ, причем в каждом блоке связи первый и второй входы элемента ИЛИ соединены с выходами первого и второго элементов И соответственно, выход элемента ИЛИ соединен с входом элемента задержки, выход которого соединен с входом формирователя импульса, выход которого соединен с входом сброса регистра адреса, выходы элементов задержки первого и второго блоков связи подключены соответственно к выходам устройства для подключения к шинам ответа первой и второй магистралей, выходы первых элементов И первого и второго ,блоков связи соединены соответственно с первым и вторым входами первого элемента ИЛИ, выходы вторых элементов И первого и второго блоков связи соединены соответственно с первым и вторым входами второго элемен5

0

5

В лек связи

Чтение

jK uaHHbie A.

27,28 -.

30 31

ЗА

Чтение

Записи

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух магистралей | 1985 |

|

SU1283781A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-15—Публикация

1988-06-08—Подача