Изобретение относится к вычислительной технике, в частности, к оперативным запоминающим устройствам, и может быть использовано для оперативной пересылки информационных элементов при разбивке информационных массивов на последовательные группы.

Известна структура организации доступа к блокам памяти от центрального процессора. Она содержит двунаправленную шину данных (ШД), соединяющую информационный вход-выход процессора с оперативной памятью, адресную шину (ША), соединяющую адресные входы памяти и выходы процессора, и шину управления (ШУ). Дешифраторы адреса, подключаемые, как правило, к линиям старших разрядов ША, позволяют образовать сигналы выборки как

конкретных блоков памяти, так и устройств ввода-вывода.

Недостатком устройства является невозможность оперативного обмена абонента с системной памятью процессора при передаче значительных объемов информации. Передача последовательных элементов массива вызывает необходимость программного перебора ячеек хранения элементов в памяти и проверки наличия конца массива, чем значительно снижается быстродействие обмена.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее контроллер прямого доступа к памяти (КПДП), ШД, ША, ШУ, дешифратор и регистр адреса. КПДП захватывает шины и ведет информационный обмен

XI

J ГО

с абонентом. Предварительно КПДП инициируется на передачу массива последовательно расположенных данных между системной памятью процессора и устройством ввода-вывода, а его внутренние информационные и функциональные регистры имеют доступ к ШД и адресуются процессором как устройства ввода-вывода. КПДП устанавливается в режим передачи. В него заносятся адрес первого элемента, расположенного в системной памяти и длина передаваемого массива. Затем по выявлении устройством ввода-вывода запроса на передачу (ЗПД) КПДП выставляет процессору запрос на захват шин (ЗХ) и получает от него сигналы подтверждения (ПЗХ), захватывает системные шины и ведет передачу байтов массива, выставляя на ША инкрементируе- мый адрес, блокируя при этом сигналом запрета (ЗПТ) неиспользуемые внешние устройства, подтверждая передачу каждого байта по ШД сигналом РПДО.

Аппаратное использование обмена значительно повышает его скорость. Однако в задачах сортировки упорядоченных данных пересылка какого-либо признака в записях, составляющих массив, приводит к необходимости передачи всего массива с последующей его сортировкой, что значительно снижает эффективность передачи.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для адресации памяти, содержащее КПДП, дешифратор, ШУ, ШД, и ША, и вход запрета на передачу данных, выходы разрешения передачи данных и блокировки КПДП - соответствующие вход и выходы устройства, входы-выходы управления режимов работы КПДП, информационный вход-выход, адресный вход и вход выборки КПДП подключены соответственно к информационному входу-выходу устройства, входу младших разрядов адреса устройства и первому выходу дешифратора, информационный вход которого подключен к входу старших разрядов адреса устройства, введены 2 триггера, три элемента И, второй дешифратор, два элемента ИЛИ, два блока накапливающих сумматоров, вход сброса первого триггера соединен с выходом ЗХ КПДП, вход установки - со стробирующим выходом КПДП и первым входом первого элемента И, а выход - с вторым входом первого элемента И, выход которого подключен к первым входам элементов ИЛИ, вторые входы которых подключены соответственно к выходам второго и третьего элементов И, а выходы соответственно - к первым синхровходам блоков сумматоров,

информационные выходы которых подключены к адресным входам устройства: первого - к входам старших, второго - младших разрядов устройства, вход переноса перво5 го блока соединен с нулевой шиной, выход переноса - с входом переноса второго блока, информационные входы блоков подключены к информационному входу устройства, управляющие входы соединены с выходом

0 ЗПТ КПДП и первым стробирующим входом второго дешифратора, а вторые синхровхо- ды подключены соответственно к второму и третьему выходам первого дешифратора, второй стробирующий вход которого соеди5 нен с входом-выходом записи КПДП, а первый выход - с стробирующим входом второго дешифратора, информационный вход которого подключен к входам младших разрядов устройства, а выход - к первым

0 входам второго и третьего элементов И и к счетному входу второго триггера, вход сброса которого соединен с входом системного сброса КПДП, а инверсный выход и прямой выходы подключены соответственно к вто5 рым входам второго и третьего элементов И. Блок накапливающего сумматора содержит коммутатор, два регистра, сумматор и шинный формирователь, выход которого - информационный выход блока, вход разре0 шения подключен к управляющему входу коммутатора и является управляющим входом блока, а информационный вход соединен с первым информационным входом коммутатора и информационным выходом

5 сумматора, выход и вход которого - соответствующие выход и вход блока, первый и второй информационные входы подключены соответственно к выходам регистров, синхровходы которых-соответственно пер0 вый и второй синхровходы блока, а информационный выход первого регистра соединен с выходом коммутатора, второй информационный вход которого подключен к информационному входу второго регистра

5 и,является информационным входом блока. Новая совокупность известных элементов позволяет производить аппаратно организованную передачу каждого К-го элемента информационного массива, за

0 счет чего быстродействие обмена повышается, как минимум, вдвое.

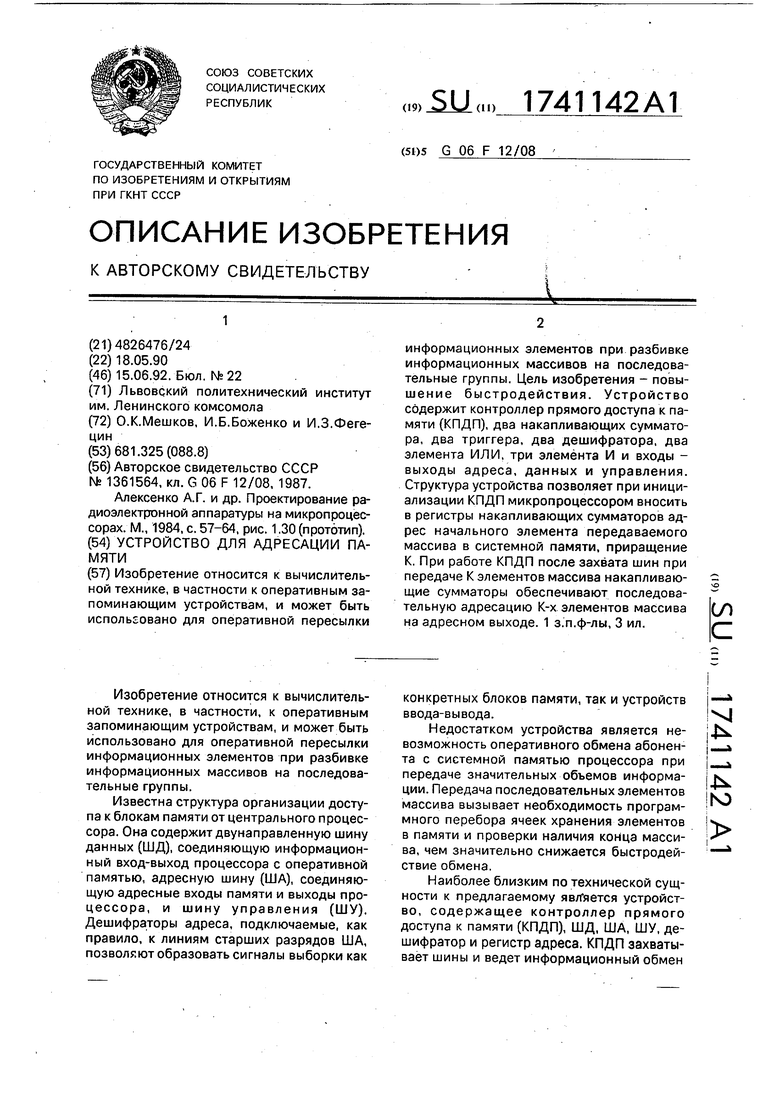

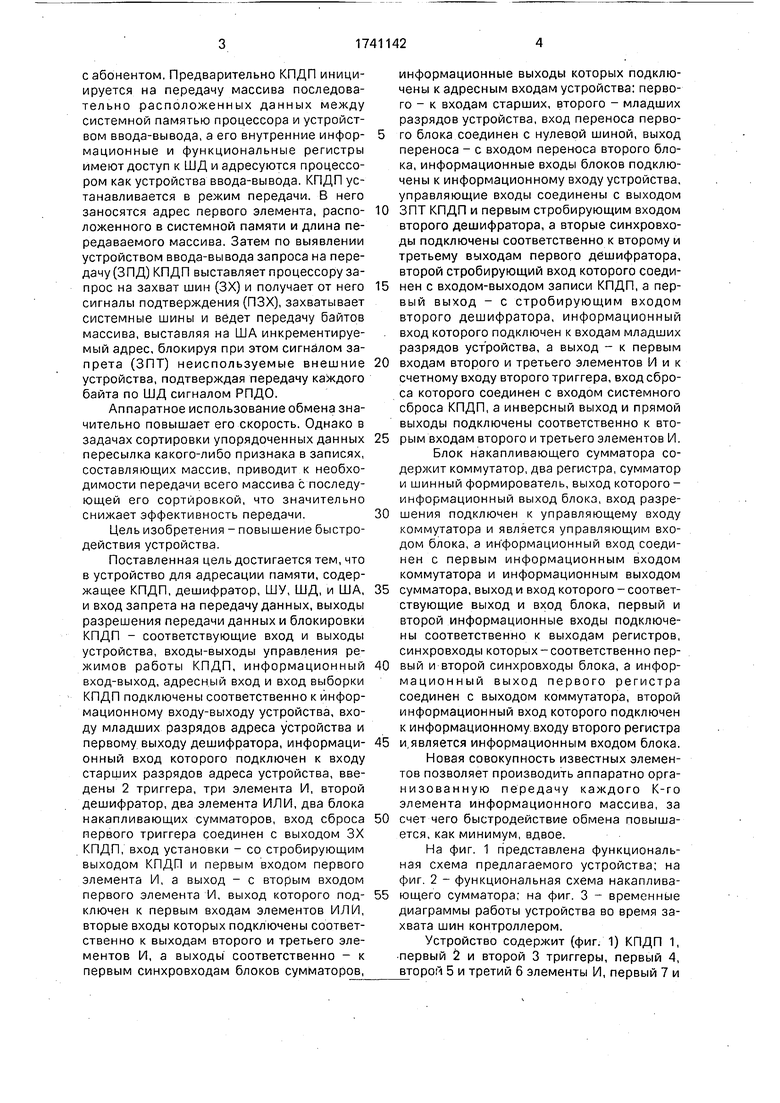

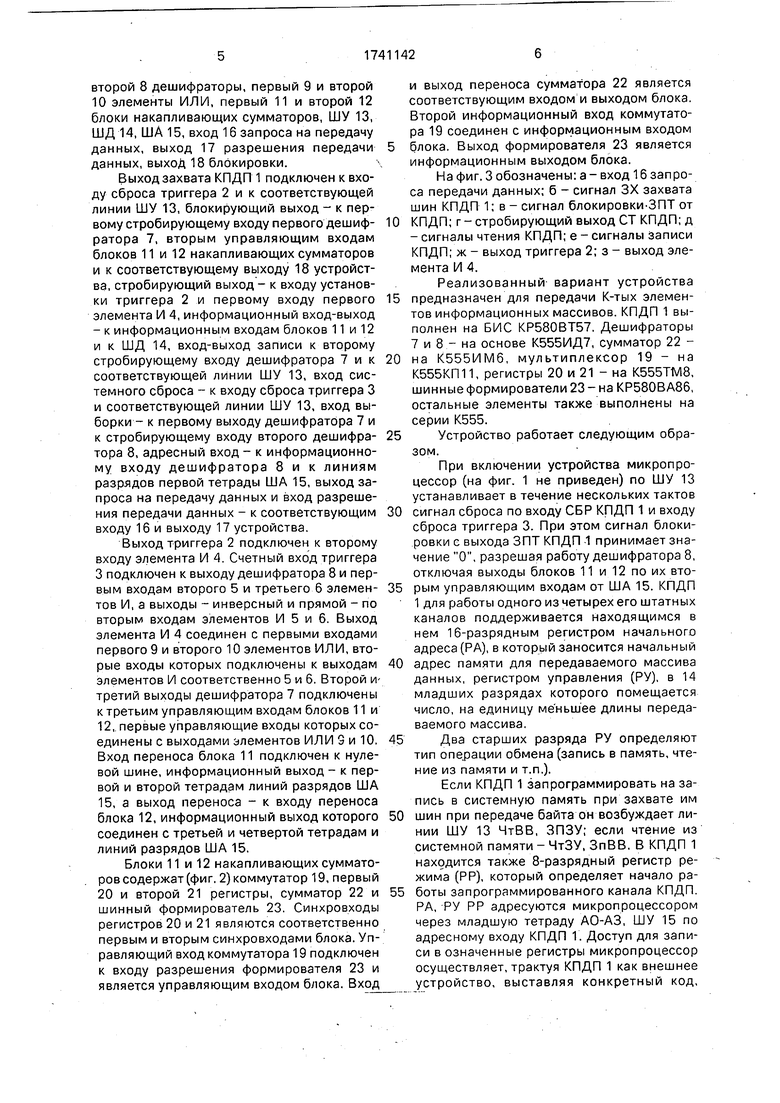

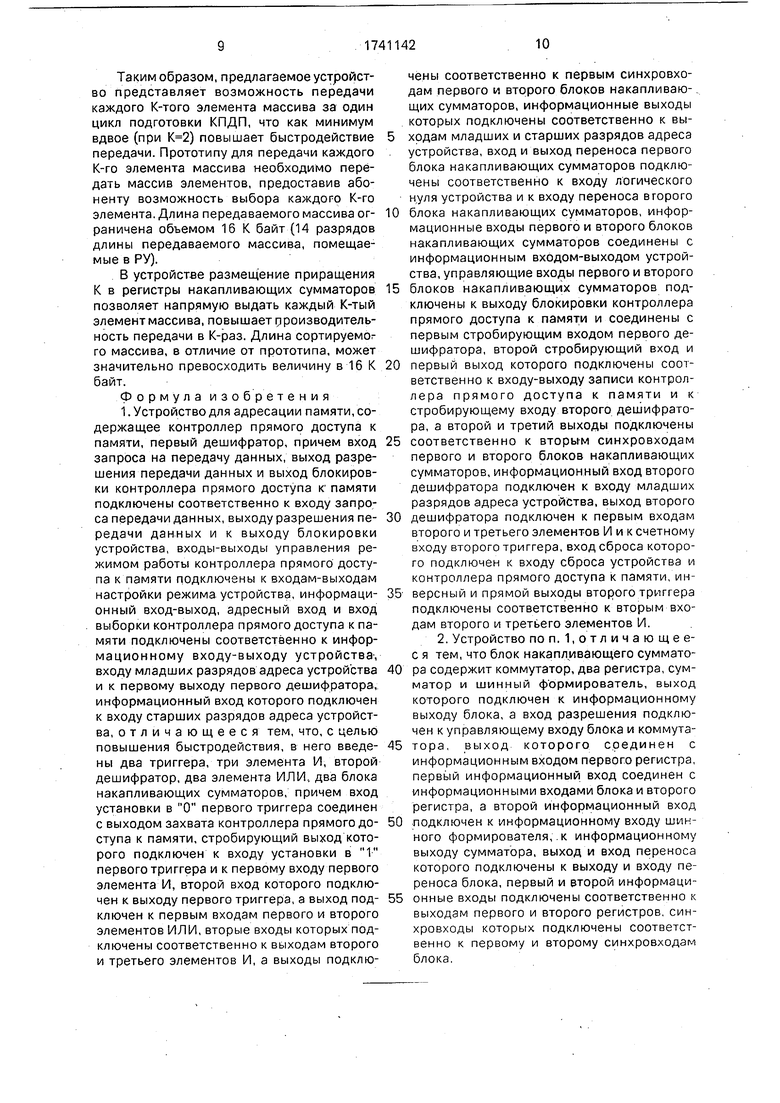

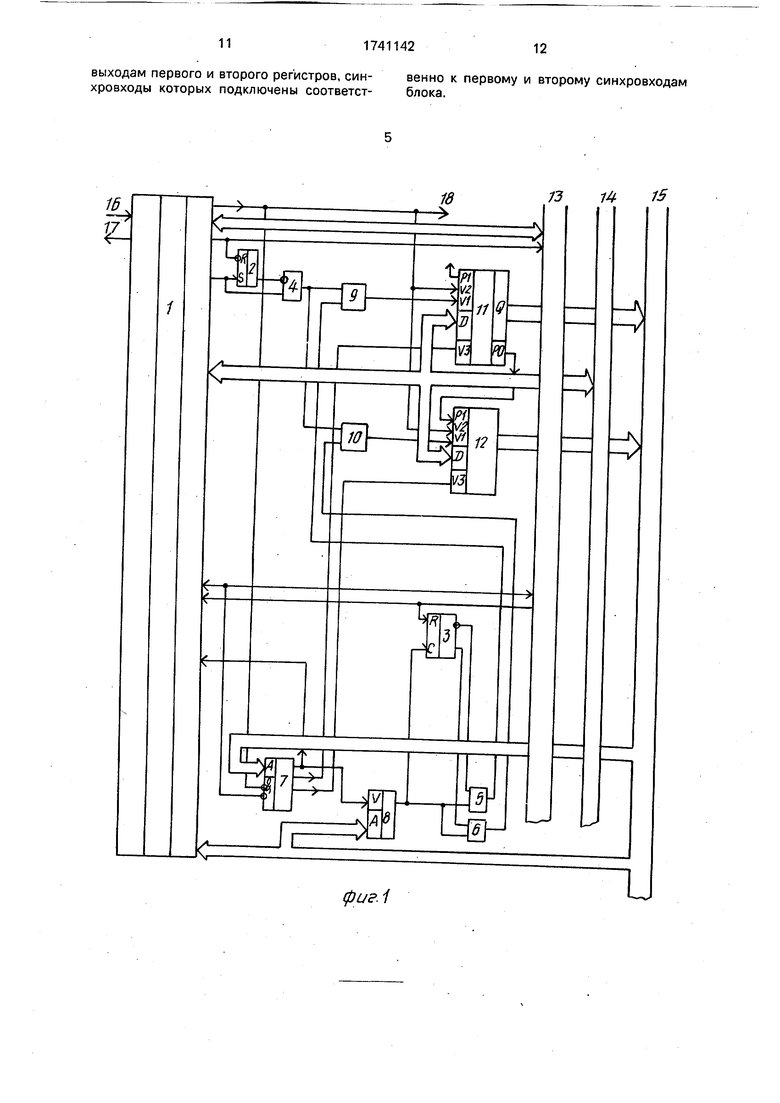

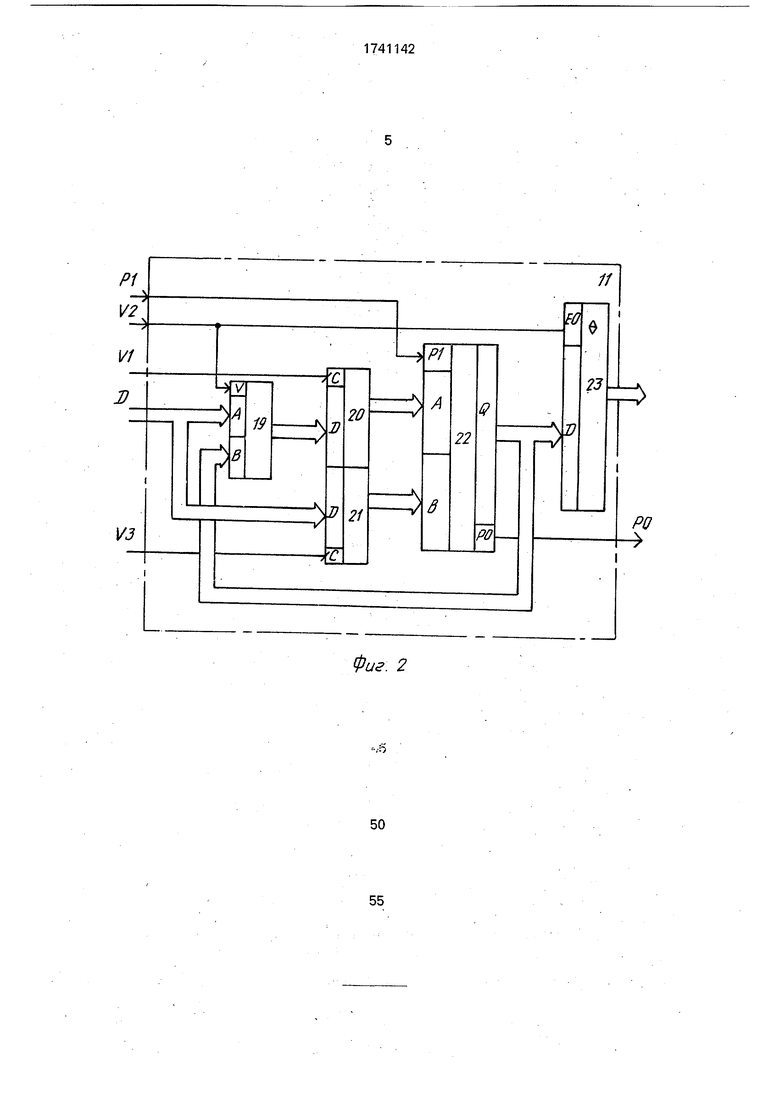

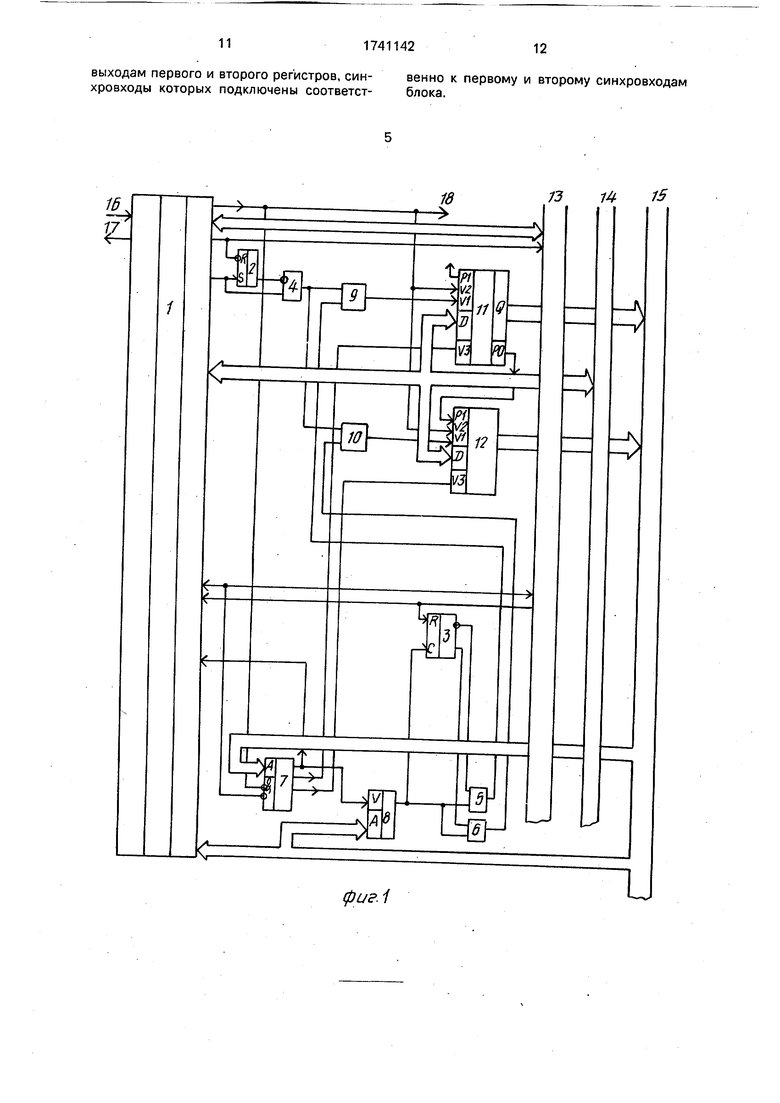

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема накаплива5 ющего сумматора; на фиг. 3 - временные диаграммы работы устройства во время захвата шин контроллером.

Устройство содержит (фиг. 1) КПДП 1, первый 2 и второй 3 триггеры, первый 4,

второй 5 и третий 6 элементы И, первый 7 и

второй 8 дешифраторы, первый 9 и второй 10 элементы ИЛИ, первый 11 и второй 12 блоки накапливающих сумматоров, ШУ 13, ШД 14, ША 15, вход 16 запроса на передачу данных, выход 17 разрешения передачи данных, выхоД 18 блокировки.

Выход захвата КПДП 1 подключен к входу сброса триггера 2 и к соответствующей линии ШУ 13, блокирующий выход - к первому стробирующему входу первого дешифратора 7, вторым управляющим входам блоков 11 и 12 накапливающих сумматоров и к соответствующему выходу 18 устройства, стробирующий выход - к входу установки триггера 2 и первому входу первого элемента И 4, информационный вход-выход - к информационным входам блоков 11 и 12 и к ШД 14, вход-выход записи к второму стробирующему входу дешифратора 7 и к соответствующей линии ШУ 13, вход системного сброса - к входу сброса триггера 3 и соответствующей линии ШУ 13, вход выборки - к первому выходу дешифратора 7 и к стробирующему входу второго дешифратора 8, адресный вход - к информационному входу дешифратора 8 и к линиям разрядов первой тетрады ША 15, выход запроса на передачу данных и вход разрешения передачи данных - к соответствующим входу 16 и выходу 17 устройства.

Выход триггера 2 подключен к второму входу элемента И 4. Счетный вход триггера 3 подключен к выходу дешифратора 8 и первым входам второго 5 и третьего 6 элементов И, а выходы - инверсный и прямой - по вторым входам элементов И 5 и 6. Выход элемента И 4 соединен с первыми входами первого 9 и второго 10 элементов ИЛИ, вторые входы которых подключены к выходам элементов И соответственно 5 и 6. Второй и- третий выходы дешифратора 7 подключены к третьим управляющим входам блоков 11 и 12, первые управляющие входы которых соединены с выходами элементов ИЛИ S и 10. Вход переноса блока 11 подключен к нулевой шине, информационный выход - к первой и второй тетрадам линий разрядов ША 15, а выход переноса - к входу переноса блока 12, информационный выход которого соединен с третьей и четвертой тетрадам и линий разрядов ША 15,

Блоки 11 и 12 накапливающих сумматоров содержат (фиг. 2) коммутатор 19, первый 20 и второй 21 регистры, сумматор 22 и шинный формирователь 23. Синхровходы регистров 20 и 21 являются соответственно первым и вторым синхровходами блока. Управляющий вход коммутатора 19 подключен к входу разрешения формирователя 23 и является управляющим входом блока. Вход

и выход переноса сумматора 22 является соответствующим входом и выходом блока. Второй информационный вход коммутатора 19 соединен с информационным входом

блока. Выход формирователя 23 является информационным выходом блока.

На фиг. 3 обозначены: а - вход 16 запроса передачи данных; б - сигнал ЗХ захвата шин КПДП 1; в - сигнал блокировки-ЗПТ от

0 КПДП; г-стробирующий выход СТ КПДП; д - сигналы чтения КПДП; е - сигналы записи КПДП; ж - выход триггера 2; з - выход элемента И 4.

Реализованный вариант устройства

5 предназначен для передачи К-тых элементов информационных массивов. КПДП 1 выполнен на БИС КР580ВТ57. Дешифраторы 7 и 8 - на основе К555ИД7, сумматор 22 0 на К555ИМ6, мультиплексор 19 - на К555КП11, регистры 20 и 21 - на К555ТМ8, шинные формирователи 23 - на КР580ВА86, остальные элементы также выполнены на серии К555.

5 Устройство работает следующим образом.

При включении устройства микропроцессор (на фиг. 1 не приведен) по ШУ 13 устанавливает в течение нескольких тактов

0 сигнал сброса по входу СВР КПДП 1 и входу сброса триггера 3. При этом сигнал блокировки с выхода ЗПТ КПДП 1 принимает значение О, разрешая работу дешифратора 8, отключая выходы блоков 11 и 12 по их вто5 рым управляющим входам от ША 15. КПДП 1 для работы одного из четырех его штатных каналов поддерживается находящимся в нем 16-разрядным регистром начального адреса (РА), в который заносится начальный

0 адрес памяти для передаваемого массива данных, регистром управления (РУ), в 14 младших разрядах которого помещается число, на единицу меньшее длины передаваемого массива.

5Два старших разряда РУ определяют

тип операции обмена (запись в память, чтение из памяти и т.п.).

Если КПДП 1 запрограммировать на запись в системную память при захвате им

0 шин при передаче байта он возбуждает линии ШУ 13 ЧтВВ, ЗПЗУ; если чтение из системной памяти - ЧтЗУ, ЗпВВ. В КПДП 1 находится также 8-разрядный регистр режима (РР), который определяет начало ра5 боты запрограммированного канала КПДП РА, РУ РР адресуются микропроцессором через младшую тетраду АО-АЗ, ШУ 15 по адресному входу КПДП 1. Доступ для записи в означенные регистры микропроцессор осуществляет, трактуя КПДП 1 как внешнее устройство, выставляя конкретный код,

присваемый КПД 1, на второй тетраде ША 15, подтверждая его сигналом записи ЗПВВ. Последний сигнал по первому стро- бирующему входу при активном нулевом входе подтверждает код КПДП на дешифра- торе 7, первый выход которого, являющийся входом выборки КПДП, принимает активное значение. Тем самым командой OUT ША (7-5)код КПДП 1, ША{3-0) или РР микропроцессор осуществляет запись в требу- емый источник.

Запись в 16-разрядный источник осуществляется следующим образом.

По указанному адресу последовательно записываются два байта, составляющие 16- разрядное слова, сначала младший байт, за- тем старший. Запись в РА КПДП 1 аппаратно дублируется записью в регистры 20 блоков 11 и 12, которые обслуживают соответственно младший и старший байты 16-разрядного числа (чему соответствует подключение к нулевой шине входа переноса блока 11 и выхода переноса блока 11 к входу переноса блока 12). Код тетрады РА, вставленный на ША 15, обозначается де- шифратором 8, который при записи микропроцессора в один из байтов РА КПДП 1 стробируется по входу выборки с первого выхода дешифратора 7. В итоге на выходе дешифратора 8 появляется сигнал, дублиру- ющий сигнал записи в РА младшего или старшего байта 16-разрядного адреса расположения первого элемента массива в системной памяти.

Выбор нужного байта, осуществляет коммутатор, выполненный на элементах 5, 6, 9, 10 и триггере 3. При начальной установке триггер 3 сброшен. При записи младшего байта в РА триггер 3 значением 1 своего инверсного выхода разрешает элементу И 5 квитировать дублирование сигнала записи. С выхода элемента И 5 этот сигнал через элемент ИЛИ 9 проходит на первый управляющий вход блока 11, записывая в его ре- гистр 20 младший байт адреса первого элемента массива, который будучи выставленным на ШД 14, через первый вход коммутатора 19 подается на информационный вход регистра 20. Запись информации в ре- гистр 20 происходит по срезу сигнала на его синхровходе. По срезу сигнала записи триг- гер 3 также изменяет свое состояние, подготавливая значением 1 на своем прямом выходе тракт прохождения для следующего сигнала записи: элемент И 6 - элемент ИЛИ 10 - первый синхровход блока 12.

Последующая запись микропроцессором старшего байта в РА КПДП 1 приводит также и к записи;его в регистр 20 блока 12.

По окончании записи триггер 3 принимает значение О и готов к следующему циклу записи в РА.

Значение приращения к текущему адресу хранится в регистрах 21 блоков 11 и 12 - соответственно младший и старший байты приращения. Занесение в них требуемых значений осуществляется микропроцессором выборки команды OUT по адресу во второй тетраде ША 15, отведенному регистром 21 и дешифрируемому дешифратором 7, соответственно вторым и третьим выходами, Тем самым инициализация микропроцессором устройства заключается в следующем.

Запись в РА КПДП 1 адреса в системной памяти первого элемента массива (при этом указанный адрес параллельно записывается в регистры 20 блоков 11 и 12). Запись в РУ КПДП 1 типа операции обмена и длины списка передаваемых элементов. Запись приращения (расстояния доследующего выбираемого элемента) в регистры 21 блоков 11 и 12. Запись в РР КПДП 1 режима работы, что означает разрешение работы КПДП 1.

При поступлении от внешнего устройства, служащего абонентом для передачи байтов, запроса на передачу ЗПД (фиг. 3 а), КПДП 1 выдает сигнал захвата шин ЗХ (фиг. 3 б) и, получив подтверждение от микропроцессора, захватывает их, При этом, выставляя сигнал блокировки ЗПТ на выход 18 для внешних устройств (фиг. 3 в) и подключая шинные формирователи 23 блоков 11 и 12 к ША 15, а также вторые информационные входы коммутаторов 19 к информационным входам регистров 20, начинают организацию обмена, подтверждая каждый передаваемый элемент в случае записи в системную память сигналами в ШУ 13 ЧтВВ, ЗпВВ, ЗпЗУ; чтения из системной памяти ЧтЗУ, ЗпВВ (фиг. Зд, е).

Передачу очередного элемента КПДП 1 предваряют стробирующим сигналом СТ, который используется для модификации содержимого регистров 20 блоков 11 и 12 на величину шага, хранимого в регистрах 21 после передачи очередного элемента массива, Для этого взводится триггер 2 (фиг, 3 ж), запрещающий по второму входу элемента И 4 прохождение через первые входы элементов ИЛИ 9 и 10 на синхровходы регистров 20 первого импульса СТ (фиг. 3 з). По окончании передачи всех элементов, записанных в РУ КПДП 1, последний снимает сигналы блокировки и захвата шин, (фиг. 3 в, б). Последний сигнал сбрасывает триггер 2, подготавливая его к следующему циклу передачи.

Таким образом, предлагаемое устройство представляет возможность передачи каждого К-того элемента массива за один цикл подготовки КПДП, что как минимум вдвое (при ) повышает быстродействие передачи. Прототипу для передачи каждого К-го элемента массива необходимо передать массив элементов, предоставив абоненту возможность выбора каждого К-го элемента. Длина передаваемого массива ограничена объемом 16 К байт (14 разрядов длины передаваемого массива, помещаемые в РУ).

В устройстве размещение приращения К в регистры накапливающих сумматоров позволяет напрямую выдать каждый К-тый элемент массива, повышает рроизводитель- ность передачи в К-раз. Длина сортируемог го массива, в отличие от прототипа, может значительно превосходить величину в 16 К байт.

Формула изобретения

1. Устройство для адресации памяти, содержащее контроллер прямого доступа к памяти, первый дешифратор, причем вход запроса на передачу данных, выход разрешения передачи данных и выход блокировки контроллера прямого доступа к памяти подключены соответственно к входу запроса передачи данных, выходу разрешения передачи данных и к выходу блокировки устройства, входы-выходы управления режимом работы контроллера прямого доступа к памяти подключены к входам-выходам настройки режима устройства, информационный вход-выход, адресный вход и вход выборки контроллера прямого доступа к памяти подключены соответственно к информационному входу-выходу устройства, входу младших разрядов адреса устройства и к первому выходу первого дешифратора, информационный вход которого подключен к входу старших разрядов адреса устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены два триггера, три элемента И, второй дешифратор, два элемента ИЛИ, два блока накапливающих сумматоров, причем вход установки в О первого триггера соединен с выходом захвата контроллера прямого доступа к памяти, стробирующий выход которого подключен к входу установки в 1 первого триггера и к первому входу первого элемента И, второй вход которого подключен к выходу первого триггера, а выход подключен к первым входам первого и второго элементов ИЛИ, вторые входы которых подключены соответственно к выходам второго и третьего элементов И, а выходы подключены соответственно к первым синхровхо- дам первого и второго блоков накапливающих сумматоров, информационные выходы которых подключены соответственно к выходам младших и старших разрядов адреса устройства, вход и выход переноса первого блока накапливающих сумматоров подключены соответственно к входу логического нуля устройства и к входу переноса второго

блока накапливающих сумматоров, информационные входы первого и второго блоков накапливающих сумматоров соединены с информационным входом-выходом устройства, управляющие входы первого и второго

блоков накапливающих сумматоров подключены к выходу блокировки контроллера прямого доступа к памяти и соединены с первым стробирующим входом первого дешифратора, второй стробирующий вход и

первый выход которого подключены соответственно к входу-выходу записи контроллера прямого доступа к памяти и к стробирующему входу второго дешифратора, а второй и третий выходы подключены

соответственно к вторым синхровходам первого и второго блоков накапливающих сумматоров, информационный вход второго дешифратора подключен к входу младших разрядов адреса устройства, выход второго

дешифратора подключен к первым входам второго и третьего элементов И и к счетному входу второго триггера, вход сброса которого подключен к входу сброса устройства и контроллера прямого доступа к памяти, инверсный и прямой выходы второго триггера подключены соответственно к вторым входам второго и третьего элементов И.

2. Устройство поп. 1,отличающее- с я тем, что блок накапливающего сумматора содержит коммутатор, два регистра, сумматор и шинный формирователь, выход которого подключен к информационному выходу блока, а вход разрешения подключен к управляющему входу блока и коммутатора, выход которого соединен с информационным входом первого регистра, первый информационный вход соединен с информационными входами блока и второго регистра, а второй информационный вход

подключен к информационному входу шинного формирователя, к информационному выходу сумматора, выход и вход переноса которого подключены к выходу и входу переноса блока, первый и второй информационные входы подключены соответственно к выходам первого и второго регистров, син- хровходы которых подключены соответственно к первому и второму синхровходам блока.

выходам первого и второго регистров, син- венно к первому и второму синхровходам хровходы которых подключены соответст- блока.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Устройство для синхронизации обмена микропроцессора с памятью отображения | 1989 |

|

SU1786489A1 |

| Устройство для ввода информации | 1987 |

|

SU1531082A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Программируемый контроллер | 1984 |

|

SU1453404A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство адресации памяти | 1988 |

|

SU1575188A1 |

| Устройство для адресации массивов данных | 1990 |

|

SU1837298A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

Изобретение относится к вычислительной технике, в частности к оперативным запоминающим устройствам, и может быть использовано для оперативной пересылки информационных элементов при разбивке информационных массивов на последовательные группы. Цель изобретения - повышение быстродействия. Устройство содержит контроллер прямого доступа к памяти (КПДП), два накапливающих сумматора, два триггера, два дешифратора, два элемента ИЛИ, три элемента И и входы - выходы адреса, данных и управления. Структура устройства позволяет при инициализации КПДП микропроцессором вносить в регистры накапливающих сумматоров адрес начального элемента передаваемого массива в системной памяти, приращение К. При работе КПДП после захвата шин при передаче К элементов массива накапливающие сумматоры обеспечивают последовательную адресацию К-х элементов массива на адресном выходе. 1 з.п.ф-лы, 3 ил. (Л

| Устройство для адресации | 1986 |

|

SU1361564A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Алексенко А.Г | |||

| и др | |||

| Проектирование радиоэлектронной аппаратуры на микропроцессорах | |||

| М., 1984, с | |||

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-06-15—Публикация

1990-05-18—Подача