1

Изобретение относится к вычислительной технике, в частности к запоминающим yc ройствам электронных вычислительных машин.

Известны долговременные запоминающие устройства для воспроизведения функции, одно из которых содержит входной регистр, вьссоцы которого соединены со входами деитфратора, ши(}раторы и коммутационные поля, подключенные к выходам шифраторов, Известное устройство имеет низкую эффективность работы в реальном масштабе , когда информация поступает на вход устройства непосредственно с преобразова;телей аналог- код. Наиболее близким к

i изобретению техническим решением является устройство, содержащее входной регистр, выходы которого соединены со входами дешифратора, ши(}чраторы, одноименные входы которух соединены с соответствующими выходами дешифратора, а выходы - со входами соответствующих элементов ИЛИ, и первую шину управления, соединенную с перВЕЛи входом входного регистра, ко второму входу которого подключена информационная

шина. Это известное устройство имеет ннэкое быстродействие при работе в реальном масштабе времени из-за невозможности фо мирования управляющих воздействий для исполнительного органа системы управления до полного накопления вхопнов информаоии.

Целью изобретения является увеличение быстродействия. В предлагаемом устройстве это достигается тем, что оно содержит управляющие ключи, блок задержки, счетчик и вторую и третью шины управления, при этом первые входы управляющих ключей и вход блока задержки соединены со второй шиной управления, вторые входы управлшощих ключей, кроме первого, соединены с соответствукхцими выходами дешифратора, выхоа блока задержки подключен к третьему входу входного регистра, а выходы управляющих ключей соединены с управляющим вхог;Дом соответствуюцего шифратора, выходы элементов ИЛИ подключены к одним вэ входов счетчика, другие входы которого соед нены с первой и третьей шинами управления

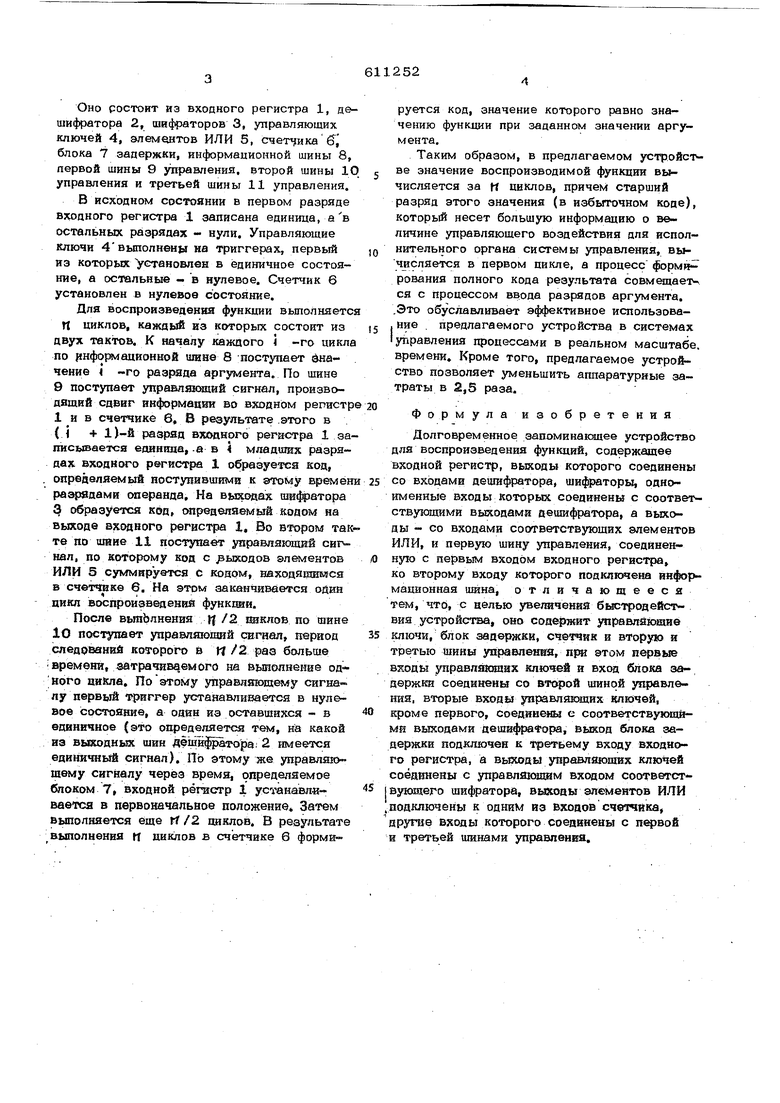

На чертеже представлена структурная схема предлагаемого устройства.

Оно ростонт из входного регистра 1, деши4ратора 2, шифраторов 3, управляющих ключей 4, элементов ИЛИ 5, счет ика б, блока 7 задержки, информационной шины 8, первой шины 9 управления, второй шины 10 управления и третьей шины 11 управления.

В исходном состоянии в первом разряде взсодного регистра 1 записана единица, а в остальньк разрядах - нули. Управляющие ключи 4вьп1олнены на триггерах, первый из которых установлен в единичное состояние, а остальные - в нулевое. Счетчик 6 установлен в нулевое состояние.

Для воспроизведения функции вьшолняетс rt циклов, каждые на которых состоит из двух тактов. К началу каждого 3 -го цикла по информационной шине 8 поступает Значение i -го разряда аргумента. По шине 9 поступает управляющий сигнал, производящий сдвиг ннформвцги во входном репистр 1 и в счетчике 6, В результате этого в С i +1 )-Й разряд входного регистра 1 ааписьшается еаин1ша, .ев 4 младишх разрядах входного регистра 1 образуется код, определяемый ностудившими к этому времен разрядами операнда. На выходах ож втора образуется код, отреаеяяемый кодом на вьпсоце входного регистра 1, Во втором такте по шйие Ц поступает унравяяющий сигнал, по которому код с выходов элементов ИЛИ 5 суммируется с кодом, находяишися в счетчике 6. На этом заканчивается ойин пикл воспроизведения функции.

После вьшЬлнення J| /2 ЕИКЛОВ по шине Ю поступает управляюпшй сигнал, нериоц следований которого в Ц /2 раз больше времени, зйтрачйв емого на &ьшолнение од ного цикла. По этому управляющему сигналу первый Триггер устанавливается в нулевое состояние, а один из оставшихся - в едвнвчное (это определяется тем, на какой из выкоднык шин . 2 имеется единичньй сигнал). По этому же управляв тему сигналу через время, определяемое блоком 7, входной регистр 1 устанавливеется в первоначальное положение. Затем вьшолняется еще ff /2 ЕИКЛОВ. В результате выполнения п никлов в счетчике б формируется код, значение которого равно значению функции при заданном значении аргумента.

Таким образом, в предлагаемом устройст ве значение воспроизводимой функции вычисляется за м циклов, причем старший разряд этого значения (в избыточном коде), который несет большую информацию о величине управляющего воздействия для исполнительного органа системы управления, вычисляется в первом цикле, а процесс формирования полного кода результата совметдается с процессом ввода разрядов аргумента. .Это обуславливает аффективное использова, ние . предлагаемого устройства в системах управления процессами в реальном масштабе, времени. Кроме того, предлагаемое устройство позволяет уменьшить аппаратурные затраты в 2,5 раза.

формулаизобретения

Долговременное запоминающее устройство для воспроизведения функций, содержащее входной регистр, выходы которого соединены со входами дешифратора, ши эаторы, одноименные входы которых соединены с соответствующими вькодами дешифратора, а выходы - со входами соответствующих элементов ИЛИ, и первую шину управления, соедйненкую с nepBbiM входом входного регистра, ко второму входу которого подключена информационная шина, отличающееся тем, что, с нелью увеличений быстродействия устройства, оно содержит управлякдане ключи, блок вдержки, счетчик и вторую и третью шины управления, п{ад этом первые В7,оды управя1 Кзшнх Ключей и вход блока задержки соединены со шиной управления, вторые входы управляющих ключей, кроме первого, соединены е соответствующими выходами дешифг Фора, выход блока задержки подключен к третьему входу входного регистра, а выходы управляющих ключей соёавнены с управляющщм входом соответст(вующего шифратора, выходы элементов ИЛИ . нодключены к одним из входов счетчйка, иругве входы которого соединены с н третьей шинами управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1297225A1 |

| ЦИФРОВОЙ МАГНИТОФОН | 1992 |

|

RU2054715C1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для цифровой магнитной записи-воспроизведения | 1987 |

|

SU1481847A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Устройство для цифровой магнитной записи-воспроизведения | 1990 |

|

SU1770979A1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1999 |

|

RU2173030C2 |

| СИСТЕМА РАДИОВЕЩАНИЯ | 2011 |

|

RU2479926C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Устройство для контроля цифровых узлов | 1987 |

|

SU1571593A1 |

Авторы

Даты

1978-06-15—Публикация

1976-03-18—Подача