Изобретение относится к вычислительной технике и может быть использовано при откладке, контроле и диагностике узлов цифровой вычислительной техники.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения тестирования узлов с двунаправленными выводами.

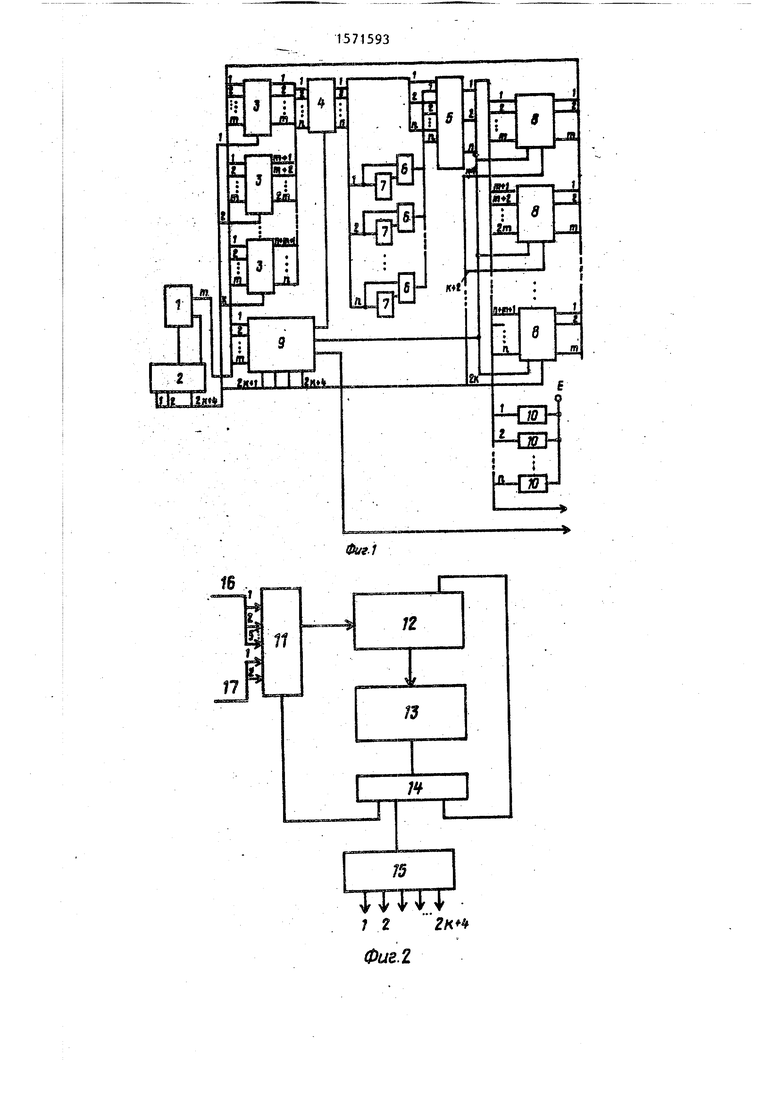

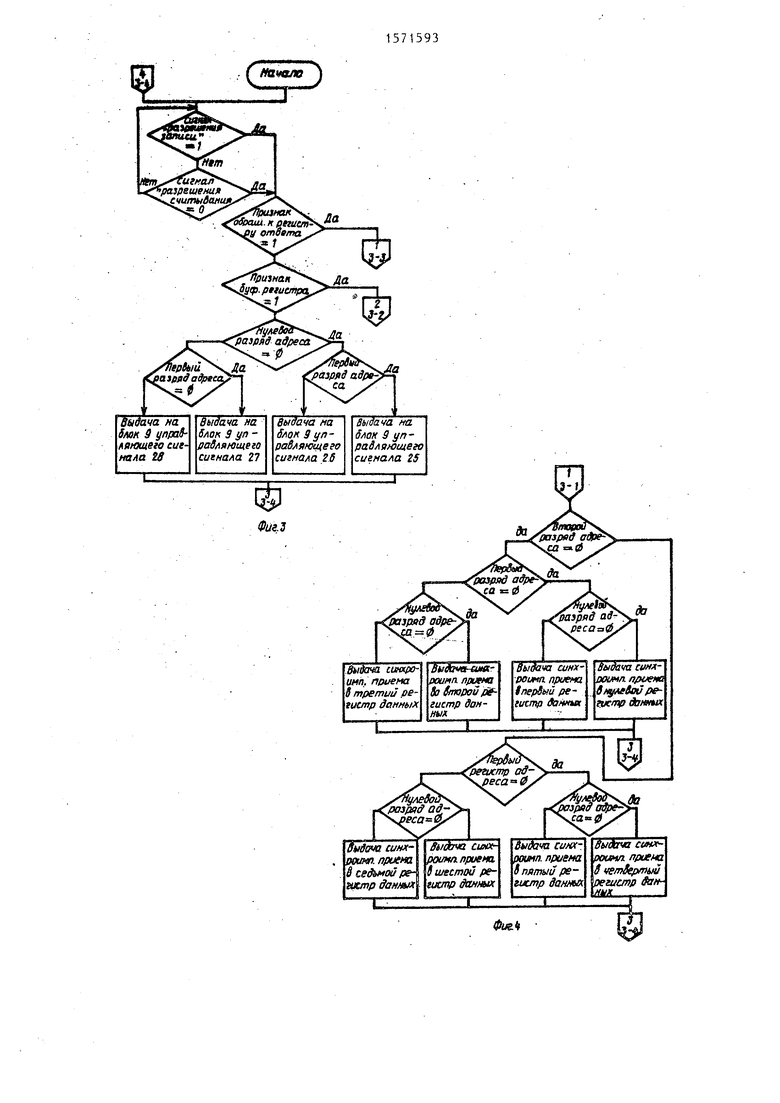

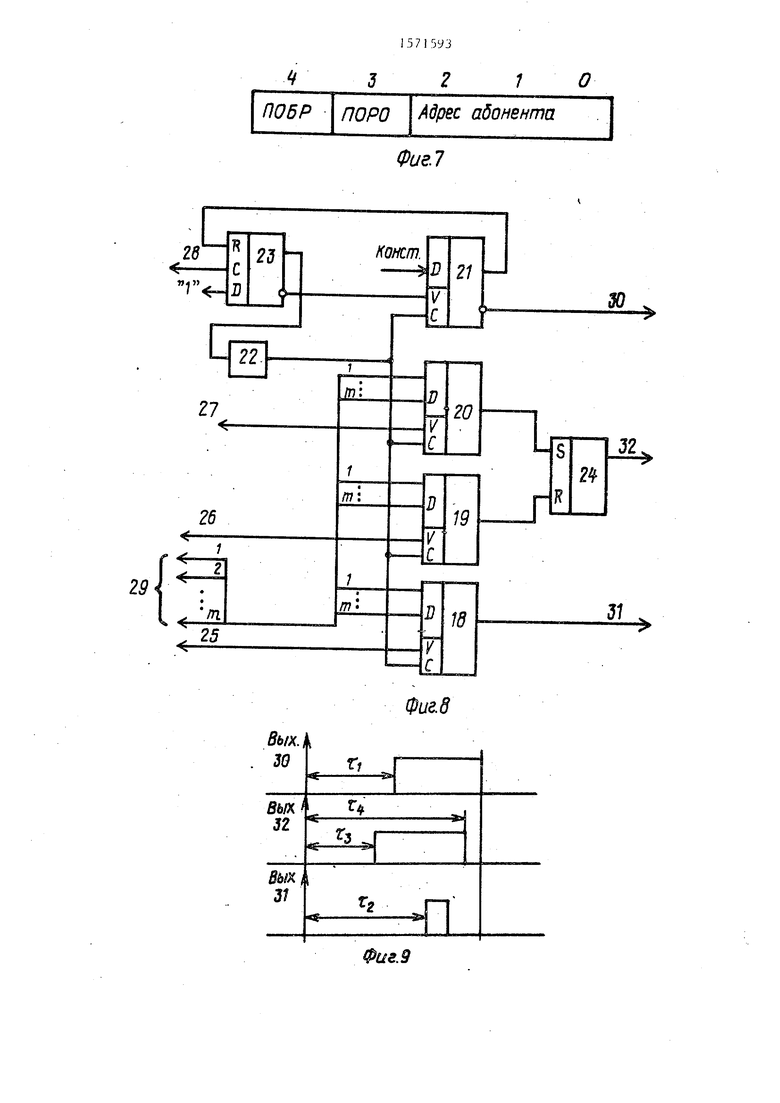

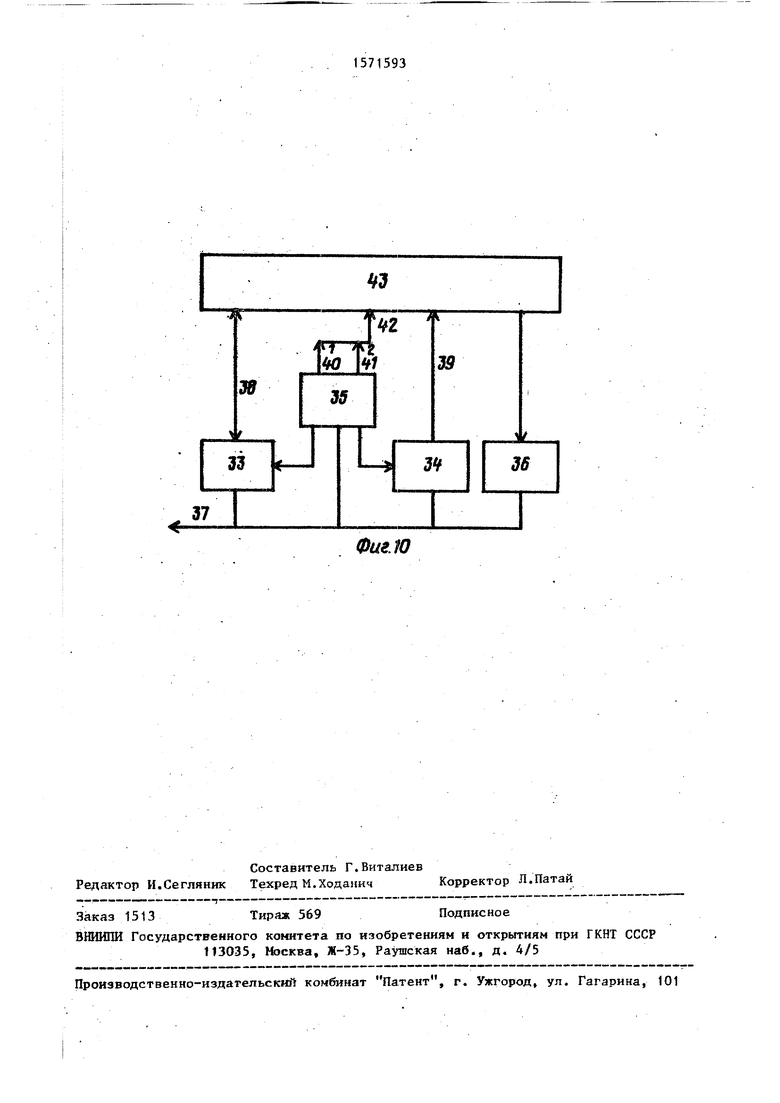

На изображена структурная схема устройства; на фиг.2 - один из возможных примеров блока микропрограммного управления;,на фиг.З - 6 - блок-схема алгоритма работы блока микропрограммного управления; на фиг. формат адреса на входе блока микропрограммного управления; на фиг.8 - один из возможных примеров

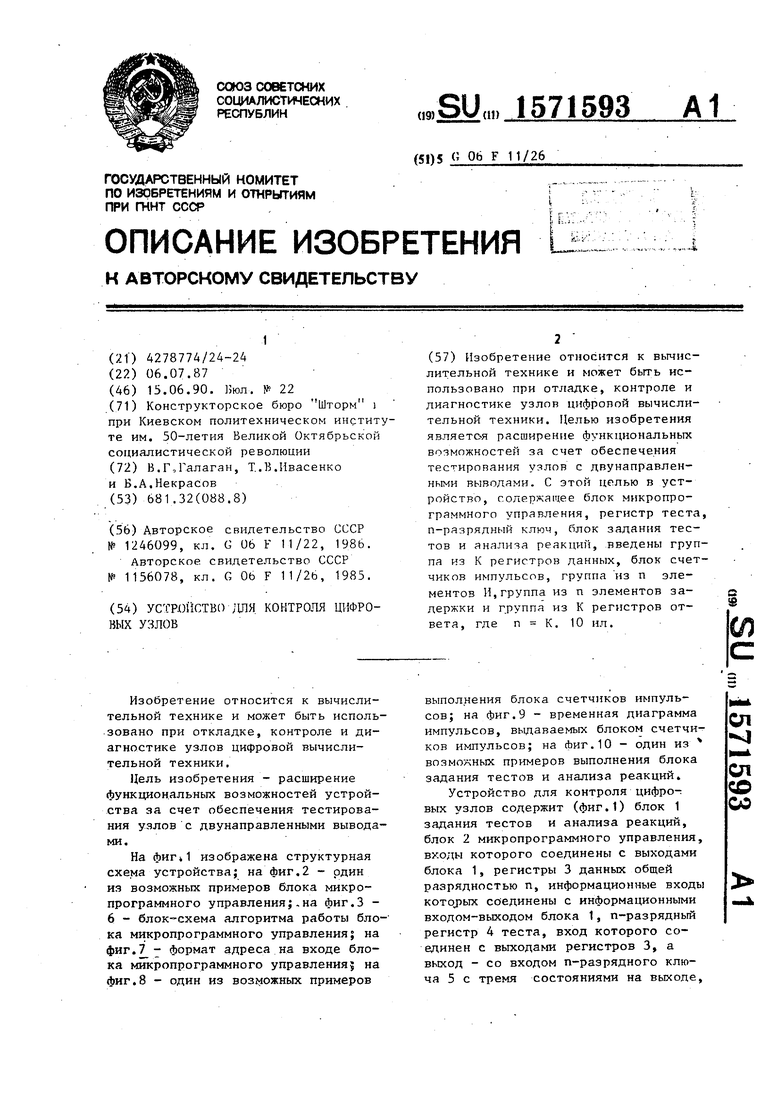

выполнения блока счетчиков импульсов; на фиг.9 - временная диаграмма импульсов, выдаваемых блоком счетчиков импульсов; на сЬиг.10 - один из ВОЗМОАНЫХ примеров выполнения блока задания тестов и анализа реакций Устройство для контроля цифровых узлов содержит (фиг.1) блок 1 задания тестов и анализа реакций, блок 2 микропрограммного управления, входы которого соединены с выходами блока 1, регистры 3 данных общей разрядностью п, информационные входы которых соединены с информационными входом-выходом блока 1, п-разрядный регистр 4 теста, вход которого соединен с выходами регистров 3, а выход - со входом n-раэрядного ключа 5 с тремя состояниями на выходе,

Сл

СЛ

Ј СО

выход которого является выходом устройства для подключения ко входу контролируемого узла. Кроме того, устройство содержит элементы И 6, первые входы которых соединены с соответствующим выходом регистра 4, вторые входы - через элемент 7 задержки - с тем же выходом регистра 4, а выход - с управляющим входом (входом управления третьим состоянием) ключа 5, регистры 8 ответа с тремя устойчивыми состояниями на выходах общей разрядностью п, входы которых подключены к выходам ключа 5, а вы- ходы соединены с информационным входом-выходом блока 1, блок 9 счетчиков импульсов, информационные входы которого подключены к информационному входу-выходу блока 1, управляю- щие входы блока 9 подключены к выходам блока 2, а первый, второй и третий выходы соединены с синхровходом регистра 4 теста, синхровходами регистров 8 ответа и синхровходом объ- екта контроля соответственно. Выходы ключа 5 через резисторы 10 соединены с источником питания, а синхровходы регистров 3 и входы управления считывания (третьим состоянием) регист- ров 8 соединены с выходами блока 2.

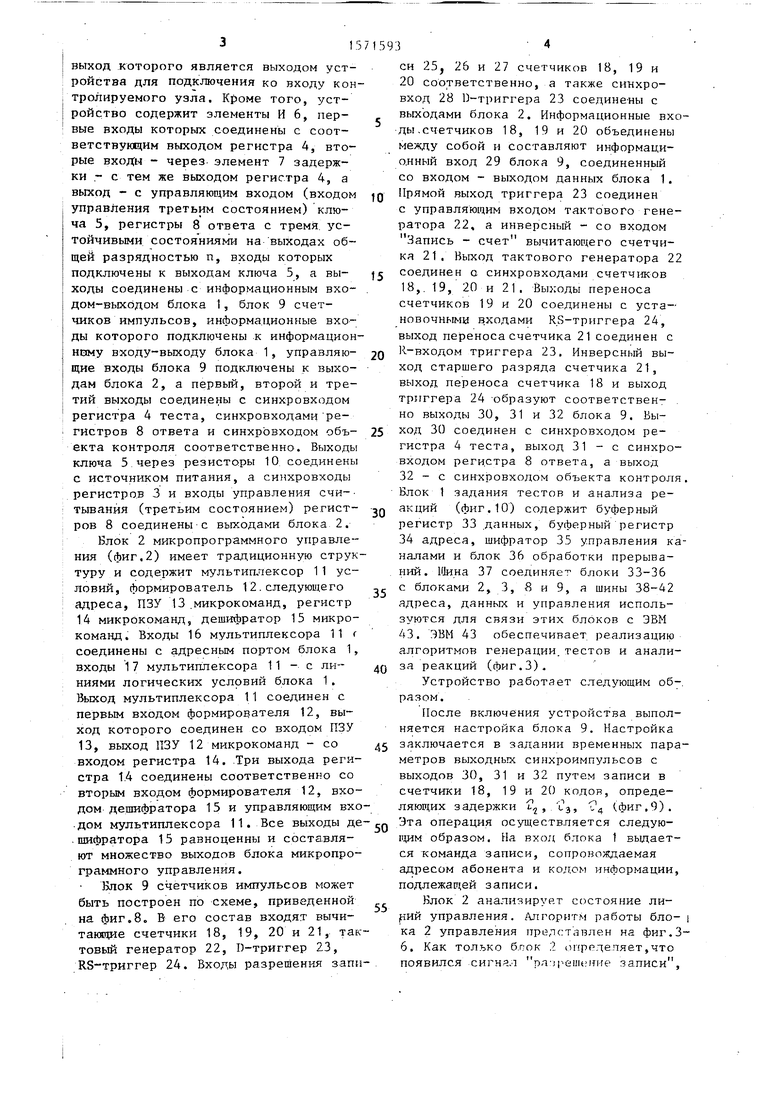

Блок 2 микропрограммного управления (фиг.2) имеет традиционную структуру и содержит мультиплексор 11 условий, формирователь 12 следующего адреса, ПЗУ 13 микрокоманд, регистр 14 микрокоманд, дешифратор 15 микрокоманд. Входы 16 мультиплексора 11 г соединены с адресным портом блока 1, входы 17 мультиплексора 11 - с ли- ниями логических условий блока 1. Выход мультиплексора 11 соединен с первым входом формирователя 12, выход которого соединен со входом ПЗУ 13, выход ПЗУ 12 микрокоманд - со входом регистра 14. Три выхода регистра 14 соединены соответственно со вторым входом формирователя 12, входом дешифратора 15 и управляющим входом мультиплексора 11. Все выходы де шифратора 15 равноценны и составляют множество выходов блока микропрограммного управления.

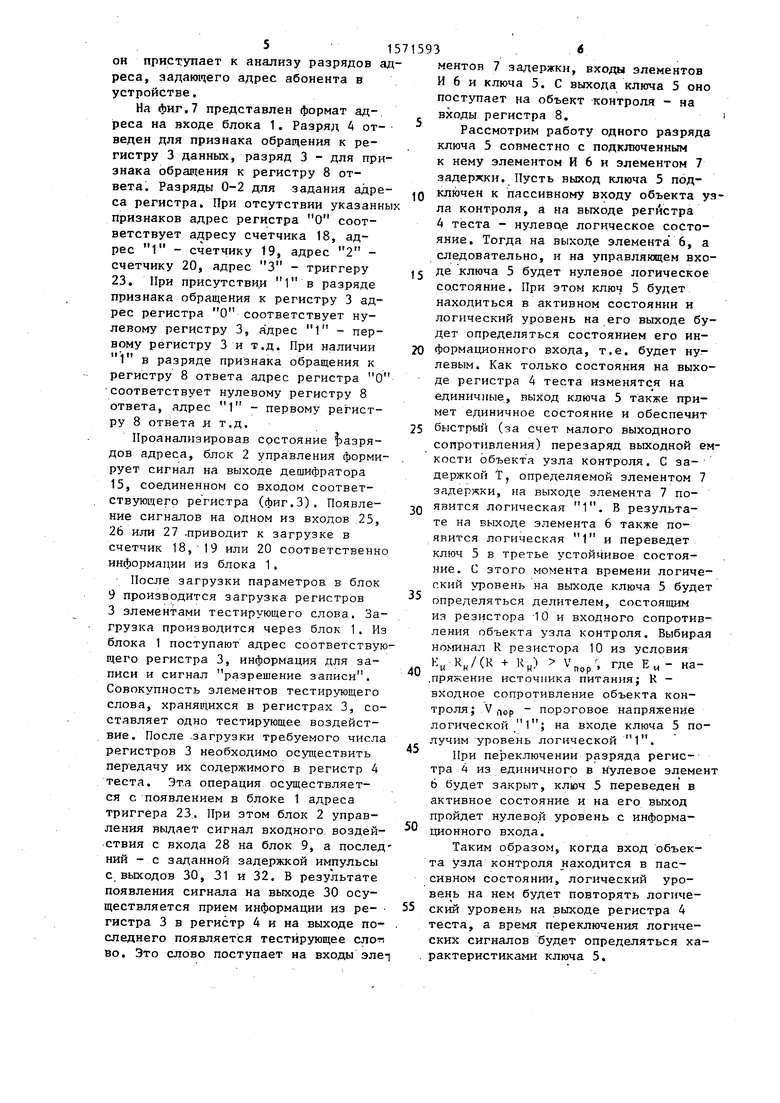

Блок 9 счетчиков импульсов может быть построен по схеме, приведенной на фиг.8„ Б его состав входят вычитающие счетчики 18, 19, 20 и 21, тактовый генератор 22, D-триггер 23, RS-триггер 24. Входы разрешения записи 25, 26 и 27 счетчиков 18, 19 и 20 соответственно, а также синхро- вход 28 1)-триггера 23 соединены с выходами блока 2. Информационные входы.счетчиков 18, 19 и 20 объединены между собой и составляют информационный вход 29 блока 9, соединенный со входом - выходом данных блока 1. Прямой выход триггера 23 соединен с управляющим входом тактового генератора 22, а инверсный - со входом

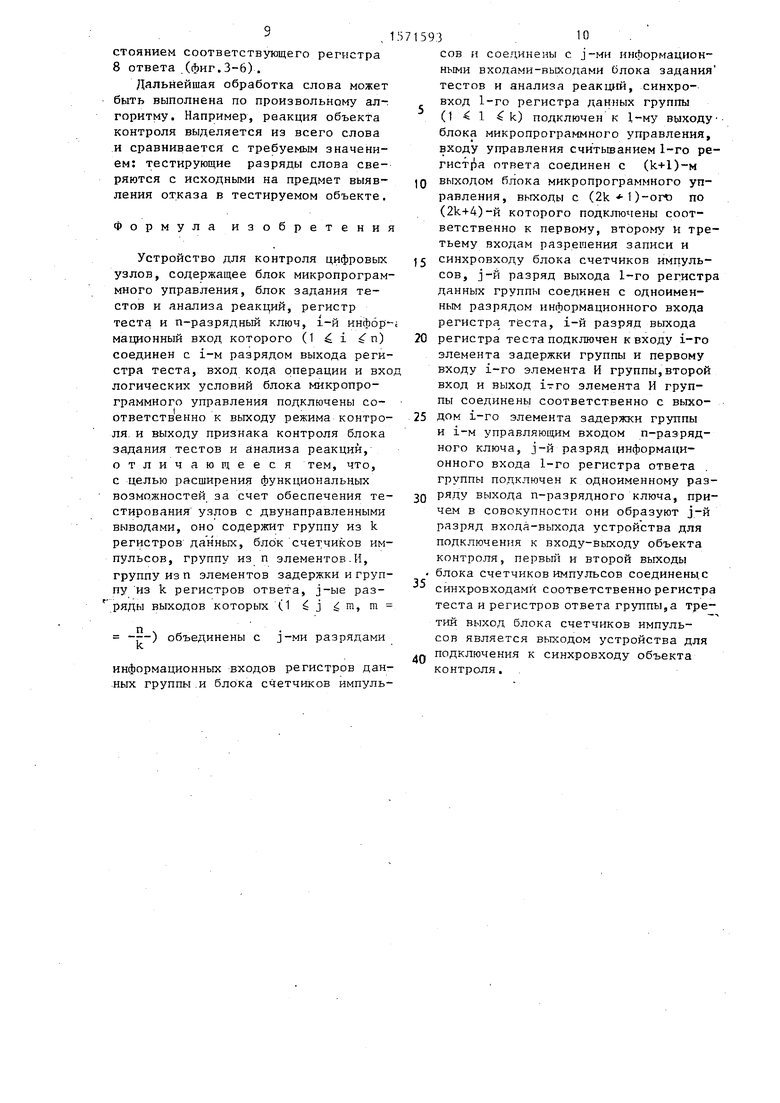

Запись - счет вычитающего счетчика 21. Выход тактового генератора 22 соединен о синхровходами счетчиков 18, 19, 20 и 21. Выходы переноса счетчиков 19 и 20 соединены с установочными входами RS-триггера 24, выход переноса счетчика 21 соединен с Я-входом триггера 23. Инверсный выход старшего разряда счетчика 21, выход переноса счетчика 18 и выход триггера 24 образуют соответственно выходы 30, 31 и 32 блока 9. Выход 30 соединен с синхровходом регистра 4 теста, выход 31 - с синхровходом регистра 8 ответа, а выход 32 - с синхровходом объекта контроля Блок 1 задания тестов и анализа реакций (фиг.10) содержит буферный регистр 33 данных, буферный регистр 34 адреса, шифратор 35 управления каналами и блок 36 обработки прерываний. Шина 37 соединяс блоки 33-36 с блоками 2, 3, 8 и 9, я шины 38-42 адреса, данных и управления используются для связи этих блоков с ЭВМ 3. ЭВМ 43 обеспечивает реализацию алгоритмов генерации.тестов и анализа реакций (Лиг.З).

Устройство работает следующим образом.

После включения устройства выполняется настройка блока 9. Настройка заключается в задании временных параметров выходных синхроимпульсов с выходов 30, 31 и 32 путем записи в счетчики 18, 19 и 20 кодов, определяющих задержки t , э 4 (фиг,1)). Эта операция осуществпяется следующим образом. На вход блока 1 выдается команда записи, сопровождаемая адресом абонента и кодом информации, подлежащей записи.

Блок 2 анализирует состояние линий управления. Алгоритм работы бло- ка 2 управления приставлен на фиг.З 6. Как только бгок о фР1еаяет,что появился сигнал r),i jpeuiemre записи,

51

он приступает к анализу разрядов адреса, задающего адрес абонента в устройстве.

На фиг.7 представлен формат адреса на входе блока 1. Разряд 4 отведен для признака обращения к регистру 3 данных, разряд 3 - для признака обращения к регистру 8 ответа. Разряды 0-2 для задания адреса регистра. При отсутствии указанны признаков адрес регистра О соответствует адресу счетчика 18, адрес 1 - счетчику 19, адрес 2 - счетчику 20, адрес 3 - триггеру 23. При присутствии 1 в разряде признака обращения к регистру 3 адрес регистра О соответствует нулевому регистру 3, адрес 1 - первому регистру 3 и т.д. При наличии 1 в разряде признака обращения к регистру 8 ответа адрес регистра О соответствует нулевому регистру 8 ответа, адрес 1 - первому регистру 8 ответа и т.д.

Проанализировав состояние разрядов адреса, блок 2 управления формирует сигнал на выходе дешифратора 15, соединенном со входом соответствующего регистра (фиг.З). Появление сигналов на одном из входов 25, 26 или 27 -приводит к загрузке в счетчик 18, 19 или 20 соответственно информации из блока 1.

После загрузки параметров в блок 9 производится загрузка регистров 3 элементами тестирующего слова. Загрузка производится через блок 1. Из блока 1 поступают адрес соответствующего регистра 3, информация для записи и сигнал разрешение записи. Совокупность элементов тестирующего слова, хранящихся в регистрах 3, составляет одно тестирующее воздействие. После загрузки требуемого числа регистров 3 необходимо осуществить передачу их содержимого в регистр 4 теста. Эта операция осуществляется с появлением в блоке 1 адреса триггера 23. При этом блок 2 управления выдает сигнал входного воздействия с входа 28 на блок 9, а последний - с заданной задержкой импульсы с,выходов 30, 31 и 32. В результате появления сигнала на выходе 30 осуществляется прием информации из ре- гистра 3 в регистр 4 и на выходе по- следнего появляется тестирующее сло во. Это слово поступает на входы эле

5936

ментов 7 задержки, входы элементов И 6 и ключа 5. С выхода ключа 5 оно поступает на объект контроля - на входы регистра 8.

Рассмотрим работу одного разряда ключа 5 совместно с подключенным к нему элементом И 6 и элементом 7 задержки. Пусть выход ключа 5 подQ ключей к пассивному входу объекта узла контроля, а на выходе регистра 4 теста - нулевое логическое состояние. Тогда на выходе элемента 6, а следовательно, и на управляющем вхос де ключа 5 будет нулевое логическое состояние. При этом ключ 5 будет находиться в активном состоянии н логический уровень на его выходе будет определяться состоянием его ин0 формационного входа, т.е. будет нулевым. Как только состояния на выходе регистра 4 теста изменятся на единичные, выход ключа 5 также примет единичное состояние и обеспечит

5 быстрый (за счет малого выходного

сопротивления) перезаряд выходной емкости объекта узла контроля. С задержкой Т определяемой элементом 7 задержки, на выходе элемента 7 поQ явится логическая 1. В результате на выходе элемента 6 также появится логическая 1 и переведет ключ 5 в третье устойчивое состояние. С этого момента времени логический уровень на выходе ключа 5 будет

определяться делителем, состоящим из резистора 10 и входного сопротивления объекта узла контроля. Выбирая номинал R резистора 10 из условия К„ V(K + Кн) Vnop , где Ем- на- .прякение источника питания; R - входное сопротивление объекта контроля; V пор - пороговое напряжение логической на входе ключа 5 получим уровень логической 1.

При переключении разряда регистра 4 из единичного в нулевое элемент 6 будет закрыт, ключ 5 переведен в активное состояние и на его выход пройдет нулевой уровень с информационного входа.

Таким образом, когда вход объекта узла контроля находится в пассивном состоянии, логический уровень на нем будет повторять логиче5 ский уровень на выходе регистра 4 теста, а время переключения логических сигналов будет определяться характеристиками ключа 5.

0

Пусть, вход объекта контроля находится в активном состоянии (т.е. является выходом). В этой ситуации логический уровень на выходе ключа 5 должен определяться состоянием объекта контроля. Это условие может быть выполнено за счет перевода ключа 5 в третье устойчивое1 состояние путем установки разрядов регистра 4 теста в 1.

Таким образом, предложенная схема включения элементов 7 (в качестве элемента 7 задержки мржет быть использована RC-цепочка), элементов 6, резисторов 10 и ключа 5 обеспечивает как подачу тестирующих воздействий на объект контроля, так и получение с него результатов тестирования .

Тестирующее слово на выходе ключа 5 сопровождается синхроимпульсом, . выдаваемым блоком 9 с выхода 32. Параметры импульса и его временное расположение относительно момента приема в регистр 4 теста задается «а этапе настройки блока 9. Струтура блока 9 может быть построена, в соответствии с фиг.8.

Этот блок обеспечивает управление временными параметрами синхроимпульсов при помощи кодов, загружаемых в его счетчики по входу 29 из блока 1. Из блока 1 в блок 9 поступают три m-ра зрядных кодов; код 1 код €3 , код Јq. , загружаемые в счетчики 18, 20, 19 соответственно путем подачи сигналов управления на выходы 25, 27, 26 соответственно. Названные три кода определяют временые соотношения и форму синхроимпульсов, приведенную на Лиг.9, где временные интвервалы 7, з 4пропорциональны кодам:

код

Јэ, код С,,., причем интервал .,

2 код

1 а

также длительности первого и второго синхроимпульсов фиксированы..Отсчет временных интервалов осуществляется от переднего фронта импульса входного воздействия, поступившего на вход 28 с блока 2 управле- , ния. Коэффициент пропорциональности между кодом и соответствующим интервалом определяется периодом Т г тактового генератора 22, работающего в стартостопном режиме, т.е. Ј код

-П m

(, if.

Значение периода Т f может достигать 10 не при исполнении управляющи

0

5

0

5

0

5

0

5

0

5

m

формирователей на микросхемах быстро действующей эмиттер.но-связанной логики (например, серии 500). Разрядность кодов обычно может приниматься равной 7-12 двоичных разрядов в зависимости от максимальных значений временных интервалов. Эта константа записывается в счетчик по сигналу с триггера 23. Приход синхроимпульса на вход 28 прекращает запись в счетчик1 21, разрешая счет.

После загрузки в счетчики 18, 20, 19 кодов j , 3 , 4 из блока 1 и загрузки в счетчик 21 константы (2 - 1) подается сигнал запуска на вход 28 блока 9, по переднему фронту которого устанавливается триггер 23. Прямой выход триггера 23 включает генератор 22, инверсный устанавливает режим вычитания счетчика 21. Под воздействием тактовых импульсов происходит вычитание кодов из всех счетчиков. По достижении нулевого значения кода в каждом счетчике формируется импульс переноса, временное положение которого смещено относительно сигнала с входа 28 управления на время, пропорциональное коду. Па первом выходе 30 синхроимпульс появляется, когда код в счетчике 21 станет равным 2ГТ)1 - 1 . По достижении нулевого значения кода в счетчике 21 формируется импульс переноса, который сбрасывает триггер 23 по входу сброса. Выходы переноса счетчиков 19 и 20, воздействуя на KS-входы триггера 24, обеспечивают формирование на выходе триггера синхроимпульса с выхода 32 для объекта контроля положительной полярности.

Разряды тестирующего слова и разряды реакции объекта узла контроля поступают на вход регистра 8 ответа.. Момент приема в регистр 8 определяется импульсом с выхода 31 из блока 9. Временной сдвиг импульса относительно момента приема в регистр 4 теста определяется на этапе настройки блока 9. После приема информации в регистры 8 ответа может выполняться ее считывание.. Чтение производится путем выдачи команды чтения и соответствующего адреса. Блок 2 управления, выделив сигнал разрешение считывания и проанализировав разряды адресного порта, выдает сигнал на выходе дешифратора 15, соединенном со входом управления третьим соУП 7

тоянием соответствующего регистра ответа (фиг.3-6).

Дальнейшая обработка слова может быть выполнена по произвольному алгоритму. Например, реакция объекта контроля выделяется из всего слова и сравнивается с требуемым значением: тестирующие разряды слова сверяются с исходными на предмет выявления отказа в тестируемом объекте.

Формула изобретения

Устройство для контроля цифровых узлов, содержащее блок микропрограммного управления, блок задания тестов и анализа реакций, регистр теста и n-разрядный ключ, i-й инфор- мационный вход которого (1 i п) соединен с i-м разрядом выхода регистра теста, вход кода операции и вход огических условий блока микропрограммного управления подключены соответственно к выходу режима контроля и выходу признака контроля блока задания тестов и анализа реакций, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения тестирования узлов с двунаправленными выводами, оно содержит группу из k регистров данных, блок счетчиков импульсов, группу из п элементов И, группу изп элементов задержки и группу из k регистров ответа, j-ые раз- ряды выходов которых (1 j Ј га, m

-г-) объединены с j-ми разрядами к.

информационных входов регистров данных группы и блока счетчиков импуль3Ю

сов и соединены с j-ми информационными входами-выходами блока задания тестов и анализа реакции, синхро- вход 1-го регистра данных группы (1 1 k) подключен к 1-му выходу блока микропрограммного управления, входу управления считыванием 1-го регистра ответа соединен с (k+l)-M

выходом блока микропрограммного управления, выходы с ()-ort) по (2k+4)-ft которого подключены соответственно к первому, второму и третьему входам разрешения записи и

синхровходу блока счетчиков импульсов, j-й разряд выхода 1-го регистра данных группы соединен с одноименным разрядом информационного входа регистра теста, i-й разряд выхода

регистра теста подключен к входу 1-го элемента задержки группы и первому входу 1-го элемента И группы,второй вход и выход irro элемента И группы соединены соответственно с выходом 1-го элемента задержки группы и i-м управляющим входом n-разрядного ключа, j-й разряд информационного входа 1-го регистра ответа группы подключен к одноименному разряду выхода n-разрядного ключа, причем в совокупности они образуют j-й разряд входа-выхода устройства для подключения к входу-выходу объекта контроля, первый и второй выходы блока счетчиков импульсов соединены с синхровходами соответственно регистра теста и регистров ответа группы,а тре-

- ч

тий выход блока счетчиков импульсов является выходом устройства для подключения к синхровходу объекта контроля.

to

i-Ь-Е1

о

чаРГ.

Р--Н

м

F-rr

П м ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для контроля логических блоков | 1987 |

|

SU1432529A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

Изобретение относится к вычислительной технике и может быть использовано при отладке, контроле и диагностике узлов цифровой вычислительной техники. Целью изобретения является расширение функциональных возможностей за счет обеспечения тестирования узлов с двунаправленными выводами. С этой целью в устройство, содержащее блок микропрограммного управления, регистр теста, N-разрядный ключ, блок задания тестов и анализа реакций, введены группа из K регистров данных, блок счетчиков импульсов, группа из N элементов И, группа из N элементов задержки и группа из K регистров ответа, где N=K. 10 ил.

% -«s

isa «

J

«Э

иш м+

I -Г1-:

Ui

J

Ul

vo

LO

гч

SL

t

Щ

fern.

3

Hff

r. n

1

E±

V

-Or«

IU-. 1TL

Фиг.З

Разрешение Выдачи информации из ну- леооео рееис- оа данных

Фие.7

Фие.8

м

гу- 40

J5

33

Я

39

3

J5

Фие.Ю

Авторы

Даты

1990-06-15—Публикация

1987-07-06—Подача