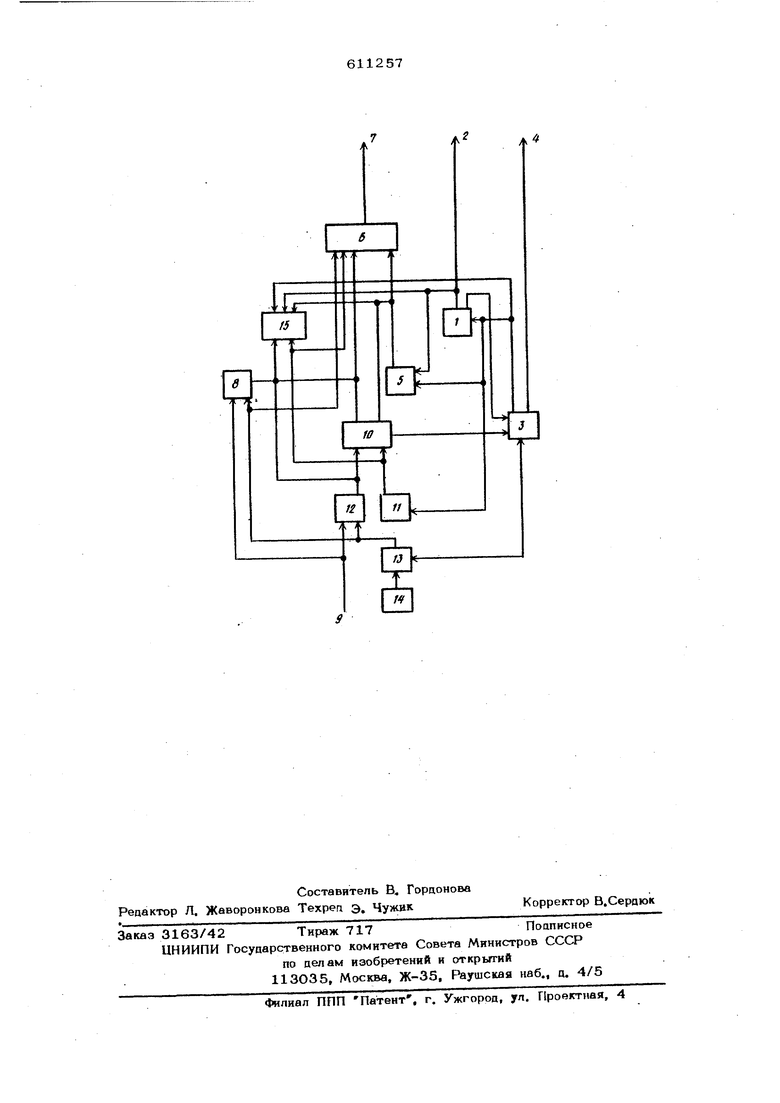

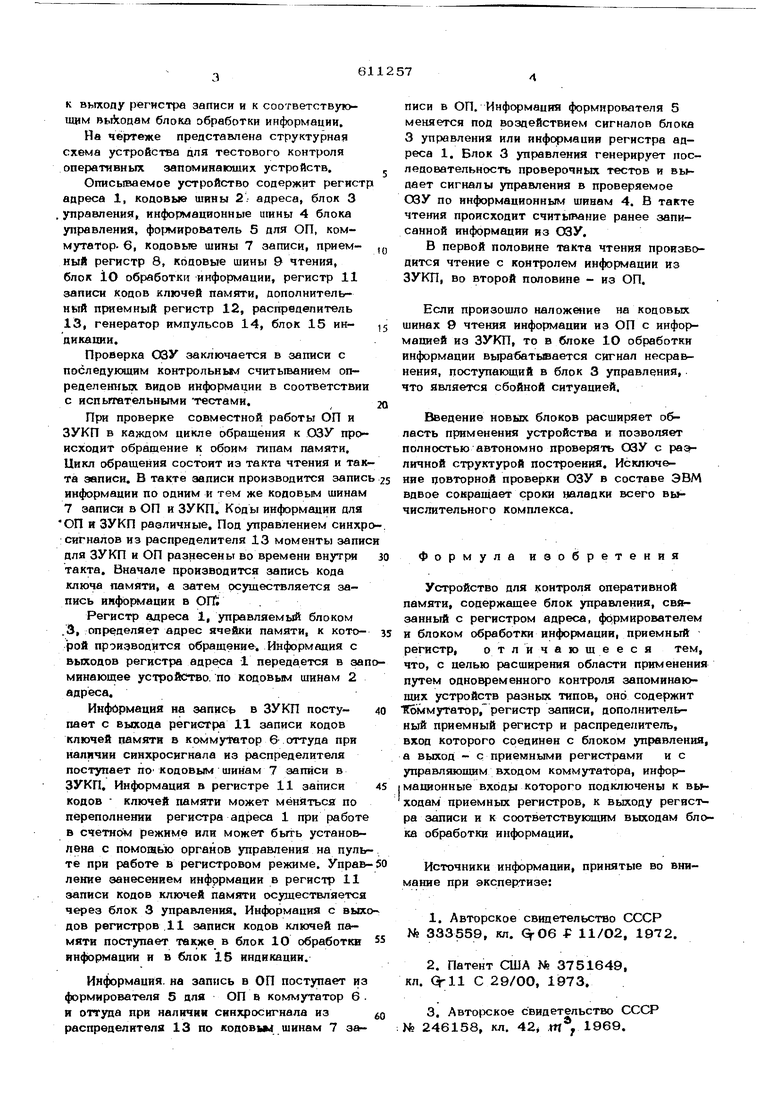

к выходу регистра записи и к соответствующим вьАоцам блока обработки иртформации. На чертеже представлена структурная схема устройства для тестового контроля оперативных запоминающих устройств.

Описываемое устройство содержит регистр адреса 1, кодовые шины 2. адреса, блок 3 управления, информационные ишны 4 блока управления, формирователь 5 для ОП, коммутатор- 6, коповьге шины 7 записи, приемный регистр 8, кодовые шины 9 чтения, блок iO обработки информации, регистр 11 записи кодов ключей памяти, дополнительный приемный регистр 12, распределитель 13, генератор импульсов 14, блок 15 ин- дикации.

Проверка ОЗУ заключается в записи с последукмдим контрольным считыванием определенных видов информации в соответствии с испытательными тестами,

При проверке совместной работы ОП и ЗУКП в каждом цикле обращения к ОЗУ происходит обращение к обоим гипам памяти. Цикл обращения состоит из такта чтения и такта записи. В такте записи производится запись информации по одним и тем же кодовым шинам 7 записи в ОП и ЗУКП, Коды информации для ОП н ЗУКП различные. Под управлением синхр сигналов из распределителя 13 моменты запис для ЗУКП и ОП разнесены во времени внутри такта. Вначале производится запись кода ключа памяти, а затем осуществляется запись информации в OTti. Регистр адреса 1, управляемый блоком .3, определяет адрес ячейки памяти, к которой производится обращение. Информация с выходов регистра адреса 1 передается в запминаюц1ее устройство, по кодовьвл шинам 2 адреса.

Информация на записи в ЗУКП поступает с выхода регистре 11 записи кодов ключей памяти в коммутатор 6 оттуда при наличии синхросигнала из распределителя поступает пОкодовым шинам 7 записи в ЗУКП. Информация в регистре 11 записи кодов ключей памяти может мён)яться по переполнении регистра адреса 1 при работе в счетном режиме или может быть установлена с помощью органов управления на пульте при работе в регистровом режиме. Управление занесением инфррмации в регистр 11 записи кодов ключей памяти осуществляется через блок 3 управления. Информация с выходов регистров 11 записи кодов ключей памяти поступает также в блок 10 обработки информации и в блок 15 индикации.

Информация, на запись в ОП поступает из формирователя 5 цля ОП в коммутатор 6 . и оттуда при наличии синхросигнала из

распределителя 13 по кодовым шинам 7 записи в ОП. Информация формирователя 5 меняется под воздействием сигналов блока 3 управления или информаиии регистра адреса 1. БЛОК 3 управления генерирует последовательность проверочных тестов и выдает сигналы управления в проверяемое ОЗУ по информационным шинам 4. В такте чтения происходит считывание ранее записанной информации из ОЗУ.

В первой половине такта чтения производится чтение с контролем информации из ЗУКП, во второй половине - из ОП.

Если произошло наложение на кодовых шинах 9 чтения информации из ОП с информацией из ЗУКП, то в блоке 1О обработки информации вьфабат1Жается сигнал несравнения, поступающий в блок 3 управления,. что является сбойной ситуацией.

Введение новых блоков расширяет область применения устройства и позволяет полностью автономно проверять ОЗУ с радличной структурой построения. Исключение повторной проверки ОЗУ в составе ЭВМ вдвое сокращает сроют наладки всего вычислительного комплекса.

Формула изобретения

Устройство для коитроля оперативной памяти, содержащее блок управления, связанный с регистром адреса, формирователем и блоком обработки инфo лvIaции, приемный регистр, отличающееся тем, что, с целью расширения области применения путем одновременного контроля запоминающих устройств разных типов, оно содержит Коммутатор, регистр записи, дополнительный приемный регистр и распределитель, вход которого соединен с блоком управления, а выход - с приемными регистрами и с управляющим входом коммутатора, инфор|мационные входы которого подключены к вььходам приемных регистров, к выходу регистра записи и к соответствующим выходам блока обработки информации.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР NO 333559, кл. Q-O6 Р 11/О2, 1972.

2.Патент США М 3751649, кл. 0-11 С 29/00, 1973,

3.ABTOtKiKoe свидетельство СССР № 246158, кл. 42, ,т®, 1969.

N

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957278A1 |

| Многоканальное устройство для формирования временных интервалов | 1980 |

|

SU932603A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для отображения информации | 1987 |

|

SU1571646A1 |

| Система телемеханики | 1982 |

|

SU1152015A1 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

| Устройство для контроля печатных плат | 1986 |

|

SU1472929A1 |

LB

/f //

Авторы

Даты

1978-06-15—Публикация

1976-08-10—Подача