Изобретение относится к запоминающим устройствам.

Известны устройства для контроля блоков оперативной памяти (1 и 2.

Одно из известных устройство содержит блок формирования данных, блок формирования адресов, блок управления 1.

Недостатком этого устройства является низкая надежность.

Наиболее близким техническим решением к предлагаемому является устройство для контроля блоков оперативной памяти, содержащее регистр адреса, блок управления, блок формирования информации на запись для оперативной памяти, блок выдачи информации, регистр приема информации из оперативной памяти, блок обработки информации, регистр записи кодов ключей памяти, приемный регистр кодов ключей памяти, блок индикации 2.

Недостатками этого устройства являются низкая надежность, так как оно не обеспечивает проверку блоков оперативной памяти с многомодульной структурой и низкое быстродействие, поскольку оно не обеспечивает быстрой локализации неисправностей и в нем отсутствует программируемый

интерфейс, что не позволяет с высокой точностью задавать временные параметры сигналов управления.

Цель изобретения - повыщение надежности и быстродействия устройства.

Поставленная цель достигается тем, что в устройство для контроля блоков оперативной памяти, содержащее синхронизатор, регистр адреса, блок управления, блок приема и выдачи информации, блок обнаружения ошибок, индикатор и формирователь

10 тестовых сигналов, первый и второй входы которого подключены соответственно к первым входам блока управления и регистра адреса, выходу синхронизатора и выходу блока управления, входу синхронизатора, первым входам индикатора и блока обнаружения ощибок и второму входу pel истра адреса, выход которого соединен с первым входом блока приема и выдачи- информации, вторым входом индикатора и третьим вхо2Q дом формирователя тестовых сигналов, четвертый вход и выход которого подключены соответственно к вторым входам блока обнаружения ошибок и блока приема и выдачи информации и к третьим входам блока приема и выдачи информации и блока обнаружения ошибок, выход и четвертый вход которого соеди-нены соответственно с вторым входом блока управления и третьим входом индикатора и с одним из выходов блока приема и выдачи информации, четвертый вход и другие выходы которого являются соответственно входом считывания, адресными и управляющими выходами и выходом записи устройства, введены блок диагностики, первый коммутатор и многоканальный программируемый блок задания временной диаграммы, управляющие входы которого соединены с первыми входами коммутатора и блока диагностики и выходом блока управления, входы синхронизации с выходом синхронизатора, а выход с вторыми входами блока обнаружения ошибок и блока диагностики, третий и четвертый входы которого подключены соответственно к выходу и к третьему входу блока обнаружения ошибок, выход и пятый вход блока диагностики соединены соответственно с третьим входом блока управления и с одним из выходов блока приема и выдачи информации и вторым входом коммутатора, выход которого подключен к пятому входу блока приема и выдачИ информации.

Многоканальный программируемый блок задания временной диаграммы содержит в каждом канале триггеры, второй коммутатор и схемы свертки по модулю два, выходы которых подключены соответственно к входам заггуска первого-четвертого триггеров,, входы установки в «единицу пятого и шестого триггеров соединены соответственно с выходами первого и третьего триггеров, а входы установки в «ноль пятого и щестого триггеров соответственно с выходами второго и четвертого триггеров, выходы пятого и шестого триггеров подключены к одним из входов второго коммутатора, выход которого является выходом блока, управляющими входами которого являются прямые и инверсные установочные входы первого- четвертого триггеров и одни из входов схем свертки по модулю два, другие входы которых, входы синхронизации триггеров и другие входы первого коммутатора являются входами синхронизац,ии блока.

Кроме того, блок диагностики содержит схемы сравнения, третий, четвертый и пятый коммутаторы и седьмой триггер, причем выходы первой и второй схем сравнения подключены к первым входам третьего и четвертого коммутаторов соответственно выходы третьей и четвертой схем сравнения сое- . динены соответственно с вторыми входами третьего и четвертого коммутаторов, выходы которых подключены к первому и второму входам пятого коммутатора, выход которого соединен с входом запуска седьмого триггера, выходы которого являются выходами блока, третьи и четвертые входы третьего- пятого коммутаторов и прямой и инверсный установочные входы седьмого триггера яв« ляются первым входом блока, вторым входом которого является управляющий вход седьмого триггера, одни из входов первой схемы сравнения и входы третьей схемы сравнения являются третьим входом блока, другие входы первой схемы сравнения и одни из входов второй схемы сравнения являются четвертым входом блока, пятым входом которого являются другие входы второй и входы четвертой схем сравнения.

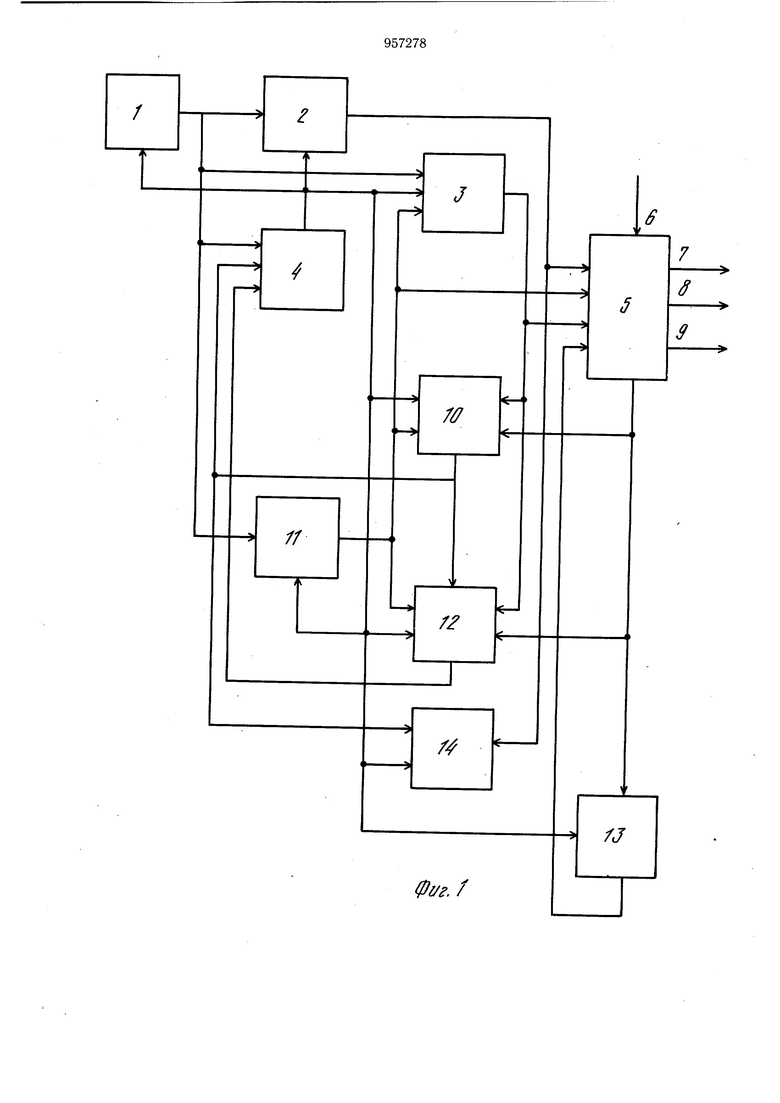

На фиг. 1 приведена функциональная

схема устройства; на фиг. 2 и 3 изображены функциональные схемы соответственно многоканального программируемого блока задания временной диаграммы и блока диагностики.

Устройство содержит (фиг. 1) синхронизатор 1, регистр 2 адреса, формирователь 3 тестовых сигналов, блок 4 управления, блок 5 приема и выдачи информации. На фиг. 1 обозначены вход 6 считывания устройства, адресные 7, управляющие 8 выходы и выход

9 записи устройства.

Устройство содержит также блок 10 обнаружения ошибок, многоканальный программируемый блок 11 задания временной диаграммы, блок 12 диагностики, первый коммутатор 13 и индикатор 14.

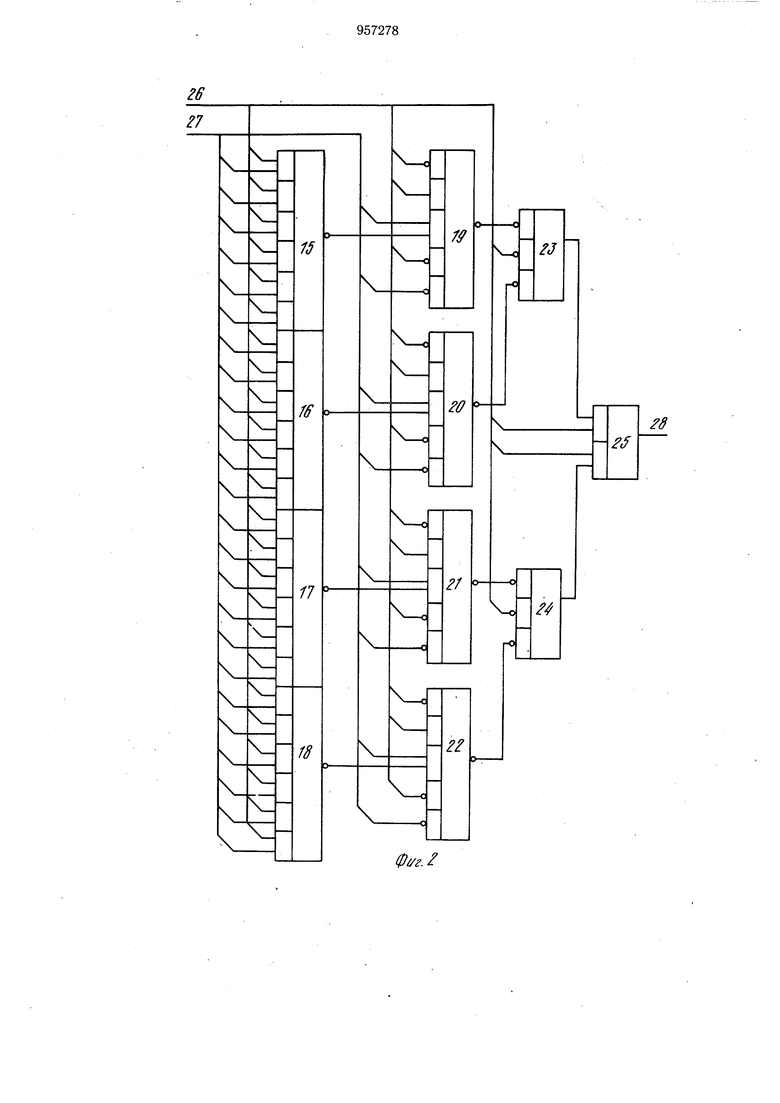

Многоканальный программируемый блок задания временной диаграммы содержит (фиг. 2) в каждом канале схемы 15 - 18 свертки по модулю два, первый - шестой триггеры 19 - 24 и второй коммутатор 25.

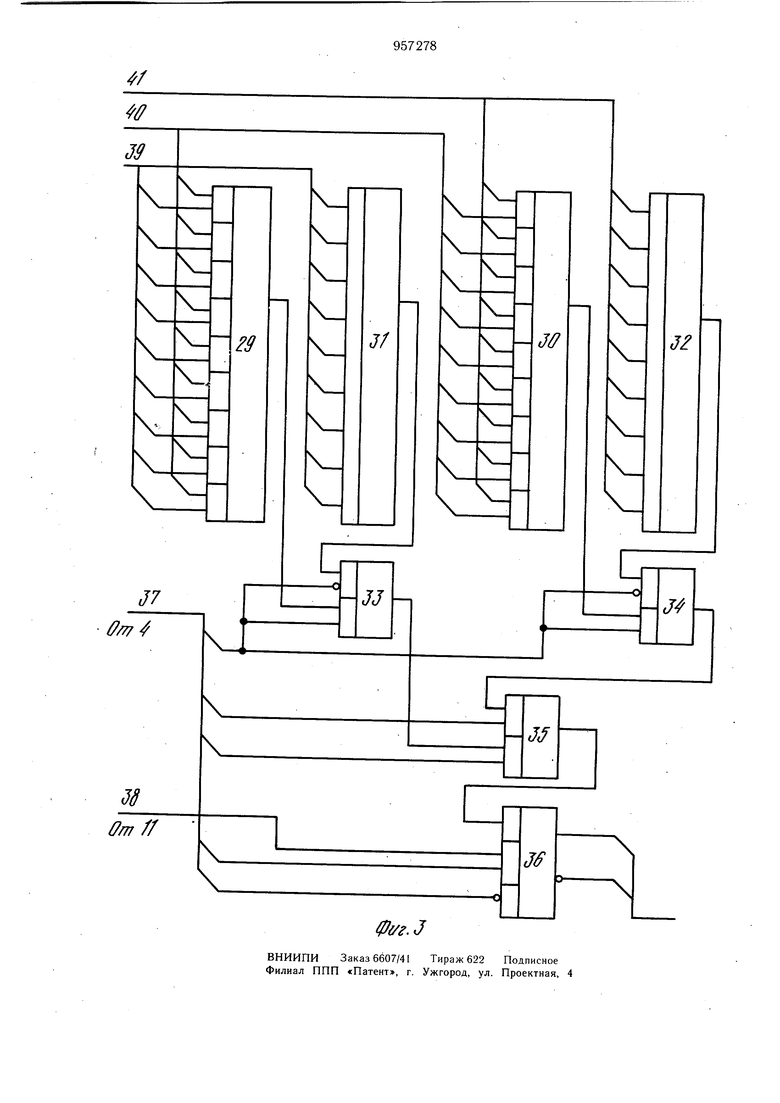

0 На фиг. 2 обозначены входы синхронизации 26 и управляющие 27 и выход 28 блока. Блок диагностики (фиг. 3) содержит первую 29, вторую 30, третью 31 и четвертую 32 схемы сравнения, третий 33, четвертый 34 и пятый 35 коммутаторы и седьмой триггер 36. На

5 фиг. 3 обозначены первый 37, второй 38, третий 39, четвертый 40 и пятый 41 входы блока.

Устройство работает следующим образом.

Контроль блока оперативной памяти (ОЗУ) заключается в записи с последующим контрольным считыванием определенных видов информации в соответствии с контрольно-диагностическими тестами.

При проверке работы ОЗУ в каждом цикле происходит обращение ко всем модулям памяти (ПМ) ОЗУ. Цикл обращения состоит из такта чтения с последующим контролем считанной информации и такта записи. При переходе на автономную проверку произвольного модуля памяти ОЗУ устройство переключается на интерфейс ПМ и вырабатывает временную диаграмму сигналов обращения в МП.

Синхронизатор 1 (фиг. 1), управляемый 5 блоком 4, вырабатывает запускающие синхросерии сигналов, синхронизирующие работу основных логических блоков устройства.

Регистр 2 (фиг. 1) формирует код адреса, по которому производится обращение к ячейке памяти. Информация кода адреса передается в запоминающее устройство через блок 5 по выходам 7. Информация кода адреса также поступает в формирователь 3 для формирования тестовой информации на запись.

Данные на запись в ОЗУ и алгоритм проверки формируются формирователем 3 под воздействием управляющих сигналов блока 4 и программируемого блока 11. Блок 5 осуществляет передачу в ОЗУ информации из формирователя 3, регистра 2, сигналов управления из блока 11, осуществляет прием считанной информации из проверяемого объекта и производит преобразование и согласование уровней сигналов интерфейса «устройство контроля - ОЗУ.

Блок 4 анализирует работу блока 10, блока 12, а также управляет функционированием логических блоков устройства. Программируемый блок 11 формирует временные последовательности сигналов, которые передаются в запоминаю1дее устройство через блок 5 по выходам 8. Временные соотнощения сигналов управления задаются программой из блока 4. Это обеспечивает возможность автоматически выставлять временные параметры и соотнощения сигналов в широком диапазоне с высокой точностью, что является важным критерием при разработке контрольно-диагностических систем для проверки быстродействующих устройств. Считанная информация по входам б через блок 5 поступает в блок 10, где под воздействием управляющих сигналов блока 4 и блока 11 осуществляется ее обработка и поразрядное сравнение с эталонной. При считывании неверной информации вырабатывается сигнал сбоя, поступающий в блок 4, и под воздействием его происходит останов работы устройства. В индикаторе 14 регистрируется сбойный разряд считанной информации из ОЗУ, номер неисправного МП и адрес неисправной ячейки памяти.

Программируемый блок 11 (фиг. 1 и 2) формирует временные последовательности сигналов управления. Каждый из сигналов управления формируется независимым каналом.

Канал работает следующим образом.

Схемы 15-18 свертки по модулю два осуществляют поразрядное сложение по модулю два выходных сигналов п-разрядного счетчика, весов п-разрядного кода 2°, 2, 2...2 с пульта управления (не показан) устройства и их свертку. Сигналы свертки поступают на входы соответствующих триггеров 19-22, которые формируют управляющие сигналы для триггеров 23 и 24. Установкой п-разрядного кода на пульте обеспечивается формирование триггерами 23 и 24 сигнала, задержка и длительность .которого определяется программным набором. Выходные сигналы триггеров 19 и 21 устанавливают триггеры 23 и 24 в единичное состояние, причем формируется передний фронт сигнала. Задний фронт сигнала 2 формируется установкой триггеров 23 и 24 в

нулевое состояние под воздействием выходных сигналов триггеров 20 и 22. Дискретным изменением весов п-разрядного кода обеспечивается установка задержки и длительности выходных сигналов триггеров 23 и 24 с высокой точностью. С помощью коммутатора 25 обеспечивается выдача на выход канала определенной временной последовательности сигналов управления в зависимости от типа проверяемого объекта. Управление триггерами 19-24 и коммутатором 25 осуществляется сигналами пульта управления устройства (не показан), поступающими по входу 27, по которому также поступают сигналы п-разрядного кода.

Триггеры 19-22 синхронизируются сигналами синхронизатора 1, поступающими по

0 входу 26.

Блок 12 анализирует правильность функционирования системы: устройство-проверяемый объект. Подается тестовая информация из формирователя 3, блока 10 и считанная

из ОЗУ информация из блока 5 в блок 12, где осуществляется обработка при наличии управляющих сигналов, поступающих из блока 4 и блока 11. Сигналы результата обработки из блока 12 поступают в блок 4. При возникновении сбойной ситуации по анали0 ЗУ сигналов, поступающих в блок 4 из блока 10 и блока 12 определяется источник сбоя системы: устройство - проверяемый объект. Блок 12 (фиг. 1 и 3) работает следующим образом.

Диагностический контроль считанной ин5 формации, поступающей по входу 39 (фиг. 3 осуществляется с помощью схемы 29 сравнения и схемы 31 сравнения. Считанная информация поразрядно сравнивается схемой

29с информацией эталонной, поступающей р по входу 40. Диагностический контроль информации, поступающей на запись в ОЗУ, осуществляется с помощью схем сравнения

30и 32. Информация из блока 5 (фиг. 1) поступает на схемы 30 и 32 сравнения по щине входу 41 (фиг. 3) и поразрядно сравнивается с.эталонной. Таким образом, при наличии сбоев локализуется конкретно место неправильного функционирования ОЗУ или устройства. Результаты контроля через соответствующие коммутаторы 33-35 поступаQ ют на триггер 36.

Коммутаторы 33 и 34 обеспечивают коммутацию схем 29-32 в зависимости от типа тестовой информации. Регистрация диагностического контроля считанной и эталонной информации осуществляется триггером

5 36 (фиг. 3) сигнал сбоя с выхода которого поступает в блок 4 (фиг. 1). По входам 37 и 38 (фиг. 3) поступают сигналы управления от блока 4 и блока 11 (фиг. 3 и 1).

Кроме того, блок 12 (фиг. 1 и 3) используется для организации самоконтроля устройства перед началом проверки ОЗУ. Коммутатор 13 (фиг. 1) осуществляет коммутацию сигналов блока 5 для интерфейса ОЗУ или МП при воздействии управляющих сигналов из блока 4. Это позволяет оперативно переводить устройство на автономную проверку ОЗУ или произвольного МП.

Кроме того, коммутатор 13 осуществляет коммутацию выходных и входных каналов информации блока 5 при организации самоконтроля блока 5 или же всего устройства.

Технико-экономические преимущества предлагаемого устройства заключаются в его более высоких, по сравнению с прототипом, надежности и быстродействии.

Формула изобретения

1. Устройство для контроля блоков оперативной памяти, содержащее синхронизатор, регистр адреса, блок управления, блок приема и выдачи информации, блок обнаружения ошибок, индикатор и формирователь тестовых сигналов, первый и второй входы которого подключены соответственно к первым входам блока управления и регистра адреса, к выходу синхронизатора и выходу блока управления, входу синхронизатора, первым входам индикатора и блока обнаружения ошибок и второму входу регистра адреса, выход которого соединен с первым входом блока приема и выдачи информации, вторым входом индикатора и третьим входом формирователя тестовых сигналов, четвертый вход и выход которого подключены соответственно к вторым входам блока обнаружения ошибок и блока приема и выдачи информации и к третьим входам блока приема и выдачи информации и блока обнаружения ощибок, выход и четвертый вход которого соединены соответственно с вторым входом блока управления и третьим входом индикатора и с одним из выходов блока приема и выдачи информации, четвертый вход и другие выходы которого являются соответственно входом считывания, адресными и управляющими выходами и выходом записи устройства, отличающееся тем, что, с целью повышения надежности и быстродействия устройства, в него введены блок диагностики, первый коммутатор и многоканальный программируемый блок задания временной диаграммы, управляющие входы которого соединены с первыми входами коммутатог э и блока диагностики и выходом блок;; ynj ;вления, входы синхронизации - с походом синхронизатора, а выход - с ВТ ;)ыми входами блока обнаружения ошибок и блока диагностики, третий и четвертый входы которого подключены соответственно к выходу и к третьему входу блока обнаружения ошибок, выход и пятый вход

блока диагностики соединены соответственно с третьим входом блока управления и с одним из выходов блока приема и выдачи информации и вторым входом коммутатора, выход которого подключен к пятому входу блока приема и выдачи информации.

2.Устройство по п. 1, отличающееся тем, что многоканальный программируемый блок задания временной диаграммы содержит в каждом канале триггеры, второй коммутатор и схемы свертки по модулю два,

выходы которых подключены соответственно к входам запуска первого - четвертого триггеров, входы установки в «единицу пятого и шестого триггеров соединены соответственно с выходами первого и третьего

5 триггеров, а входы установки в «ноль пятого и шестого триггеров соответственно с выходами второго и четвертого триггеров, выходы пятого и шестого триггеров подключены к одним из входов второго коммутатора, выход которого является выходом блока, управляющими входами которого являются прямые и инверсные установочные входы первого-четвертого триггеров и одни из входов схем свертки по модулю два, другие входы которых, входы синхронизации триггеров и другие входы первого коммутатора являются входами синхронизации блока.

3.Устройство по п. 1, отличающееся тем, что блок диагностики содержит схемы сравнения, третий, четвертый и пятый коммутаторы и седьмой триггер, причем выходы первой и второй схем сравнения подключены к первым входам третьего и четвертого коммутаторов соответственно, выходы третьей и четвертой схем сравнения соединены соответственно с вторыми входами третьего и чет5 вертого коммутаторов, выходы которых подключены к первому и второму входам пятого коммутатора, выход которого соединен с входом запуска седьмого триггера, выходы которого являются выходами блока, третьи

0 и четвертые входы третьего-пятого коммутаторов и прямой и инверсный установочные входы седьмого триггера являются первым входом блока, вторым входом которого является управляющий вход седьмого триггера, одни из входов первой схемы сравнения и входы третьей схемы сравнения являются третьим входом блока, другие входы первой схемы сравнения и одни из входов второй схемы сравнения являются четвертым входом блока, пятым входом которого являются

0 другие входы второй и входы четвертой схем сравнения.

Источники информации, принятые во внимание при экспретизе

1.Патент США № 3751649, 5 кл. G 11 С 29/00, опублик. 1978.

2.Авторское свидетельство СССР

№ 611257, кл. G 11 С 29/00, 1978 (прототип).

гб

/7

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для сопряжения модулейВычиСлиТЕльНОй СиСТЕМы C KOHTPO-лЕМ | 1978 |

|

SU807258A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| Устройство для сопряжения ЭВМ с телеграфными аппаратами | 1984 |

|

SU1251092A1 |

15

fff

п

W

/

/J

0

гд

2f

/

//

fe./

J

39

29

J/

Jff

Авторы

Даты

1982-09-07—Публикация

1981-02-06—Подача