1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах с программные управле.нием.

Известно постоянное запоминвйэщее устройство трансформаторного типа, содержащее последовательно включенные числовые линейки, каждая числовая линейка прошита числовыми шинами и подключена к дешифратоРУ 1.1.

Недостатком этого устройства явлйется сложность гфошивки трансформаторов и заме-. ны числовых линеек.

. Наиболее близким по техническому решению к предлагаемому является устройство, содержащее накопитель, одни из выходов которого подключены к входаг усилителей считывания, а входы накопителя через ключи соеди}- ны с выходами основного дешифратора выборки, регистр и шины управления 2J.

При использовании таких постоянных запоминающих устройств (ПЗУ) количество усилителей, обмоток считыванг я, а также феррнтовых сердечников определяется количеством разрядов данного ПЗУ. Поэтому применение таких ПЗУ в устройствах для программного управления с большим количеством разрядов ограничено сложностью и громоздкостью их

Нбкепйтелей в конструктивном отношении (налпчне механических устройств, обеспечивающих крепление н надежное касание составных частей), а также сложностью в технологическом отношении (трудность прокладки и замены числовых линеек при установке в них нераэбооных сердечников). При этоМ в таких ПЗУ каждый разряд требует своего усилителя считывания, которые, как правило, являются многчжаскйдными к составляют знаJQ чительный удельный вес в электронном оборудовании ПЗУ.

. Таким образом, наряду со сложностью ПЗУ, большим габаритами накопителя усложняется его прошивка, а также конструктивное изготовление.

IS Цель изобретения - увеличение информационной емкобтн устройства.

Поставленная цель достигается тем, что.запоминающее устройство содержит дополнительный дешифратор выборки и элементы И-НЕ, первые входы которых соединены

0 с соответстаующими выходами дополинтельиого дешифратора выборки и с выходами усилителей считывания, вторые входы всех элементов И-НЕ подключены к соответствующим шина. управления, выходы одних из элёмент в И-НЕ под.спючены к регистру, выходы

элементов И-НЕ , соединены с соответствующими входами накопителя.

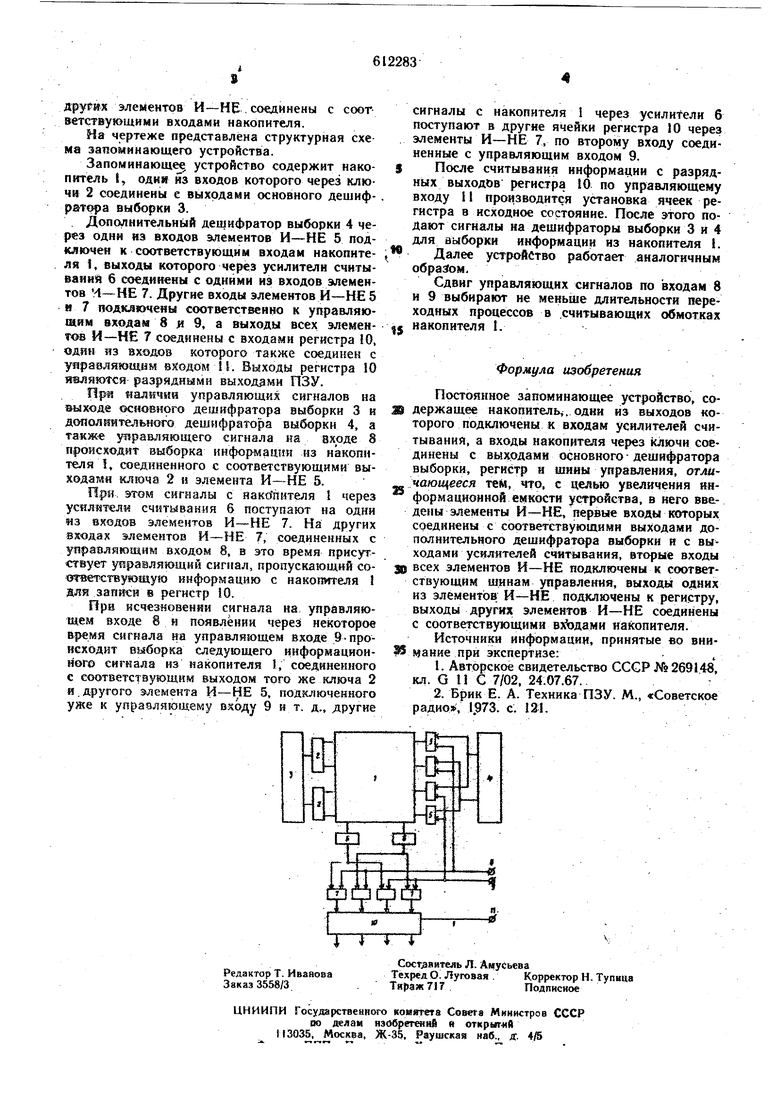

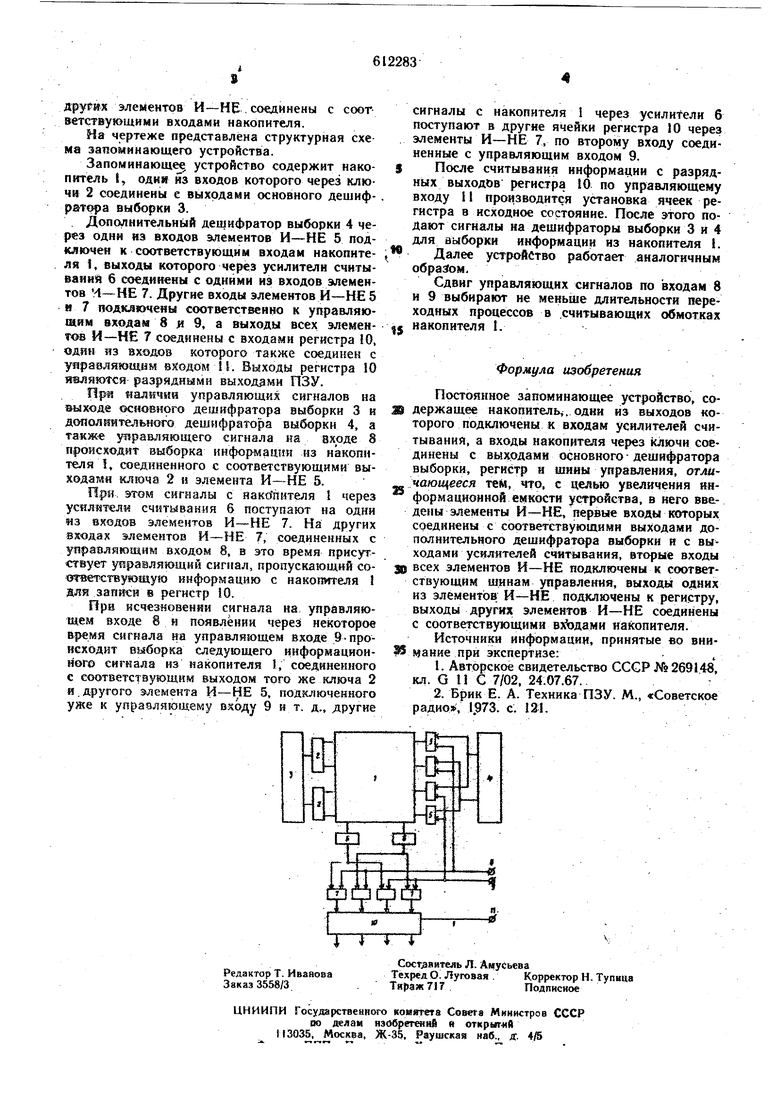

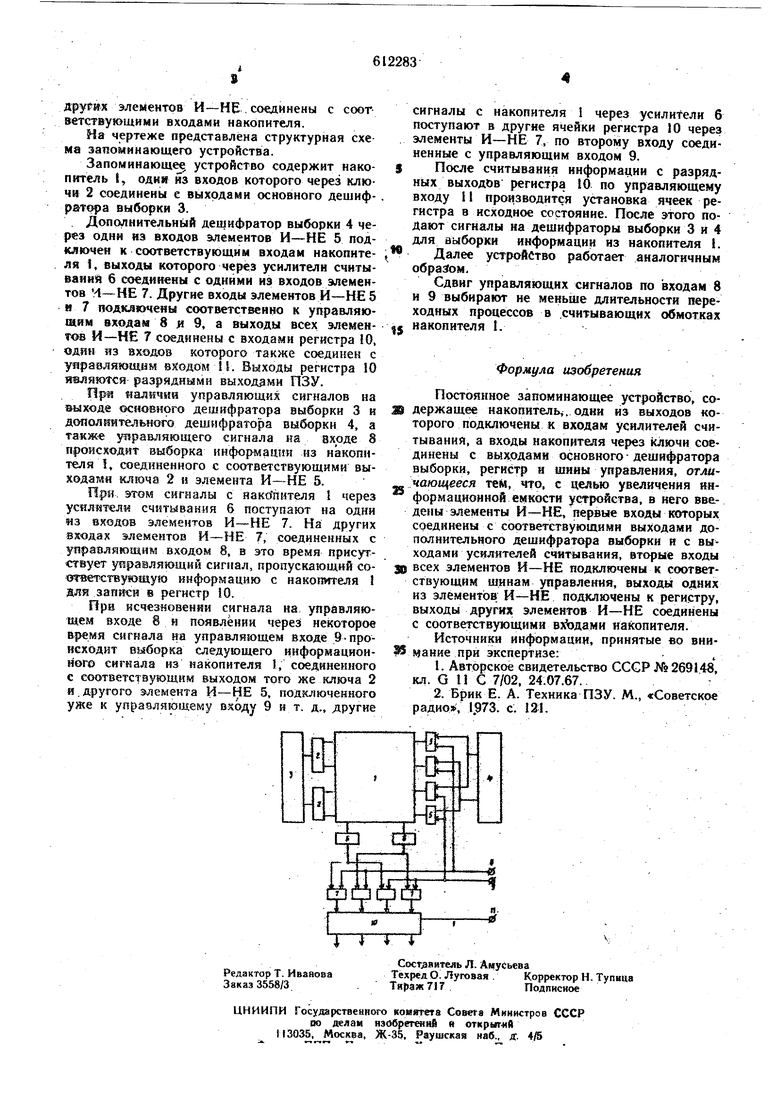

На чертеже представлена структурная схема запоминающего устройства.

Запоминающе устройство содержит накопитель I, ОДНИ из входов которого через ключи 2 соединены е выходами основного дешиф- . р&тора выборки 3.

Дополнительный дешифратор выборки 4 через одни нз входов элемеитов И-НЕ 5 подключен к соответствующим входам накопителя I, выходы которого через усилители считываинй 6 соединены с одними из входов элементов Л-НЕ 7. Другие входы элементов И-НЕ 5 и 7 подключены соответственно к управляющим входам 8 я 9, а выходы всех элементе® И-НЕ 7 соединены с входами регистра 0, ОДИН из входов которого также соединен с уяравлйкнднм входом 11. Выходы регнстра 10 яшляютсй разрядными выходами ПЗУ.

Оря иалнчий управляющих сигналов на выходе основного дешифратора выборки 3 и дояолйительного дешифратора выборки 4, а также управляющего сигнала на входе 8 происходит выборка информации из накопителя , соединенного с соответствующими выходамн ключа 2 и элемента И-НЕ 5.

. этом сигналы с накопителя 1 через усилители считывания 6 поступают на одни из входов элементов И-НЕ 7. На других входах элементов И-НЕ 7, соединенных с управляющим входом 8, в это время присутствует управляющий сигнал, пропускающий со0таетсгвующую информацию с накопителя I жля записи в регистр 0.

При исчезновении сигнала на управляющем входе 8 и появлении через некоторое время сигнала на управляющем входе 9-происходит выборка следующего информационного сигнала из накопителя 1, соединенного с соответствующим выходом того же ключа 2 «.другого элемента И-НЕ 5, подключенного уже к управляющему входу 9 и т, д., другие

сигналы с накопителя 1 через усилители 6 поступают в другие ячейки регистра 0 через элементы И-НЕ 7, по второму входу соединенные с управляющим входом 9.

После считывания информации с разрядных выходов регистра 10 по управляющему входу 11 производится установка ячеек регистра в исходное состояние. После этого подают сигналы на дешифраторы выборки 3 и 4 для выборки информации из накопителя .

Далее устройство работает аналогичным образом.

Сдвиг управляющих сигналов по входам 8 и 9 выбирают не Meifbuie длительности переходных процессов в .считывающих обмотках накопителя 1.

Формула изобретения

Постоянное запоминающее устройство, содержащее накопитель, одни из выходов которого подключены к входам усилителей считывания, а входы накопителя через ключи соединены с выходами основного дещифратора выборки, регистр н шины управления, отличающееся тем, что, с целью увеличения информационной емкости устройства, в него введены элементы И-НЕ, первые входы которых соедииены с соответствующими выходами дополнительного дещифратора выборки и с выходами усилителей считывания, вторые входы всех элементов И-НЕ подключены к соответствующим шинам управления, выходы одних из элементов И-НЕ подключены к регистру, выходы других элементов И-НЕ соединены с соответствующими взсЬдами накопителя.

Источники информации, принятые во вииц}ание при экспертизе:

1.Авторское свидетельство СССР № 269148, кл. G П С 7/02, 24.07.67.

2.Брик Е. А. Техника ПЗУ. М., «Советское радио, 1.973. с. 121.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1978 |

|

SU750562A1 |

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ из постоянного ТРАНСФОРМАТОРНОГО ЗАПОМИНАЮЩЕГО | 1973 |

|

SU377868A1 |

| Модуль постоянной памяти | 1979 |

|

SU905858A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU744730A1 |

| Трансформаторное постоянное запо-МиНАющЕЕ уСТРОйСТВО | 1979 |

|

SU841048A1 |

| Запоминающее устройство | 1983 |

|

SU1112412A1 |

| Трансформаторное постоянное запоминающее устройство | 1985 |

|

SU1310901A2 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Запоминающее устройство | 1980 |

|

SU940235A1 |

| Трансформаторное постоянное запоминающее устройство | 1982 |

|

SU1072097A1 |

Авторы

Даты

1978-06-25—Публикация

1976-08-02—Подача