Изобретение относится к вычислительной технике и может быть использовано при изготовлении больших интегральных схем запоминающих устройств с произвольной выборкой информации, имеющих большую площадь кристаллов, где требуется увеличить выход правильно функционирующих изделий с высоким быстродействием.

Известно запоминающее устройство, содержащее матрицуэлементов памяти (ЭП), схемы логики обрамления и схемы коррекции, позволяющие исправлять ошибки, вызванные дефектами ЭП, которые расположены в нескольких разрядах матрицы ЭП при наличии такого же числа дополнительных разрядов в матрице (I.

Недостатком этого устройства является низкое быстродействие.

Наиболее близким техническим рещением к изобретению является запоминающее устройство, содержащее дешифратор адреса слова, соединенный с числовыми адресными щинами матрицы основных и резервных ЭП разрядные шины которых соединены соответственно с основными и резервными усилителями записи считывания (УЗС), первые управляющие входы которых связаны с выходом схемы управления записью считыванием, входами подключенной к шинам выборки кристалла, разрешения записи и входной информации, входы дешифратора адреса разряда соединены с первыми входами матрицы программируемых элементов И, и выходами буферных схем, выходы которых соединены с вторыми входами матрицы программируемых алементов И, третьи входы которой под ключаются к управляющим входам програМ мирования, информационный выход основных и резервных УЗС соединен с входом выходного блока, управляющие входы к.оторого подключены к шинам выборки кристалла и разрешения записи, выход выходного блока является выходом устройства {2J.

Недостатками известного устройства являются низкое быстродействие из-за задержек сигналов коррекции в целях запрета обращения к дефектному ЭП основной матрицы, а также сложность устройства.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее дешифратор адреса слова, выходы которого соединены с числовыми щинами матрицы ос(ювных и резервных ЭП, разрядные шины которвй подключены к одним из входов основных и резервных усилителей соответственно, одни из управляющих входов которых соединены с выходом формирователя управляющих сигналов, а выходы подключены к входам выходного блока, матрицу программируемых ЭП, один из входов которой соединены с выходами регистра адреса разряда и входами дещифратора адреса разряда, а другие входы объединены с входами

регистра адреса разряда и являются одними из адресных входов устройства, информационными входами которого являются одни из входов формирователя управляющих сигналов, другие входы которого и управляющие входы выходного блока являются одними из управляющих входов устройства, другими управляющими входами которого являются управляющие входы матрицы программируемых ЭП выходом устройства -

О выход выходного блока., введены источник опорного напряжения и- две группы -формирователей сигналов, причем входы одних из формирователей сигналов подключены к выходам дешифратора адреса разряда, и выходы - к другим управляющим входам основных усилителей, входы других формирователей сигналов соединены с выходами матрицы программируемых ЭП, а выходы - с другими управляющими входами резервных усилителей, выходы источника опор0 ного напряжения подключены к другим входам основных и резервных усилителей.

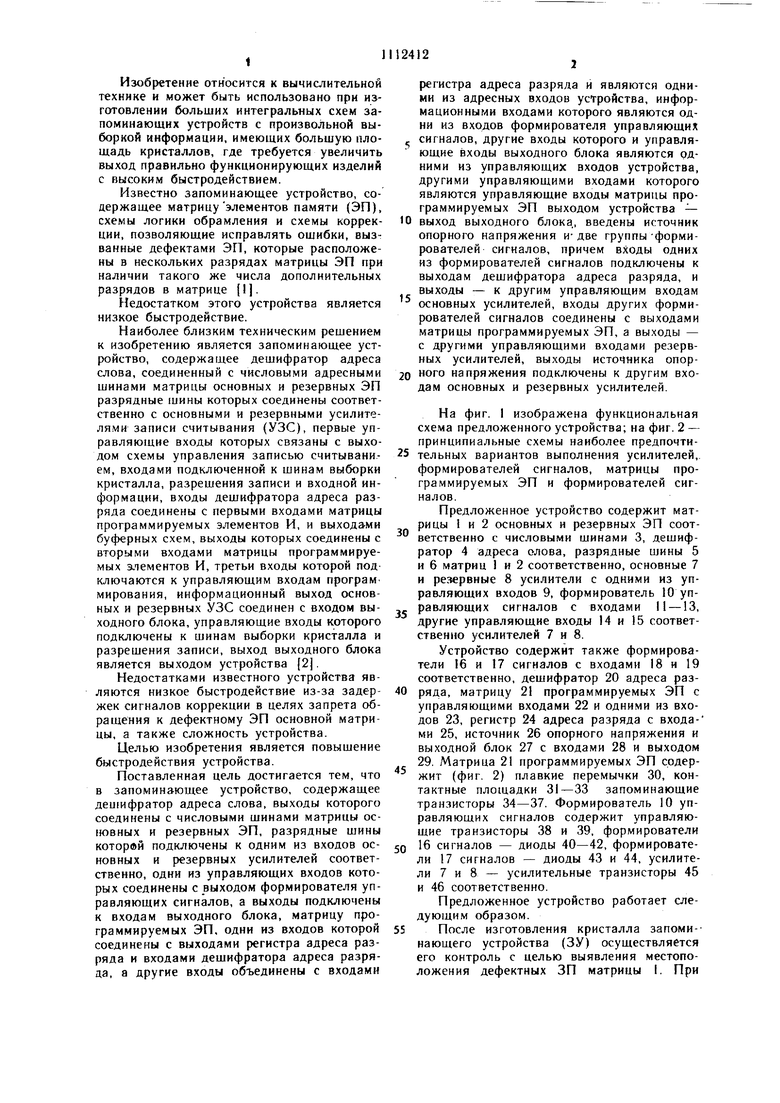

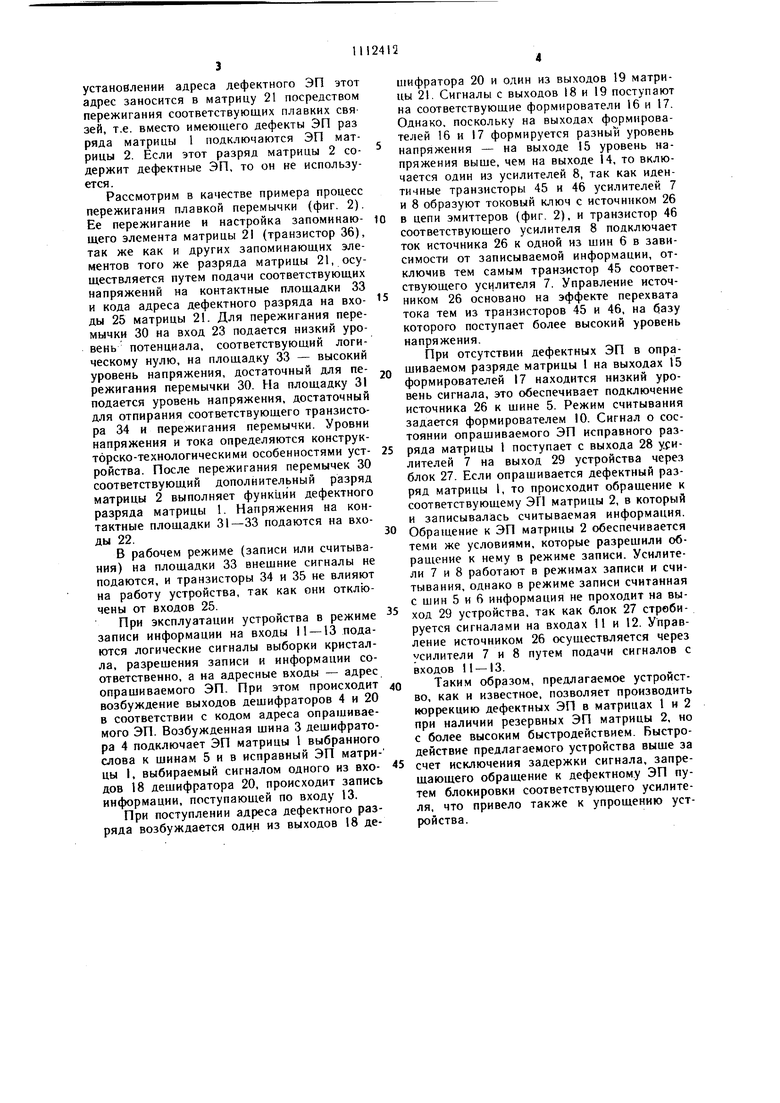

На фиг. I изображена функциональная схема предложенного устройства; на фиг. 2 - принципиальные схемы наиболее предпочти5 тельных вариантов выполнения усилителей, формирователей сигналов, матрицы программируемых ЭП и формирователей сигналов.

Предложенное устройство содержит матрицы 1 и 2 основных и резервных ЭП соот0ветственно с числовыми шинами 3, дешифратор 4 адреса олова, разрядные шины 5 и 6 матриц 1 и 2 соответственно, основные 7 и резервные 8 усилители с одними из управляющих входов 9, формирователь 10 управляющих сигналов с входами 11 - 13, другие управляющие входы 14 и 15 соответственно усилителей 7 и 8.

Устройство содержит также формирователи 16 и 17 сигналов с входами 18 и 19 соответственно, дешифратор 20 адреса раз0 ряда, матрицу 21 программируемых ЭП с управляющими входами 22 и одними из входов 23, регистр 24 адреса разряда с входами 25, источник 26 опорного напряжения и выходной блок 27 с входами 28 и выходом 29. Матрица 21 программируемых ЭП содержит (фиг. 2) плавкие перемычки 30, контактные площадки 31-33 запоминающие транзисторы 34-37. Формирователь 10 управляющих сигналов содержит управляющие транзисторы 38 и 39, формирователи

16 сигналов - диоды 40-42, формирователи 17 сигналов - диоды 43 и 44, усилители 7 и 8 - усилительные транзисторы 45 и 46 соответственно.

Предложенное устройство работает следующим образом.

5 После изготовления кристалла запоми-нающего устройства (ЗУ) осуществляется его контроль с целью выявления местоположения дефектных ЗП матрицы I. При

установлении адреса дефектного ЭП этот адрес заносится в матрицу 21 посредством пережигания соответствующих плавких связей, т.е. вместо имеющего дефекты ЭП раз ряда матрицы 1 подключаются ЭП матрицы 2. Если этот разряд матрицы 2 содержит дефектные ЭП, то он не используется.

Рассмотрим в качестве примера процесс пережигания плавкой перемычки (фиг. 2). Ее пережигание и настройка запоминающего элемента матрицы 21 (транзистор 36), так же как и других запоминающих элементов того же разряда матрицы 21, осуществляется путем подачи соответствующих напряжений на контактные площадки 33 и кода адреса дефектного разряда на входы 25 матрицы 21. Для пережигания перемычки 30 на вход 23 подается низкий уровень потенциала, соответствующий логическому нулю, на площадку 33 - высокий уровень напряжения, достаточный для пережигания перемычки 30. На площадку 31 подается уровень напряжения, достаточный для отпирания соответствующего транзистора 34 и пережигания перемычки. Уровни напряжения и тока определяются конструкторско-технологическими особенностями устройства. После пережигания перемычек 30 соответствующий дополнительный разряд матрицы 2 выполняет функции дефектного разряда матрицы 1. Напряжения на контактные площадки 31-33 подаются на входы 22.

В рабочем режиме (записи или считывания) на площадки 33 внещние сигналы не подаются, и транзисторы 34 и 35 не влияют на работу устройства, так как они отключены от входов 25.

При эксплуатации устройства в режиме записи информации на входы 11 -13 подаются логические сигналы выборки кристалла, разрещения записи и информации соответственно, а на адресные входы - адрес опращиваемого ЭП. При этом происходит возбуждение выходов дещифраторов 4 и 20 в соответствии с кодом адреса опращиваемого ЭП. Возбужденная щина 3 дещифратора 4 подключает ЭП матрицы 1 выбранного слова к щинам 5 и в исправный ЭП матрицы I, выбираемый сигналом одного из входов 18 дещифратора 20, происходит запись информации, поступающей по входу 13.

При поступлении адреса дефектного разряда возбуждается один из выходов 18 дешифратора 20 и один из выходов 19 матрицы 21. Сигналы с выходов 18 и 19 поступают на соответствующие формирователи 16 и 17. Однако, поскольку на выходах формирователей 16 и 17 формируется разный уровень напряжения - на выходе 15 уровень напряжения выще, чем на выходе 14, то включается один из усилителей 8, так как идентичные транзисторы 45 и 46 усилителей 7 и 8 образуют токовый ключ с источником 26 в цепи эмиттеров (фиг. 2), и транзистор 46 соответствующего усилителя 8 подключает ток источника 26 к одной из шин 6 в зависимости от записываемой информации, отключив тем самым транз-истор 45 соответствующего усилителя 7. Управление источником 26 основано на эффекте перехвата тока тем из транзисторов 45 и 46, на базу которого поступает более высокий уровень напряжения.

При отсутствии дефектных ЭП в опрашиваемом разряде матрицы 1 на выходах 15 формирователей 17 находится низкий уровень сигнала, это обеспечивает подключение источника 26 к щине 5. Режим считывания задается формирователем 10. Сигнал о состоянии опрашиваемого ЭП исправного разряда матрицы 1 поступает с выхода 28 усилителей 7 на выход 29 устройства через блок 27. Если опрашивается дефектный разряд матрицы I, то происходит обращение к соответствующему ЭП матрицы 2, в который и записывалась считываемая информация. Обращение к ЭП матрицы 2 обеспечивается теми же условиями, которые разрешили обращение к нему в режиме записи. Усилители 7 и 8 работают в режимах записи и считывания, однако в режиме записи считанная с шин 5 и 6 информация не проходит на выход 29 устройства, так как блок 27 стребируется сигналами на входах И и 12. Управление источником 26 осуществляется через усилители 7 и 8 путем подачи сигналов с входов И -13.

Таким образом, предлагаемое устройство, как и известное, позволяет производить 1юррекцию дефектных ЭП в матрицах 1 и 2 при наличии резервных ЭП матрицы 2, но с более высоким быстродействием. Быстродействие предлагаемого устройства выще за счет исключеиия задержки сигнала, запрещающего обращение к дефектному ЭП путем блокировки соответствующего усилителя, что привело также к упрощению устройства.

29

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Запоминающее устройство | 1983 |

|

SU1107176A1 |

| Запоминающее устройство с коррекцией дефектных элементов памяти | 1981 |

|

SU980165A1 |

| Программатор для записи информации в полупроводниковые элементы памяти | 1985 |

|

SU1280449A2 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Адресный формирователь | 1988 |

|

SU1596388A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1418816A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее дешифратор адреса слова, выходы которого соединены с числовыми шинами матрицы основных и резервных элементов памяти, разрядные шины которой подключены к одним из входов основных и резервных усилителей соответственно, одни из управляюших входов которых соединены с выходом формирователя управляющих сигналов, а выходы подключены к входам выходного блока, матрицу программируемых элементов памяти, одни из входов которой соединены с выходами регистра адреса разряда и входами деижфратора адреса разряда, а другие входы объединены с входами регистра адреса разряда и являются одними из адресных входов устройства, информационными входами которого являются одни из входов формирователя управляющих сигналов, другие входы которого и управляющие входы выходного блока являются одними из управляющих входов устройства, другими управляющими входами которого являются управляющие входы матрицы программируемых элементов памяти, выходом устройства является выход выходного блока, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены источник опорного напряжения, и две группы формирователей сигналов, причем входы одних из формирователей сигнаi лов подключены к выходам дешифратора адреса разряда, а выходы - к другим управ(Л ляющим входам основных усилителей, входы других формирователей сигналов соединены, с выходами матрицы программируемых элемеитов памяти, а выходы - с другими управляющими входами резервных усилителей, выходы источника опорного напряжения подключены к другим входам основных и резервных усилителей. to ;ib

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с коррекцией дефектных элементов памяти | 1981 |

|

SU980165A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-09-07—Публикация

1983-06-02—Подача