(54) МОДУЛЬ ПОСТОЯННОЙ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Устройство для вывода информации | 1983 |

|

SU1124278A1 |

| ТРЕНАЖЕР ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ МАТРИЦ | 1990 |

|

RU2102792C1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Устройство для обмена информацией | 1979 |

|

SU849193A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для отображения информации на матричном индикаторе | 1990 |

|

SU1835555A1 |

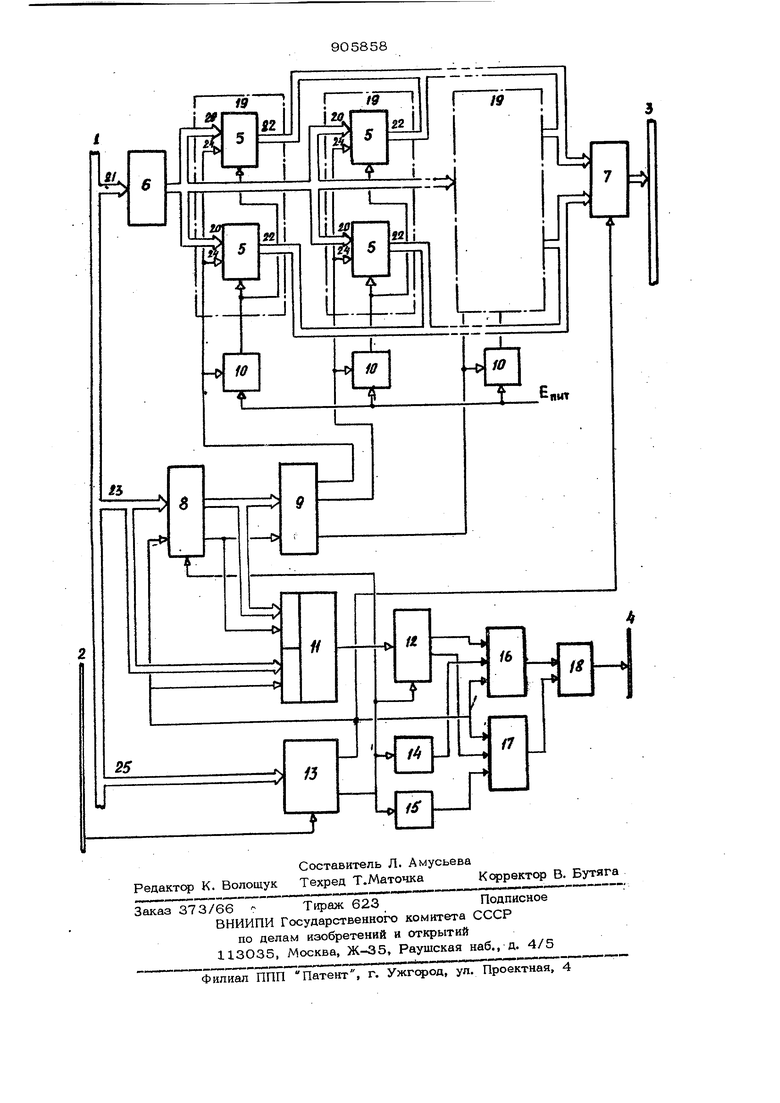

Изобретение относится к вычислитель ной технике, в частности к постоянным запоминающим устройствам вычислительных машин. Известно постоянное запоминающее устройство, выполненное на полупроводниковых мйтриц памяти и содержащее большое количество полупроводниковых матриц памяти, необходимых для организации требуемой емкости устройства, адресные и числовые усилители, дещифраторы выборки матриц памяти и схемы управления. Адресные входы матриц памяти адресные усилители ПОДКЛЕОчены к адресным шинам, числовые выходы через числовые усилители - к числовым шинам ЦВМ. Входы выборки матриц подключены к выходам дешифраторов, под ключенных входами к адресным шинам, а входы питающего напряжения всех мат риц соединены непосредственно с источником питания l3 . Недостатком устройства является бол шое потребление энергии матрицами памяти и сложность построения систем памяти большой емкости из отдельных модулей памяти. Наиболее близким к предложенному по , технической сушности и схемному решению является модуль постоянной памяти, содержащий 16 полупроводниковых матриц памяти, входы питающего напряжения которых соединены непосредственно с источником питания, адресные усилители, числовые усилители, дешифратор выбора матриц и селектор с коммутационным полем, осуществляющие блокировку отдельных К1атриц памяти модуля. В это к- модуле адресные шины первой группы подключены к входам адресных усилителей, выходы которых подключены к aдpecньt : входам матриц памяти, выходы матрим соединены с входами числовых усилителей, выходы которых подключены к числовым шннам ЦВМ. Адресные шины второй группы подключены к входам дешифраторов, обеспечиваюших выбор одной матрицы из 16, и к управляющим входам селек39Отора, селектируемые входы котсфого соединены с контактами коммутационного по ля. Управляющие входы дешнфратс а и числовых усилителей поаключены к шине сопровождения адреса ЦВЛ1. Адресные шины третьей группы соединены с элементами схемы у1фавления 2. Недостатком данного модуля является большое потребление энергии матрицами памяти, что приводит к увеличению габаритов и веса блока питания и ЦВ/И в целом, усложнению конструкции из-за необходимости отвода избыточного тепла и снижению надежности. Указанные недостатки ограничивают область примене- ния полупроводниковых постоянных ЗУ .ujofl емкости и практически исключаю возможность их использования в составе бортовых ЦВМ. Цель изобретения - уменьшение потре ляемой мощности и повышение надежности ЗУ. Поставленная цель достигается тем, что в модуль постоянной памяти, содержащий группы матричных полупроводниковых накопителей, адресные входы котфых подключены к соответствующим выходам адресных, усилителей, входы котярых подключены к ащ}есным шинам первой группы, выховы матричных накопителей соединены с входами числовых усилителей, уг равлающие входы матричных накопителей групп соединены с выходами де- шифрат а, и шины синхронизации, в него введены блок сравнения, триггер, одновибраторы, элементы И, элемент ИЛИ, 1рограмм1фуемый накопитель, регистр и I коммутаторы, одни входы которых подсое динены к у1фавляюшим входам матричных накопителей, другие - к шинам питания, а выходы к входам питания матричных накопителей, адресные и угфавляюший входы дешифратора н одни из входов элемента сравнения соединены с выходами регистра, щ)угие входы элемента срав нения и сйин из входов регистра подключены соответственно к адресным шинам второй группы н к первому выходу программируемого накопителя, первому вход триггера и входам одновибраторов, второй выход программируемого накопителя соединен с управляющими входами числовых, усилителей, адресные входы регистра соединены с первыми входами элементов И, вторые входы которых подключены к инверсным выходам одновибраторов, третьи входы элементов И соединены с прямым и инверсным выходами тригтера, а выходы - с входами элемента ИЛИ, выход которого соединен с шиной синхронизации адреса, входы программируемого накопителя подключены к адресным шинам третьей группы и к шине синхронизации числа, выход элемента сравнения соединен с вторым входом триггера. На чертеже гфедставлена структурная схема модуля постоянной памяти. Модуль своими входами подключен к адресным шинам 1 и к шине 2 синхронизации адреса ЦВМ, а выходами - к числовым шинам 3 и шнне 4 синхронизации числа. Наличие сигналов на шинах 2 и 4 синхронизации адреса и числа свидетельствует об окончании переходных процессов на шинах 1 и 3 адреса и числа. Схемы угфавления устройства, подкпюченных к адресным и числовым шинам, могут использовать коды, установленные на этих шинах, только наличии сигналов на соответствующих шинах 2 и 4. Модуль содержит полупроводниковые матрицы 5 памяти, адресные усилители 6, числовые усилители 7, регистр 8, дешифратор 9, коммутат ч ы питания Ю, схему сравнения 11, триггер 12, программируемый накопитель 13, два одноBHdpaTqpa 14 и 15, два элемента И 16 и 17 и элемент ИЛИ 18. Матрицы памяти объединены в группы 19. Количество матриц 5 в группе 19 и количество групп 19 и модуле определяется внутренней организацией матриц и сргавизацией модуля памяти. Нащжмер, при сдэганизации матрицы 512 8-разрядных чисел и требуемой емкости модуля 16К 16-ра; ядных чисел модуль должен 32 группы по 2 матрицы в каждой. Одноимеиные адресные входы 20 всех матриц 5 подключены через адресные усилители 6 к первой группе 21 адресных шин 1, значение кода на которых О1феделяет адрес числа внутри матрицы 5. Одноименные числовые выходы 22 матриц 5 подключены через числовые усилители 7 к числовым шинам 3 ЦВМ. Адресные и числовые усилители обеспечивают минимальную ц грузку на шины ЦВМ и позволяют одновременно подключать к шинам несколько модулей памяти. Регистр 8 состоит из группы адресных и одного у1Чзавляющего разрядов и предназначен для хранения текущего значения кода адреса, установленного на второй группе 23 адресных шин, и текущего значения сигнала обращения к модулю. формируемого на первом выходе программируемого накопителя 13. Ввод информации в регистр осуществляется сигналом обращения к ПЗУ, который формируется на ьгором выходе схемы 13 и поступает на синхровход регистра 8. Выходы адресных и угфавляющего регистра 8 подключены соответственно к адресным и управляющему входам деши(}ратора 9. При этом работа дещи4ратс а 9 раарешена в том случае, если на выходе управ ляющего разряда регистра - сигнал логичес кой единицы. В зaвнcи ocтн от значения ко да на адресных входах 9 обеспечивает выбор одной из групп 19 матриц по управляющим входам 24 и включение соответствующего коммутатора 10 питания, который подключает матрицы выбранной группы к источнику питающего напряжения. Схема сравнения 11 предназначена для пс а ядного сравнения кода, записанного в регистр 8 во время предыдущего обращения к ПЗУ, с текущим зиа чением этого же кода. Результат сравнения вводится в триггер 12 одновремеН но с вводом текущего значения кода в регистр 8. Если сравнение произощло и в триггер 12 записана логическая единица, то при текущем обращении выбор числа произво«1ится на той же группы 5 того же модуля, что н при 1Ч)едыдущем обращении. В этом случае не происходит переключение питающего нащ)5окения с матриц naMSTTR одной группы на Щ1у- гой Группы, а время выборки информации из модуля равно времени выбсфки матриц 5 памяти. Есяя сравнение не произошло и в тригг 12 запвсан логический ноль, то при данном обрашенви к ПЗУ щюисходит переключение питающего напряжения, с матриц одной группы на матрицы другой группы, ном которой вводится в адресные регистра 8, данного модуля или на матрицы одной из групп другого модуля, входящего в состав ПЗУ. В этом случае время выборки инфс мации равно сумме времени выборки матриц памяти и времени переключения коммутатора ip питания. Одновнбраторы 14 и 15 запускаются сигналом обращения и ПЗУ, который фор мируется на втором входе накопителя 13 и обеспечивают задержку сигнала сиюдронизации числа, который формируется эле ментами И и ИЛИ 16-18 и гюступает на шину 4 синхронизации числа. В зависимости от состояния триггера 12 включается один из элементов И 16 и 17 и через элемент 18 ИЛИ проходит сигнал от соответствующего одновибратора 14 или 15. Первый одновибратор 14 формирует импульс, длительность котсрого равна времени выборки матриц 5 памяти, длительность импульса второго одновибратора 15 равна сумме времени выборки матриц 5 памяти и времени переключения коммутатора 1О питания. Таким образом, задержка сигнала синхронизации числа относительно сигнала синхронизации адреса соответствует времени появления на щинах 3 числа достоверной информации, т.е. времени выбелки модуля. Накопитель 13, входы которого подключены к третьей группе 25 адресных щин и к щине 2 согфовождения адреса, вырабатывает совокупность двух сигналов: сигнал обращения к модулю (первый выход) и сигнал обращения к ПЗУ, т.е. к любому модулю, входящему в ПЗУ (второй выход). Сигнал обращения к модулю вьфабатывается в случае, если установленный на третьей группе 2 адресных шин адрес 1финадлежит массиву адресов данного модуля, и инициирует включение коммутатсфов и числовых усилителей. Сигнал офащения к ПЗУ формируется, если текущий ащзес гфинадлежш- одному из модулей (любому ПЗУ) и инициирует переключение питания от одного модуля к другому. Накопитель 13 может быть построен с использованием полупроводниковой матрицы ПЗУ небольшой емкости (количество чисел равно количеству модулей всех типов в ЦВМ, разрядность 2, запрограммированной в соответствие с распределением адресов ЦВМ. Такое построение модулей полупроводниковой памяти позволяет многократно уменьшить ток, потребляемый матрицами памяти и стабилизировать его, так как постоянно подключены к источнику питания матрицы только одной группы одного из модулей, входящих в ПЗУ, уменьшить габариты и вес ЦВМ, упростить ее конструкцию и повысить надежность. Например, при построении ПЗУ емкостью 64К 16-разрядных чисел на матрицах памяти, имеющих организацию 512 8-разрядных чисел, общая мощность, рассеиваемая матрицами памяти устройства, выполнен.кого по известной схеме, составляет около 2ОО Вт, (щ)Я мощности, рассеиваемой одной матрицей памяти 0,83 т). В предг ложенной конструкции эта мощность уменьшена до 1,6 Вт. При этом быстродействие 13У практически не ухудшается, так как гфограммным путем обеспечивается длительный период обращений к одной групп одного из модулей (т.е. без переключени питания между группами) с редкими пере ходами от одной группы к другой и от одного моду.г1я к другому. Формула изобретения Модуль постоянной памяти, содержащий группы матричных полухфоводниковых накопителей, адресные входы которых подключены к соответствующим выходам адресных усилителей, входы которых подключены к адресным шинам перво группы, выходы матричН1.х накопителей соединены с входами числовых усилителей, управляющие входы матричных накопителей групп соединены с выходами дешифратора, и шины синхронизации, отличающийся тем, что, с целью уменьшения пагребляемой мощности и повышения надежности, в него введены блок сравнения, триггер, одновибраторы, элементы И, элемент ИЛИ, программируемый накопитель, регистр н коммутаторы одни входы которых подключены к управляющим входам матричных накопителей, а другие - к шинам питания, а выходы к входам питания матричных накопителей, адресные и управляющий входы дешифратора и один из входов элемента сравнения соединены с выходами регистра, другие входы элемента сравнения и один из входов регистра подключены соответственно к адресным шинам второй группы и к первому выходу программируемого ндкопителя, первому входу триггера и входам одновибраторов, второй выход хфограммируемого накопителя соединен с управляющим входом числовых усилителей, адресные входы регистра соединены с первыми входами элементов И, вторые входы которых подключены к инверсным выходам одновибраторов, третьи входы элементов И соединены с прямым и инверсным выходами триггера, а выходы с входами элемента ИЛИ, выход которого соединен с щиной синхронизации адреса, Входы программируемого накопителя подключены к адресным щинам третьей группы и к шине синхронизации числа, выход элемента сравнения соединен с вторым входом триггера. Источники информации, 1ринятые во внимание при экспертизе 1.Патент США N9 3858187, кл. 340-172. 5, опублик 1974. 2.ineiviovy desigu handlfioob Изд. фирмы Jhtef , с. 8-42, фиг. 66 (прототип).

Авторы

Даты

1982-02-15—Публикация

1979-02-08—Подача