(54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗСВАНИЯ ДВОИЧНОГО КОДА В ИМПУЛЬСНУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1989 |

|

SU1633492A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Цифровой фазометр-частотомер | 1985 |

|

SU1265644A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1451861A1 |

| СПОСОБ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА НА ВРАЩАЮЩЕЙСЯ ПО УГЛУ КРЕНА РАКЕТЕ. ЛИНЕАРИЗАТОР СИГНАЛА. ПЕРЕКЛЮЧАЕМЫЙ ЛИНЕАРИЗАТОР СИГНАЛА. СПОСОБ ИНТЕГРИРОВАНИЯ ДЛЯ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА И ЦИФРОВОЙ ИНТЕГРАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2549231C1 |

| Устройство для генерирования функционально изменяющихся напряжений | 1979 |

|

SU903916A1 |

| Аналого-цифровой преобразователь | 1991 |

|

SU1800617A1 |

| Устройство для измерения временных интервалов | 1985 |

|

SU1293692A1 |

| Устройство для отображения информации | 1972 |

|

SU458004A1 |

Иаобретенае относится к области автоматики и вычиспительвой техники и может быть испоиьаовано для , матеилатичвского преобраз жания частотно-импульсной информации.

Известные устройства преобразования двоичного кода в импульсную последовательность сложны по своей схемной реализации ij,

Наиболее близким по технической сущнести к предложенному является устройство пре разования двоичного кода в импульсную последовательность, содержащее формирователь импульсов, BXOJ3 которого соединен с выходом генераipopa опорной частоты, а выходы - со входами триггера, выход которого соединен с первым управляющим входом ключа, второй управлягощ{й вход которого подклв чен к шине окончания преобразования, пер- вый и второй сумматоры, выход каждого из которых подключен ко входу соответствующего регистра двоичного кода, выход которого соединен с первым входом соответствующего сумматора.

Такое устройство- требует формирования взвешенных по двоичному ввкову серий опорных импульсов, что создает аппаратурную сложность.

Цепь изобретения - уйрошение устройства - достигается тем, что в нем выход первого регистра двоичного кода через ключ соединен со вторым входом второго сумматора, выход которого является выходом устройства.

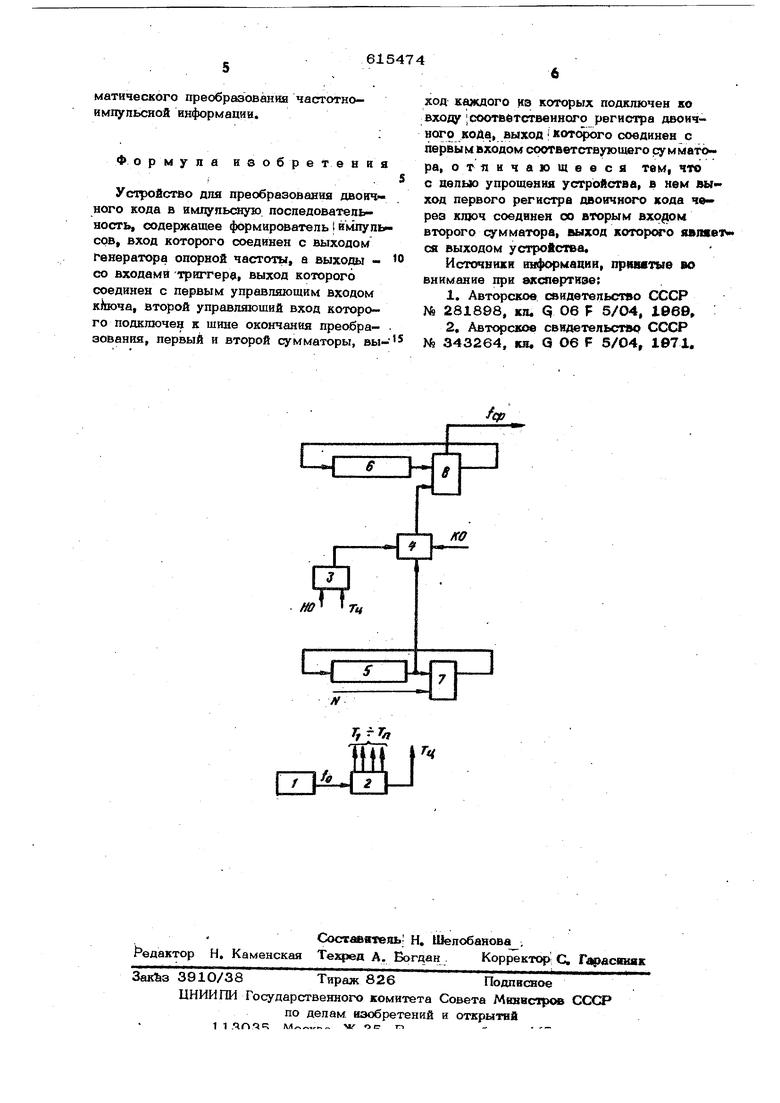

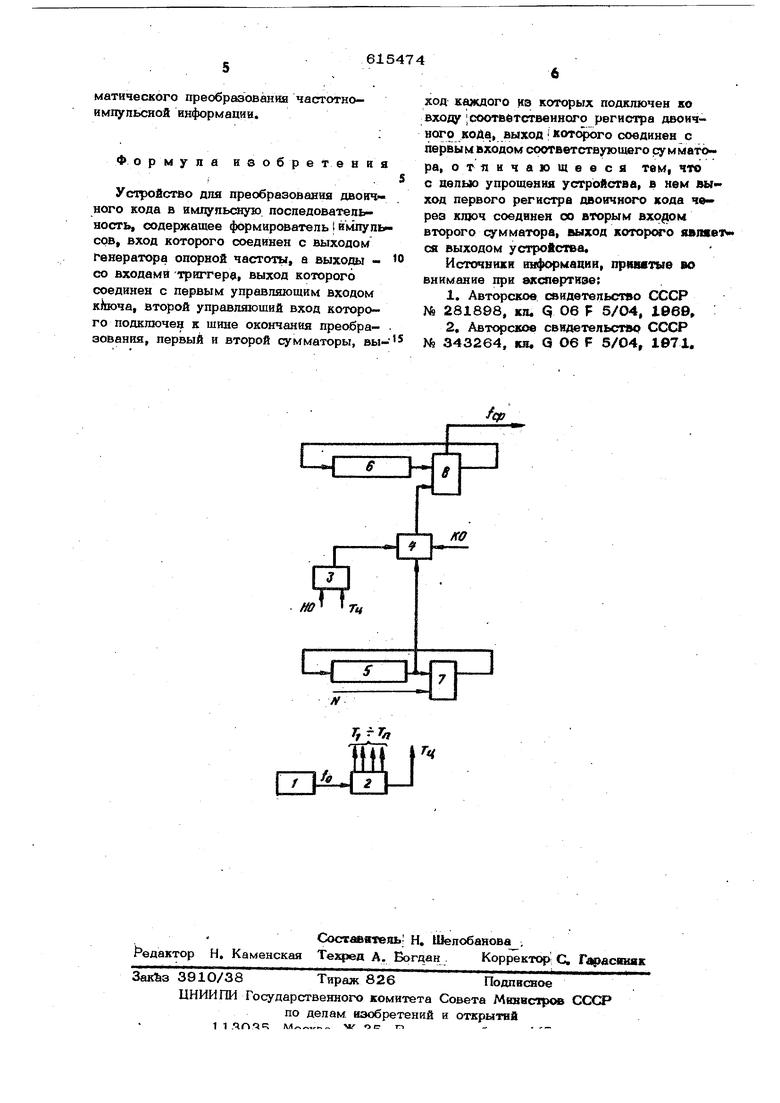

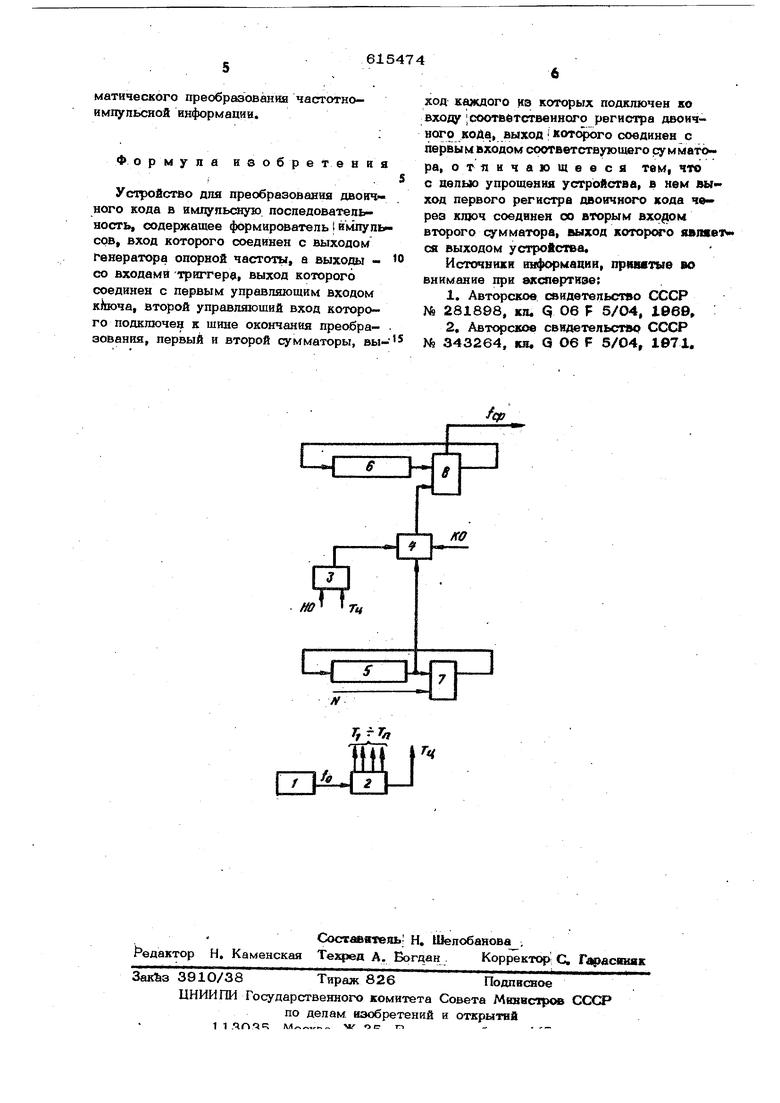

На чертеже представлена блок-схема устройства преобразование двоичного кода в импульсную последовательность, содержащая генератор 1 опорной частоты, формирователь 2 импульсов, триггер 3, ключ 4, первый и второй регистры 5, 6 ДВОИЧНО1Х) кода, первый и второй сумматоры 7 8,

Функционально первый регистр 5 дво1г Ного кода и первый сумматор 7 так же, как второй регистр 6 двоичного кода со вторым сумматором 8, объединены соответственно в интегратор текущего значения и функциональный интегратор. Если за время преобразования произ ведено П суммирования двоичного кода К , то выражение для результата вы числений может быть записано в следую щем gfj П.К„.и„-2 ,,CD где Я f, - ЧИСЛО переполнений в 61Y разр Пд - число суммирований, двоичного кода га время преобразования f К fj, - оставшийся в интеграторе (б, двоичный код младших разрядов результата суммирования. Время преобразования tfj может быть найдено из выражения с где ц - частота цикла обращения инт ратора. Определив f, из выражения (l) и разделив полученное значение на ifn , найдем выражение для среднего значенг частоты на выходе схемы за время пре образования ) V n,.-- , .,,.„ Второй член в скобках представляет из себя относительную погрешность пре разования- (f двоичного кода в частоту следования импульсов. Тогда можно записать, что г - 1 П U f J JV fcp ( полученного выражения .с высокой степенью приближения следует, что сред нее значение частоты преобразования прямо пропорционально величине преобразуемого кодаК и практически не зависит от времени преобразования /tp . „ Минимальное число суммирований, при котором будет обеспечена относител ная статическая погрешность не хуже заданной, может быть найдено из выражения1 Работа устройства происходит следующим образом. Импульсы опорной частоты f о от ге нератора опорной частоты 1 поступают на вход формирователя 2, где они испол зуются для формирования И тактовых импульсныхПоследовательностей, с помощью которых осуществляется сдвиг двоичных чисел в - разрядных регистрах 5 и 6. Кроме того, формирователь 2 формирует последовательность имлуль ,сов с пеоиопом ппятппо«ма т ляющих начало каждого цикла обращения интеграторов. В исходном состоянии в интеграторе текущего значений кода, (б, 7) обращает -ся двоичное число Kf, , Чгоо-гаетствующеё результату промежуточных вычислений N i 5rнкциoнaльный интегратор (б, 8) обнулён,триггер 3установлен в положение, : когда ключ 4 закрыт. Импульсом ,Nd , определяющим начало операции преобразования, производится запуск триггера 3, Очередной импульс Тц, расположенный на временной оси непосредственно после прохождения сигнала НО переводит триггер во второе устойчивое состояние, при КОТОРОМ ключ 4 открыт. С этого момента двоичное число, находящееся в регистре 5, начинает передаваться младшими разрядами вперед одновременно в сумматор 7 и через ключ 4 - в сумматор 8, Через вре.мя Тц двоичное число, содержащееся в первом интеграторе (интеграторе текущего значения кода), окажется расположенным в регистре 6 второго интегратора (функционального интегратора) таким образом, что его младщий разряд будет находиться перед входом в сумматор 8. Одновременно содержимое первого интегратора (S, 7) совершит полный оборот и расположится своим младшим}/ разрядом перед входом в сумматор 7, В дальнейшем с периодом повторения Уц будет происходить увеличение каждый раз на величину преобразуемого кода сс. держимого второго интегратора (6,8). Единицы переполнения в6 разряд двоичных , образующихся в сумматоре 8, не поступают через закольцовку в регистр 6, а выделяются и в виде последовательности импульсов подаются на выход схемы преобразования. В регистре 6 всегда остаются 6 младших разрядов двоичного числа, представляющего результат суммирования. В момент окончания операции преобразования импульсов КО. закрывается ключ 4 и обнуляется функциональный интегратор (6,8). Предложенное устройство реализовано на Куйбышевском авиационном заводе при создании для /испытаний самолета ТУ-154 специализированных информационно-измерительных систем, осуществляющих математическую обработку частоту но-импульсных сигналов по сложным алгоритмам. Устройство позволило в значительной степени уменьшить аппаратурную сложность вычислительных устройств за счет замены математических операций

магического преобразования частотно- импупьсяой информации.

Формула изобретения

Устройство для преобразования двоичного кода в имцу пьсную поспедоватепьность, содержащее формирователь (И1лпупьсрв, вход которого соединен с выходом генератора опорной частоты, а выходы со входами триггер выход которого соединен с первым управляющим входом кЬоча, второй управляющий вход которого подключен к шине окончания преобра- . зования, первый и второй сумматоры, выход каждого КЗ которых подключен ко входу ;соотвбтственного регистра двоичного кода, выход I которого соединен с первы м входом соответствующего су м матора, отличающееся теМ| что

. с пелыо упрощения устройства, в нем выход первого регистра двоичного кода через ключ соединен оо вторым входом второго сумматора, выход котор я о яялсе ся выходом устройства.

Истотнижн ннформапии, привстые во внимание при ахспертизе;

r,rJ5,

Авторы

Даты

1978-07-15—Публикация

1976-09-06—Подача