iS

СЛ

:Двонч11о-десятичный счетчик 2, сумма- тор 3 п блок 4 управления. Новым в Преобразователе является то, что он содержит формирователь 5 тетрады, формирователь 6 эквивалента, четыре элемента ИЛИ с первого 7 по четвертый 10, пять элементов И с первого П по

пятый 15 и первый 16 и второй 17 элементы НЕ. Преобразователь может быть использован при построении специализированного цифрового вычислителя устройства отображения информации Ьложной информацион1 й си стемы Tima . метеорадиолокатора. 3 з.п. ф-лы, 4 ил., 2 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь двоичного кода угла в двоично-десятичный код градусов | 1981 |

|

SU993243A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

Изобретение относится к вычислительной технике и предназначено для преобразования двоичных параллельных или числоимпульсных кодов угла с постоянным масштабом и дальности с переменным масштабом в двоично-десятичные коды градусов и километров соответственно. Цель изобретения - расширение класса решаемьпс задач преобразователем за счет обеспечения дополнительной возможности преобразования в двоично-десятичные коды двоичного параллельного или число-импульсного кода - дальности с переменным масштабом и , двоичного число-импульсного кода угла с постоянным масштабом. Преобразователь содержит двоичный счетчик 1,

; 1

; Изобретение относится к вычисли- ;тельной технике и предназначено для :преобразования двоичных параллельных или число-импульсных кодов , угла с ;постоянным масштабом и дальности с :переменным масштабом в двоично-деся- тичные коды градусов и километров со- I ответственно и может быть использовано при построении специализированного цифрового вычислителя (СЦВ) устройства отображения информации (УОИ) слож- ;ной информационной системы типа ме- :тео/радиолокатора (МРЛ). ; Цель изобретения - расширение ; класса решае 1ых задач за счет обеспе- чения дополнительной возможности пре- ;образования в двоично-десятичный код : двоичного параллельного или ч 1сло-им;пульсного кода дальности с перемен- ным масп табом и дво№пгого число-импульсного кода угла с постоянньм масштабом.

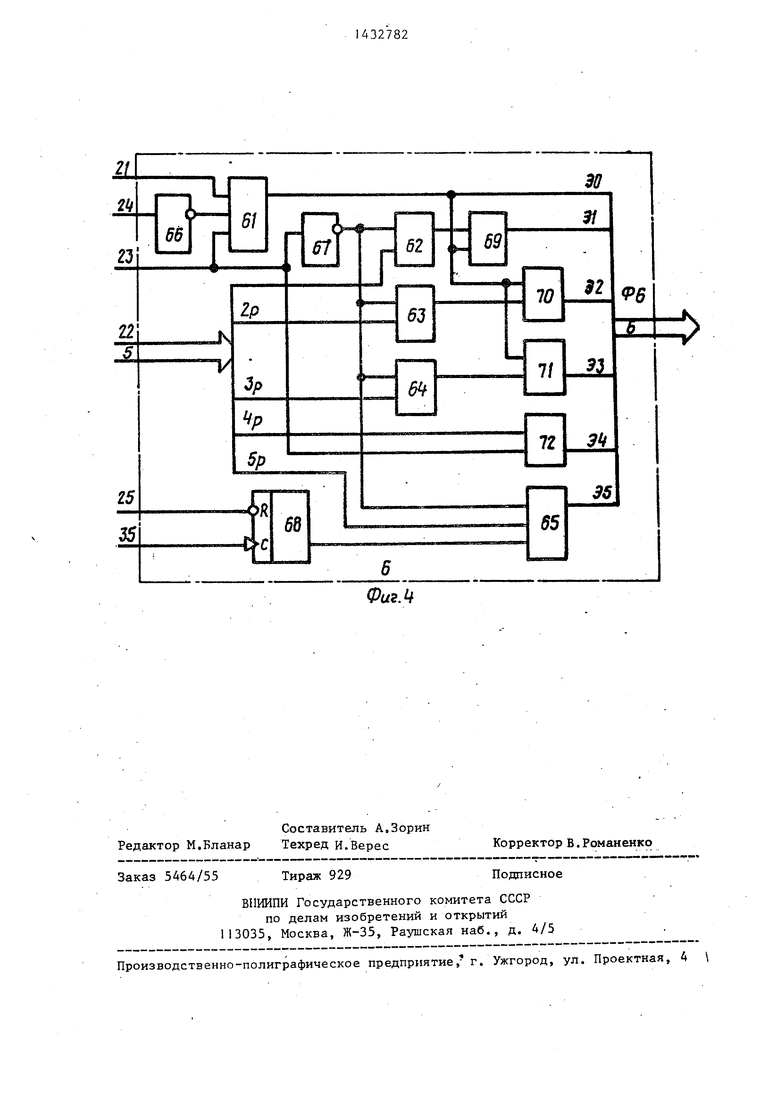

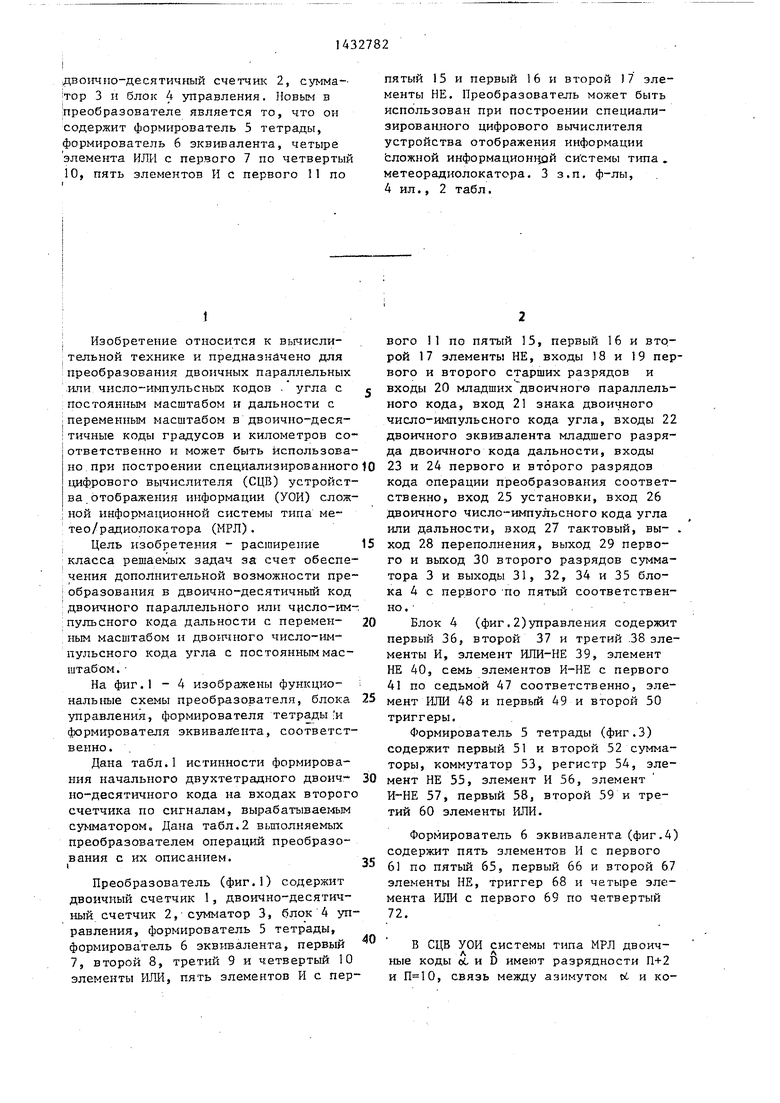

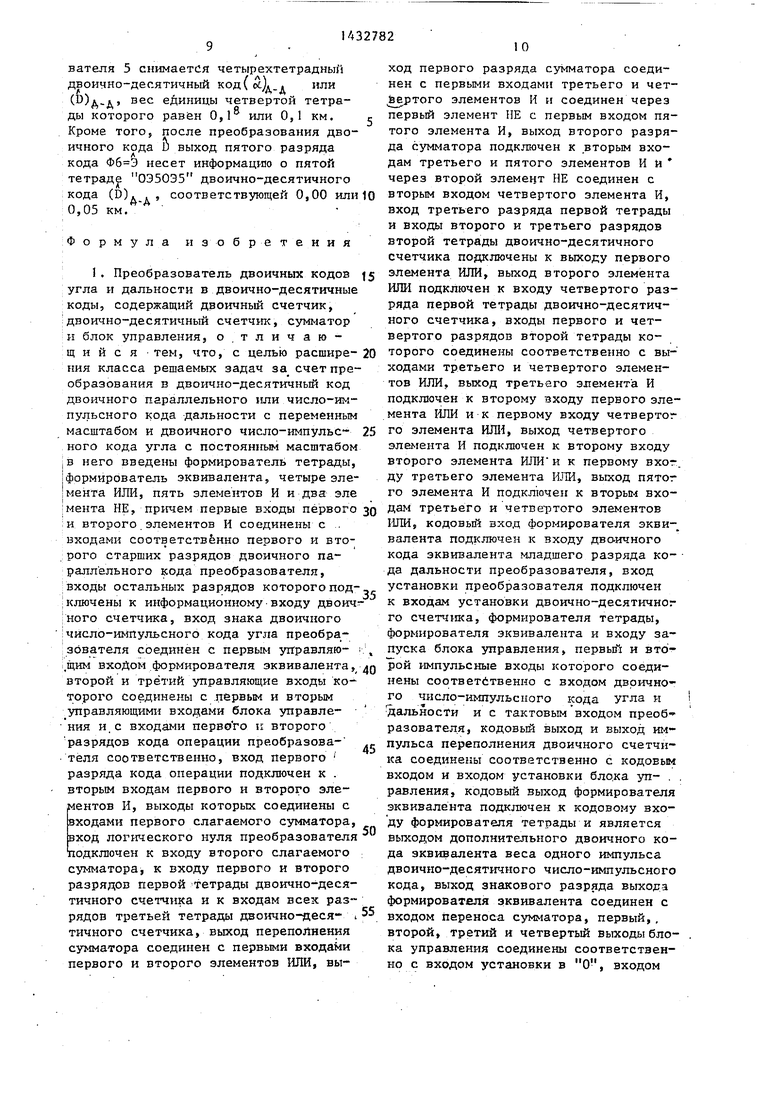

На фиг.1 - 4 изображены функцио- нальные схемы преобразователя, блока управления, формирователя тетрады . и формирователя эквивалента, соответственно. .

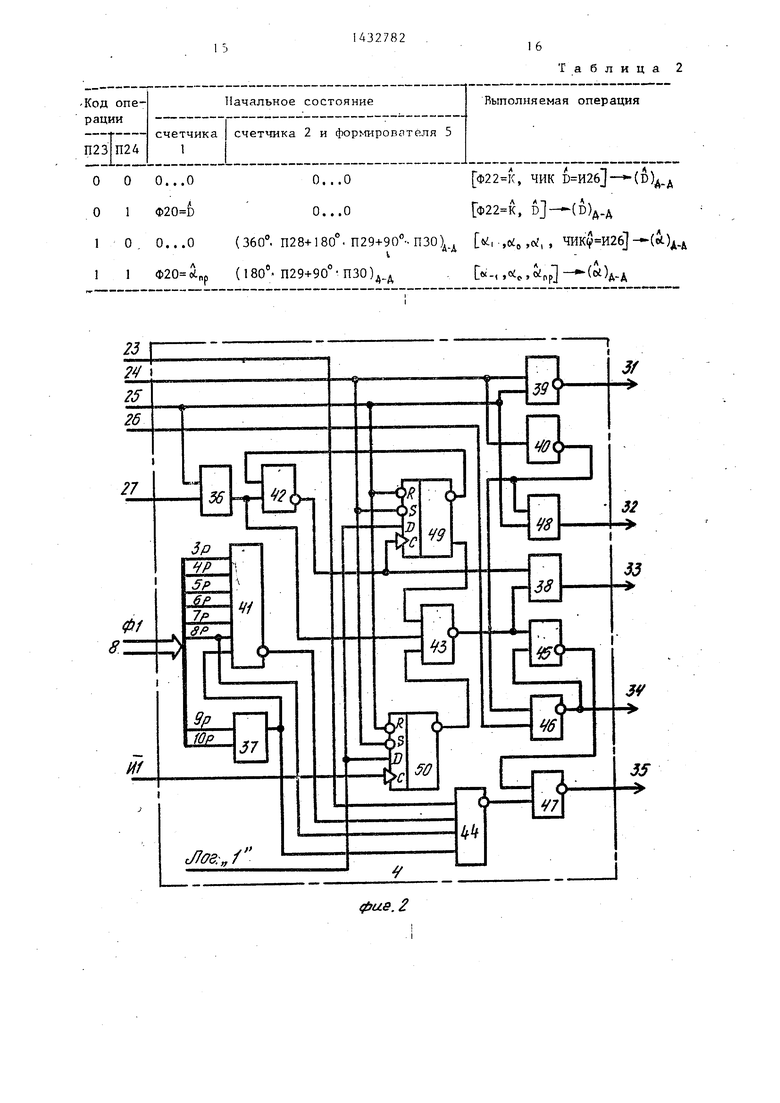

Дана табл.1 истинности формирования начального двухтетрадного двоич- но-десятичного кода на входах второго счетчика по сигналам, вырабатываег ым сумматором. Дана табл.2 вьшолняемых преобразователем операций преобразования с их описанием. I

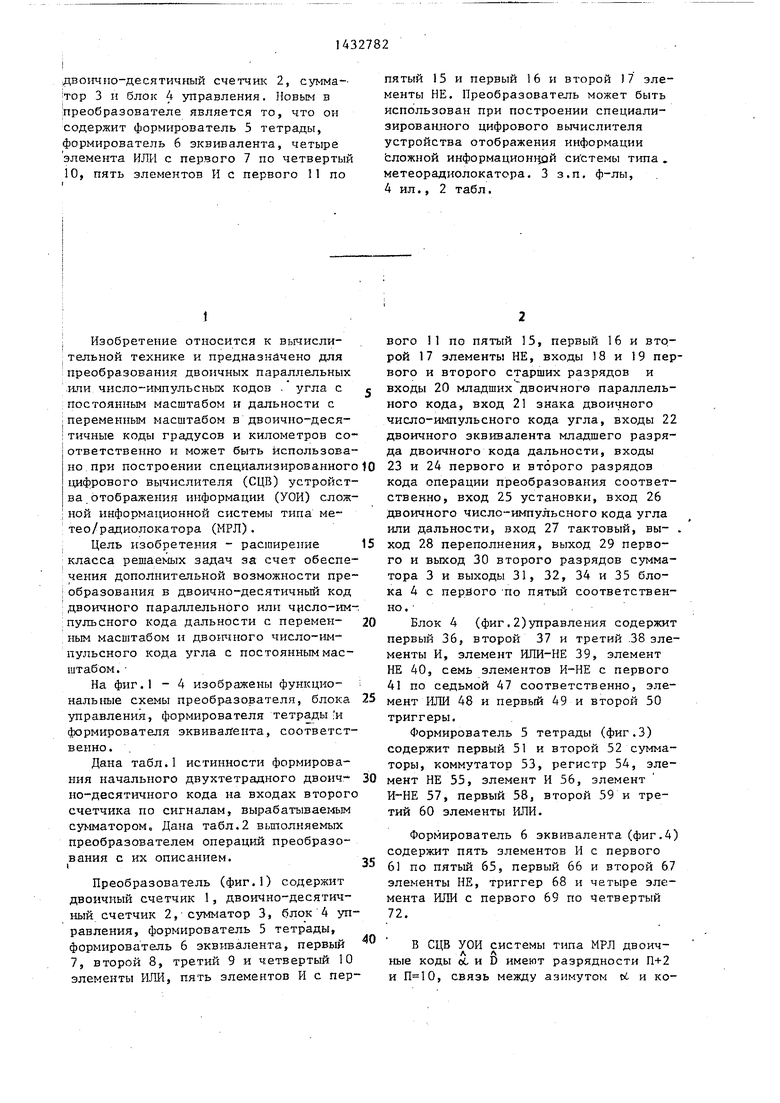

Преобразователь (фиг.1) содержит двоичный счетчик 1, двоично-десятичный счетчик 2, сумматор 3, блок 4 управления, формирователь 5 тетрады, формирователь 6 эквггаалента, первый 7, второй 8, третий 9 и четвертый 10 элементы И.ГШ, пять элементов И с перс0 5 0

5

0

5

вого 1 по пятый 15, первый 16 и втр- рой 17 элементы НЕ, входы 18 и 19 первого и второго старших разрядов и входы 20 младших двоичного параллельного кода, вход 21 знака двоичного число-импульсного кода угла, входы 22 двоичного эквивалента младшего разряда двоичного кода дальности, входы 23 и 24 первого и второго разрядов кода операции преобразования соответственно, вход 25 установки, вход 26 двоичного число-импульсного кода угла или дальности, вход 27 тактовый, вы- . ход 28 переполнения, выход 29 первого и выход 30 второго разрядов сумматора 3 и выходы 31, 32, 34 и 35 блока 4 с перйого -по пятый соответственно. .

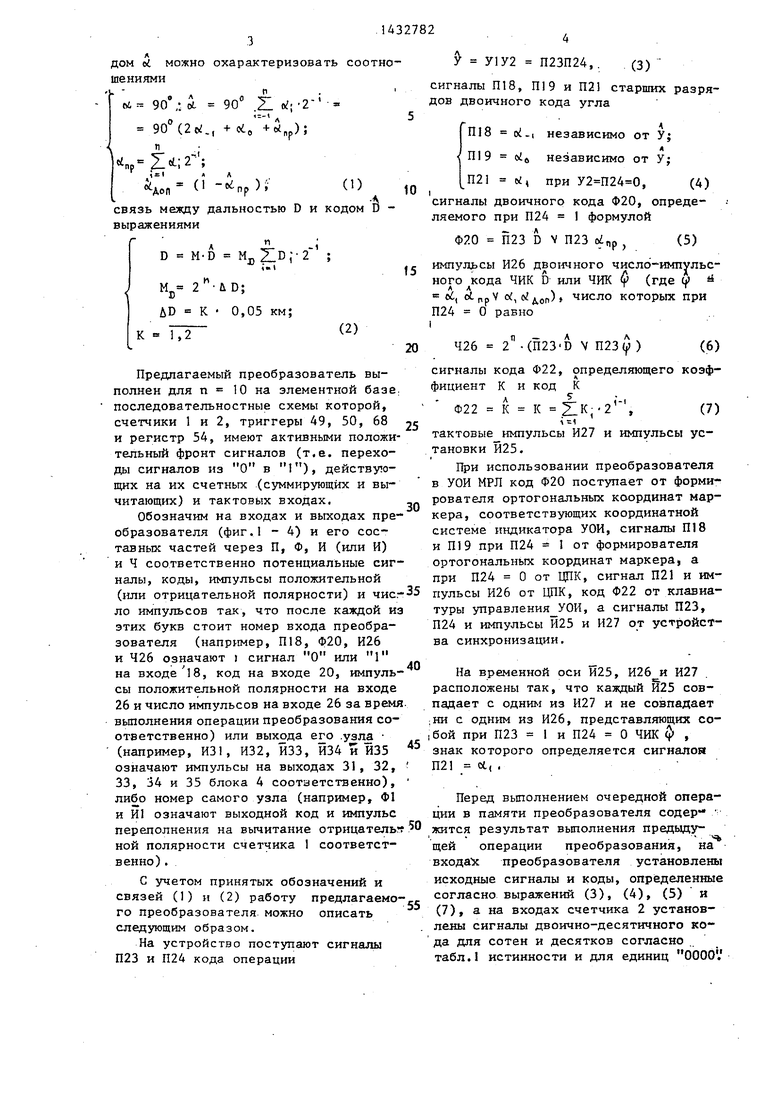

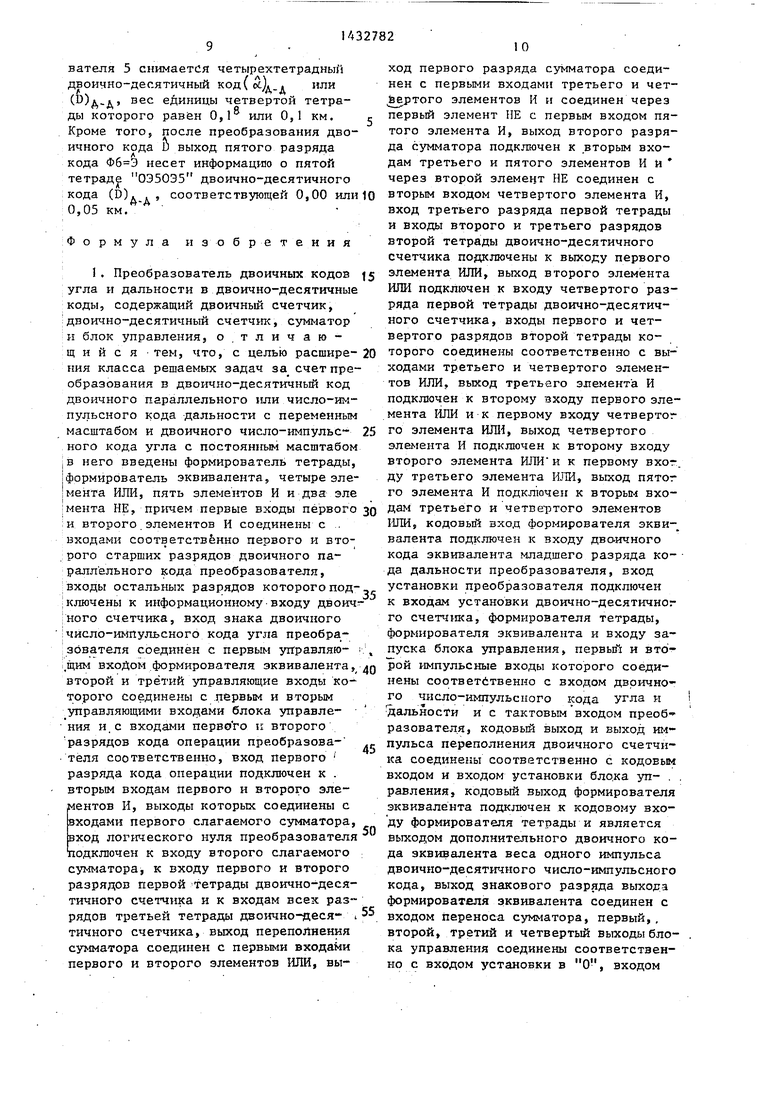

Блок 4 (фиг.2)управления содержит первый 36, второй 37 и третий .38 элементы И, элемент ИЛИ-НЕ 39, элемент НЕ 40, семь элементов И-НЕ с первого 41 по седьмой 47 соответственно, элемент ИЛИ 48 и первый 49 и второй 50 триггеры.

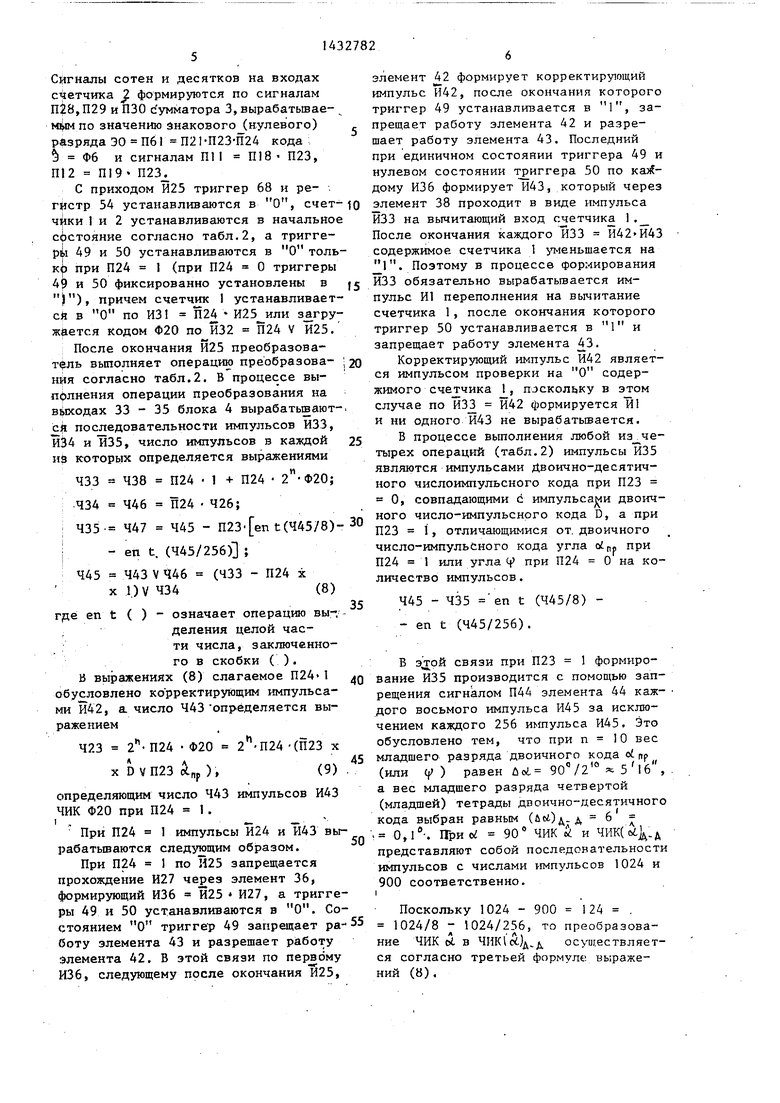

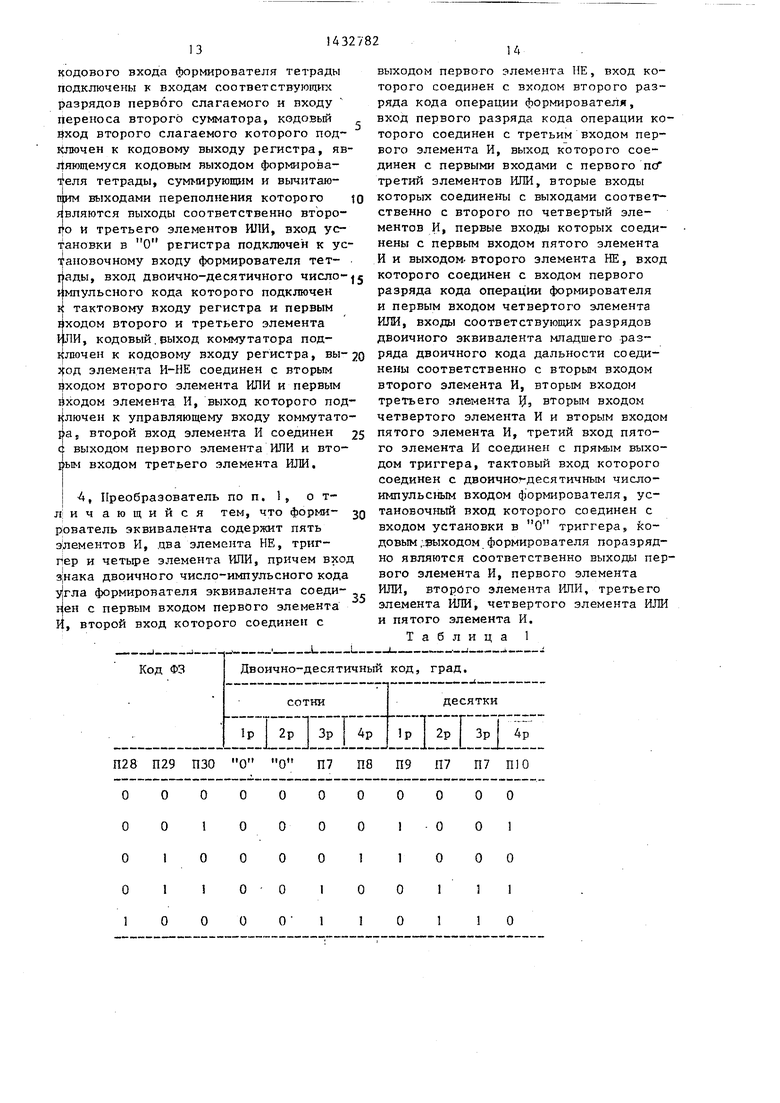

Формирователь 5 тетрады (фиг.З) содержит первый 51 и второй 52 сумматоры, коммутатор 53, регистр 54, элемент НЕ 55, элемент И 56, элемент И-НЕ 57, первый 58, второй 59 и третий 60 элементы ИЛИ.

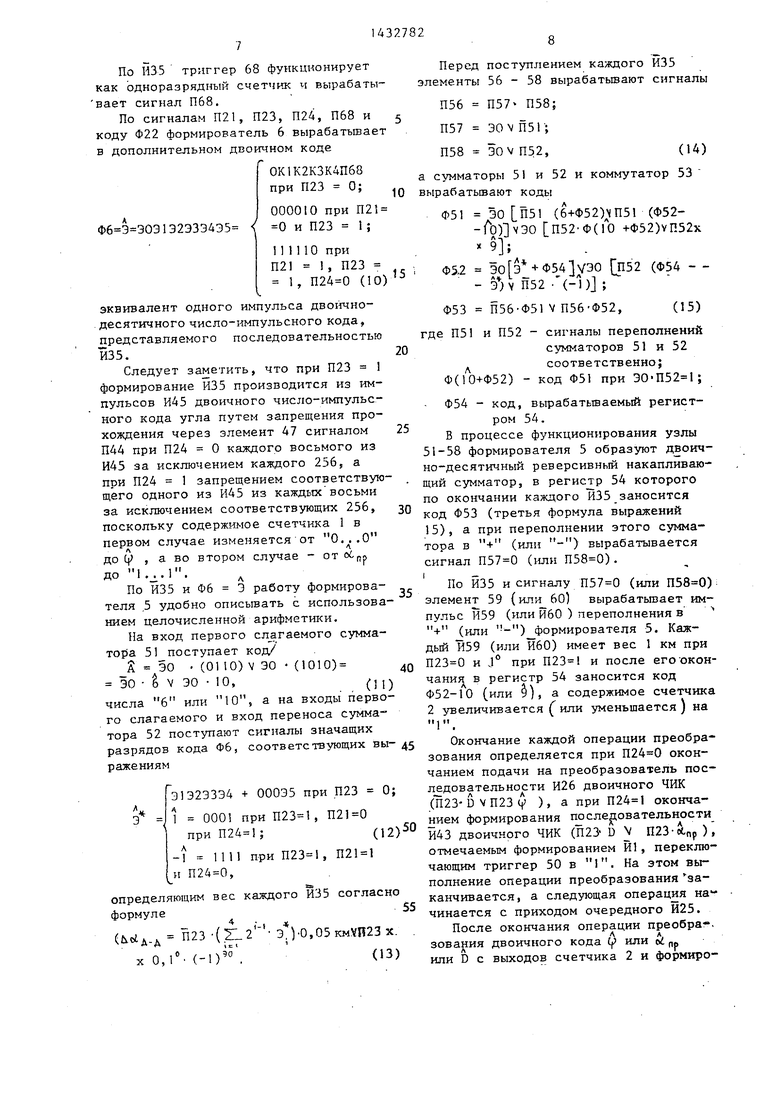

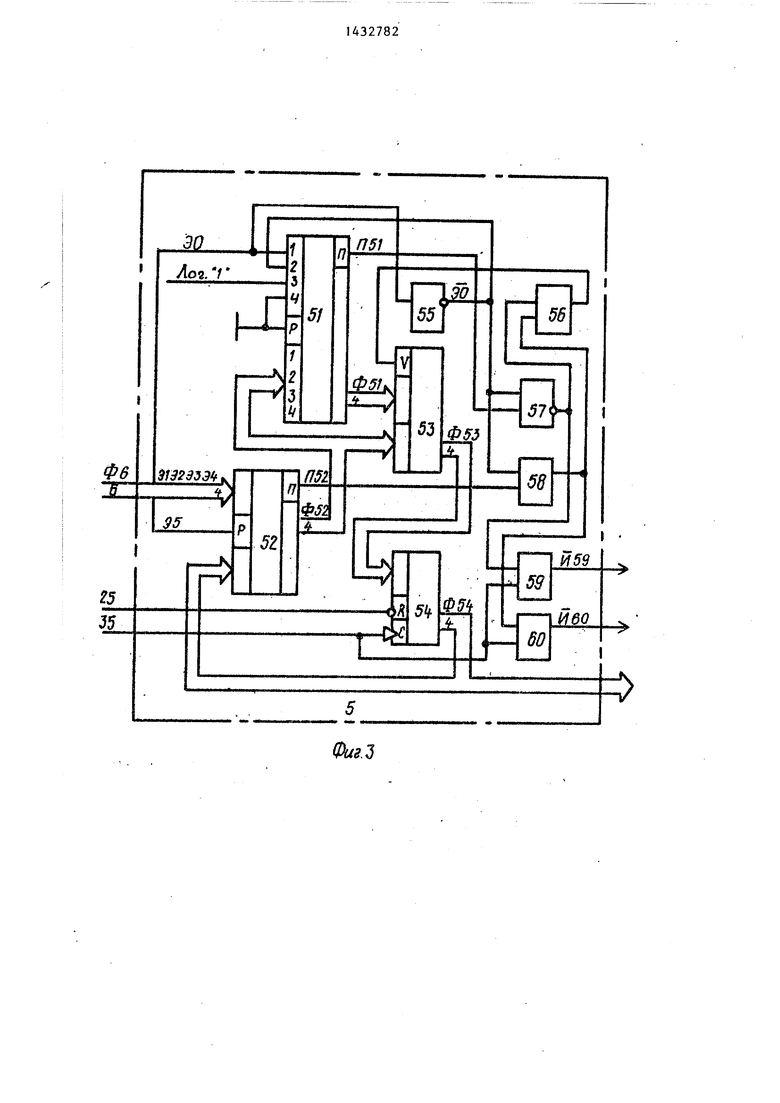

Формирователь 6 эквивалента (фиг.4) содержит пять элементов И с первого 61 по пятый 65, первый 66 и второй 67 элементы НЕ, триггер 68 и четыре элемента ИЛИ с первого 69 по четвертый 72.

40

В СЦВ УОИ системы типа МРЛ двоичные коды ОС и D имеют разрядности П+2 и , связь между азимутом ct и кодом ci шениями

можно охарактеризовать соотноЧоп

(1 -einp)i

связь между дальностью выражениями

D

-1

М.

К

(2)

Предлагаемый преобразователь выполнен для п 10 на элементной базе; последовательностные схемы которой, счетчики 1 и 2, триггеры 49, 50, 68 и регистр 54, имеют активными положительный фронт сигналов (т.е. переходы сигналов из О в 1), действующих на их счетных (суммирующих и вычитающих) и тактовых входах.

Обозначим на входах и выходах преобразователя (фиг.1 - 4) и его составных частей через П, Ф, И (или И) и Ч соответственно потенциальные сигналы, коды, импульсы положительной

сигналы кода Ф22, определяющего коэффициент К и код К

Ф22 К К

25

i ,

2-,

(7)

30

тактовые импульсы И27 и импульсы установки И25.

При использовании преобразователя в УОИ МРЛ код Ф20 поступает от формирователя ортогональных координат маркера, соответствующих координатной системе индикатора УОИ, сигналы П18 и П19 при П24 1 от формирователя ортогональных координат маркера, а при П24 О от ЦПК, сигнал П21 и им(1ти отрицательной полярности) и чис.-35 пульсы И26 от ЦПК, код Ф22 от клавиатуры управления УОИ, а сигналы П23, П24 и импульсы Й25 и И27 от устройства синхронизации.

45

ло импульсов так, что после каждой из этих букв стоит номер входа преобразователя (например, П18, ф20, И26 и 426 означают i сигнал О или 1 на входе 18, код на входе 20, импульсы положительной полярности на входе 26 и число импульсов на входе 26 за время, выполнения операции преобразования соответственно) или выхода его .узл (например, И31, И32, ЙЗЗ, И34 и И35 означают импульсы на выходах 31, 32, 33, 34 и 35 блока 4 соответственно), либо номер самого узла (например, Ф1 и И1 означают выходной код и импульс переполнения на вычитание отрицатель: ной полярности счетчика 1 соответственно) .

С учетом принятых обозначений и связей (1) и (2) работу предлагаемого преобразователя можно описать следующим образом.

На устройство поступают сигналы 023 и П24 кода операции

50

55

На временной оси И25, И27 расположены так, что каждый Й25 совпадает с одним из И27 и не совпадает ,ни с одним из И26, представляющих со- |бой при П23 1 и П24 О ЧИК ф , знак которого определяется сигналон П21 ot, .

Перед вьшолнением очередной операции в памяти преобразователя содер жится результат выполнения предыдущей операции преобразования, входах преобразователя установлены исходные сигналы и коды, определенные согласно выражений (3), (4), (5) и (7), а на входах счетчика 2 установлены сигналы двоично-десятичного ко да для сотен и десятков согласно табл.1 истинности и для единиц OOOOV

на

$ 71

У2 П23П24,. (3)

сигналы П18, П19 и П21 старших разрядов двоичного кода угла

независимо

от У;

А

независимо от У;

при , (4) I

сигналы двоичного кода Ф20, определяемого при П24 I формулой

Ф20

П23 D

V П23 oi,p,

(5)

импульсы И26 двоичного число-импульсного кода ЧИК D или ЧИК

(5:, (ippV о;, ,on),

(где (f i число которых при

П24 О равно

426

А

(6)

сигналы кода Ф22, определяющего коэффициент К и код К

Ф22 К К

5

i ,

2-,

(7)

0

тактовые импульсы И27 и импульсы установки И25.

При использовании преобразователя в УОИ МРЛ код Ф20 поступает от формирователя ортогональных координат маркера, соответствующих координатной системе индикатора УОИ, сигналы П18 и П19 при П24 1 от формирователя ортогональных координат маркера, а при П24 О от ЦПК, сигнал П21 и им45

50

55

На временной оси И25, И27 расположены так, что каждый Й25 совпадает с одним из И27 и не совпадает ,ни с одним из И26, представляющих со- |бой при П23 1 и П24 О ЧИК ф , знак которого определяется сигналон П21 ot, .

Перед вьшолнением очередной операции в памяти преобразователя содер жится результат выполнения предыдущей операции преобразования, входах преобразователя установлены исходные сигналы и коды, определенные согласно выражений (3), (4), (5) и (7), а на входах счетчика 2 установлены сигналы двоично-десятичного ко да для сотен и десятков согласно табл.1 истинности и для единиц OOOOV

на

Сигналы сотен и десятков на входах с«1етчика формируются по сигналам П28, П29 и ПЗО с умматора 3, вырабатьюае- М1ЯМ по значению знакового (нулевого) разряда ЭО П61 П21-П23-П24 кода Ф6 и сигналам ПИ П18 - П23, П12 П19 П23.

С приходом И25 триггер 68 и ре- . гнстр 54 устанавливаются в О, счет- чйки 1 и 2 устанавливаются в начальное ссЬстояние согласно табл,2, а тригге- pii 49 и 50 устанавливаются в О толь к|) при П24 1 (при П24 О триггеры 4 и 50 фиксированно установлены в il), причем счетчик 1 устанавливает- сй в О по ИЗ 1 П24- - жается кодом Ф20 по И32 П24 V И25.

После окончания И25 преобразователь выполняет операцию преобразова- ния согласно табл.2. В процессе выполнения операции преобразования на вькодах 33 - 35 блока 4 вырабатьшаютей последовательности импульсов ИЗЗ, ИЭ4 и , число импульсов в каждой из которых определяется выражениями

-Ф20;

433 434 435

438 П24 446 П24

1 + П24 426; 447 445 - (445/8)I - en t. (445/256) ;

445 443 V 446 (433 - П24 х

X 1.) V 434(8)

где en t ( ) - означает операцию выделения целой части числа, заключенного в скобки ( ).

В выражениях (8) слагаемое обусловлено корректирующим импульсами Й42, а число 443 определяется выражением

1

423 2 П24 Ф20 X D V П23 А-пр ) ,

(П23 X (9)

определяющим число 443 импульсов И43

4ИК Ф20 при П24 1.

,

При П24 1 импульсы И24 и И43 вырабатьшаются следующим образом.

При П24 1 по Н25 запрещается прохождение И27 через элемент 36, формирующий И36 И25 « И27, а триггеры 49 и 50 устанавливаются в О. СоБ эЧ;ой связи при П23 1 формирование И35 производится с помощью запрещения сигналом П4А элемента 44 каж- дого восьмого импульса И45 за исключением каждого 256 импульса И45. Это обусловлено тем, что при п 10 вес младшего разряда двоичного кода ot пр (или V) равен йсг 90V2 5 1б, а вес младщего разряда четвертой (младшей) тетрады двоично-десятичного кода выбран равным ()-A 6 . 0,1°-. Прис 90 4ИК & и 4ИК(.д представляют собой последовательности импульсов с числами тпульсов 1024 и

900 соответственно.

I

Поскольку 1024 - 900 124

стоянием О триггер 49 запрещает ра-55 1024/8 - 1024/256, то преобразоваботу элемента 43 и разрешает работуние 4ИК Ы, в 4ИК1с.) осуществляетЭлемента 42. В этой связи по первомуся согласно третьей формуле выражеИ36, следующему после окончания И25,ний (8).

0 5

0

5

0

5

злемент формирует корректирующий импульс И42, после окончания которого триггер 49 устанавлтзается в 1, запрещает работу элемента 42 и разрешает работу элемента 43. Последний при единичном состоянии триггера 49 и нулевом состоянии -триггера 50 по дому И36 формирует И43, который через элемент 38 проходит в виде импульса ИЗЗ на вычитающий вход счетчика 1, После окончания каждого ИЗЗ содержимое счетчика 1 у1-1еньщается на 1. Поэтому в процессе формирования ИЗЗ обязательно вырабатьгоается импульс И1 переполнения на вычитание счетчика 1, после окончания которого триггер 50 устанавливается в 1 и запрещает работу элемента 43.

Корректирующий импульс И42 является импульсом проверки на О содержимого счетчика 1, поскольку в этом случае по Й42 формируется lil и ни одного И43 не вырабатывается.

В процессе выполнения любой из четырех операций (табл.2) импульсы И35 являются импульсами Двоично-десятичного числоимпульсного кода при П23 0, совпадающими d импульсами двоичного число-импульсного кода D, а при П23 1, отличающимися от. двоичного число-импульСного кода угла при П24 1 или угла (f при П24 О на количество импульсов.

445 - 435 еп t (445/8) - - en t (445/256).

Б эЧ;ой связи при П23 1 формирование И35 производится с помощью запрещения сигналом П4А элемента 44 каж- дого восьмого импульса И45 за исключением каждого 256 импульса И45. Это обусловлено тем, что при п 10 вес младшего разряда двоичного кода ot пр (или V) равен йсг 90V2 5 1б, , а вес младщего разряда четвертой (младшей) тетрады двоично-десятичного кода выбран равным ()-A 6 . 0,1°-. Прис 90 4ИК & и 4ИК(.д представляют собой последовательности импульсов с числами тпульсов 1024 и

900 соответственно.

I

Поскольку 1024 - 900 124

5 1024/8 - 1024/256, то преобразоваПо И35 триггер 68 функционирует как одноразрядный счетчик ч вырабаты- вает сигнал П68.

По сигналам П21, П23, П24, П68 и коду Ф22 формирователь 6 вырабатывает в дополнительном двоичном коде

/

ОК1К2КЗК4П68 при П23 0;

000010 при П21 0 и П23 1;

111110 при П21 1, П23 1, (10)

эквивалент одного импульса дво11гчно- десятичного число-импульсного кода, представляемого последовательностью И35.

Следует заметить, что при П23 1 формирование И35 производится из импульсов И45 двоичного число-импульсного кода угла путем запрещения прохождения через элемент 47 сигналом П44 при П24 О каждого восьмого из И45 за исключением каждого 256, а при П24 1 запрещением соответствующего одного из И45 из каждых восьми за исключением соответствующих 256, поскольку содержимое счетчика 1 в первом случае изменяется от 0...0 до ф , а во втором случае - от о6„р до 1..1.

По И35 и Ф6 Э работу формирователя ,5 удобно описывать с использованием целочисленной арифметики.

На вход первого слагаемого сумматора 51 поступает код/

S ЭО . (ОНО) V 30 (1010) 30 V ЭО 10,,)

числа 6 или 10, а на входы первого слагаемого и вход переноса сумматора 52 поступают сигналы значащих разрядов кода Ф6, соответствующих вы- ражениям

Э

Э1Э233Э4 + ОООЭ5 при П23 0;

1 000 при ,

при (12)0

-t 1111 при ,

и ,

.

определяющим вес каждого ИЗ5 согласно формуле55

(Ыд.д П23 (212 Э)-0,05км гП23х. .

X 0,1

-м о

Перед поступлением каждого И35 элементы 56-58 вырабатьюают сигналы

П56 П57 П58;

П57 30V П5Г; П58 30V П52,

(lA)

а сумматоры 51 и 52 и коммутатор 53 вырабатьшают коды

Ф51 30 П51 (6+Ф52)П5Г (Ф52- -Го)чЗО П52 Ф(Го +Ф52)УП52х

Ф5.2 П52 (Ф54 - - 3)v П52 - (-1) ;

Ф53 П56-Ф51 V П56 Ф52,

(15)

20

25

30

40

45

35

;

)0

55

. .

)

где П51 и П52 - сигналы переполнений

сумматоров 51 и 52 дсоответственно;

Ф(10+Ф52) - код Ф51 при ЭО П52 1;

Ф54 - код, вырабатьшаемый регистром 54.

В процессе функционирования узлы 51-58 формирователя 5 образуют двоично-десятичный реверсивный накапливающий сумматор, в регистр 54 которого по окончании каждого И35 заносится код Ф53 (третья формула выражений 15), а при переполнении этого сумматора в + (или -) вырабатывается

сигнал (или ).

1-.

По И35 и сигналу (или ) элемент 59 () вырабатьшает импульс И59 (или И60 ) переполнения в + (или -) формирователя 5. Каждый Ti59 (или Ибо) имеет вес 1 км при и J° при П23 и после его окончания в регистр 54 заносится код Ф52-10 (или у), а содержимое счетчика

2увеличивается ( или уменьшается ) на 1.

Окончание каждой операции преобразования определяется при окончанием подачи на преобразователь пос- л едовательности И26 двоичного ЧИК (n23-Dvn23v ), а при окончанием формирования последовательности Й43 двоичного ЧИК (П23 D V П23-Лпр ), отмечаемым формированием И1, переключающим триггер 50 в I. На этом выполнение операции преобразования заканчивается, а следующая операция на чинается с приходом очередного Й25.

После окончания операции преобра-. зования двоичного кода (f или oi „„ или D с выходов счетчика 2 и формирователя 5 снимается четырехтетрадный двоично-десятичный код(й.}д.д или (Ь), вес единицы четвертой тетрады которого равен 0,1 или 0,1 км. Кроме того, после преобразования двоичного кода D выход пятого разряда кода несет информацио о пятой тетраде ОЭ50Э5 двоично-десятичного

кода (D) 0,05 км.

А-А

соответствующей 0,00 или

Формула изобретения

5

0

5

0

5

0

5

0

5

ход первого разряда сумматора соединен с первыми входами третьего и чет- ртого элементов И и соединен через первый элемент НЕ с первым входом пятого элемента И, выход второго разряда сумматора подключен к .вторым входам третьего и пятого элементов И И через второй элемент НЕ соединен с вторым входом четвертого элемента И, вход третьего разряда первой тетрады и входы второго и третьего разрядов второй тетрады двоично-десятичного счетчика подключены к выходу первого элемента ИЛИ, выход второго элемента ИЛИ подключен к входу четвертого разряда первой тетрады двоично-десятичного счетчика, входы первого и четвертого разрядов второй тетрады которого соединены соответственно с выходами третьего и четвертого элементов ИЛИ, выход третьего элемента И подключен к второму входу первого элемента ШШ и к первому входу четвертог го элемента ИЛИ, выход четвертого элемента И подключен к второму входу второго элемента ИЛИ и к первому вхог. ду третьего элемента ИЛИ, выход пятог го элемента И подключен к вторым входам третьего и четветгтого элементов ИЛИ, кодовьй вход формирователя экви- валента подключен к входу двоичного кода эквивалента младшего разряда ко- да дальности преобразователя, вход установки преобразователя подключен к входам установки двоично-десятичног го счетчика, формирователя тетрады, формирователя эквивалента и входу запуска блока управления, первый и вто - рой импульсные входы которого соединены соответственно с входом двоичного число-импульсного кода угла и дальности и с тактовым входом преобразователя, кодовый выход и выход импульса переполнения двоичного счетчика соединены соответственно с кодовым входом и входом установки блока уп- . . равлениЯ} кодовый выход формирователя эквивалента подключен к кодовому входу формирователя тетрады и является выходом дополнительного двоичного кода эквивалента веса одного импульса двоично-десятичного число-импульсного кода, выход знакового разряда выхода формирователя эквивалента соединен с входом переноса сумматора, первый,, второй, третий и четвертый выходы блока управления соединены соответственно с входом установки в О, входом

установки в начальное состояние, входом вычитания и входом суммирования двоичного счетчика, пятый выход блока управления соединен с входами двоично-десятичных число-импульсных входов формирователей эквивалента и тетрады, выходы переполнения на суммирование и вычитание формирователя тетрады соединены соответственно с суммирующим и вычитающим входами двоично-десятичного счетчика, кодовые выходы двоично-десятичного счетчика и формирователь тетрады и выход младшего разряда выхода формирователя экБивалента являются информационными выходами преобразователя, выходом импульса конца преобразования которого является импульс переполнения на выг читание двоичного счетчика.

входами соответственно второго и третьего элементов И-НЕ, первый управляющий вход блока управления подключен к первому входу четвертого элемента И-НЕ, входы с второго по четвертый которого соединены соответственно с вьпсодом первого элемента И-НЕ, с входом младшего из группы старших разрядов кодового входа блока управления и с выходом второго элемента И, выход первого элемента И подключен к вторым входам второго и третьего элементов И-НЕ, выход второго элемента И-НЕ соединен с тактовьм входом первого триггера и с первым входом третьего элемента И, инверсный выход второго триггера подключен к третьему входу третьего элемента И- - НЕ, выход которого соединен с вторым входом третьего элемента И и с перог 0

5 Q

5

0

5

0

5

вым входом пятого элемента И-НЕ, второй вход которого подключен к выходу шестого элемента И-НЕ, выход пятого элемента И-НЕ подключен к первому входу седьмого элемента И-НЕ, второй вход которого соединен с выходом чет вертого элемента И-НЕ, вход логической единицы блока управления соединен с D-входами триггеров, входы установки в 1 которых соединены с вторым входом элемента ИЛИ-НЕ, входом элемента НЕ и вторым управляющим входом блока управления, первЬш импульсный вход которого соединен с первым входом шестого элемента И-НЕ, выход элемента НЕ подключен к вторым входам элемента ИЛИ и шестого элемента И-НЕ, второй вход первого элемента И и тактовый вход второго триггера соединены соответственно с вторым импульсным входом и входом установки блока управления, выходы с первого по пятый блока управлеш я соединены с выходами соответственно элемента ИЛИ-НЕ, элемента ИЛИ, третьего элемента И, шестого элемента И-НЕ и седьмого элемента И-НЕ.

3, Преобразователь по п. 1, с т- личающийся тем, что ..формирователь тетрады содержит.два сумматора, коммутатор, регистр, элемент НЕ, элемент И, элемент И-НЕ и три элемента ИЛИ, причем первый вход первого элемента ИЛИ соединен с первым входом элемента , выходом элемен- .та НЕ и входом второго разряда первого слагаемого первого су1 1матора, выход переполнения которого соединен с вторым входом элемента И-НЕ, вход зна- , кового разряда кодового входа формирователя тетрады подключен к входу элемента НЕ и входу первого старшего разряда первого слагаемого первого сумматора, входы третьего и четвертого разрядов первого слагаемого которого соединены с входами соответственно логической единицы и нуля форми- . рователя тетрады, вход логического нуля Которого соединен с входом переноса первого сумматора, кодовый вы- : ход которого соединен с первым кодовым входом коммутатора, второй кодовый вход которого соединен с кодовым входом второго слагаемого первого сумматора, и кодовым выходом второго сум- ,, матора, выход переполнения которого соединен с вторым входом первого элемента ИЛИ, входы значаш 1х разрядов

кодового входа формирователя тетрады подключены к входам соответствующих разрядов первбго слагаемого и входу переноса второго сумматора, кодовый Эход второго слагаемого которого под- Ключен к кодовому выходу регистра, яв- 4яю1демуся кодовым выходом формирова- тетрады, суммирующим и вычитаю- выходами переполнения которого tO являются выходы соответственно второго и третьего элементов ШШ, вход установки в О рЕГИстра подключен к ус- taHOBO4HOMy входу формирователя тет- рады, вход двоично-десятичного число- j 1|мпульсного кода которого подключен 1 тактовому входу регистра и первым йходом второго и третьего элемента |ЛИ, кодовый. рыход коммутатора под- i|jno4eH к кодовому входу регистра, вы- jQ од элемента И-НЕ соединен с вторым 4ходом второго элемента ИЛИ и первым 1Ыодом элемента И, выход которого под- 1|лючен к управляющему входу коммутато- а, второй вход элемента И соединен 25 G ВЫХОДОМ первого элемента ИЛИ и вторым

I

входом третьего элемента ИЛИ.

I -4, Преобразователь по п. 1 , о т- л:ич ающийся тем, что формирователь эквивалента содержит пять э;лементов И, два элемента НЕ, триг- rlep и четыре элемента ИЛИ, причем вход нака двоичного число-импульсного кода

30

выходом первого элемента НЕ, вход которого соединен с. входом второго разряда кода операции формирователя, вход первого разряда кода операции ко торого соединен с третьим входом первого элемента И, выход которого соединен с первыми входами с первого псГ третий элементов ИЛИ, вторые входы которых соединены с выходами соответственно с второго по четвертый элементов И, первые входы которых соединены с первым входом пятого элемента И и выходом-второго элемента НЕ, вход которого соединен с входом первого разряда кода операции формирователя и первым входом четвертого элемента ИЛИ, входы соответствующих разрядов двоичного эквивалента младшего разряда двоичного кода дальности соединены соответственно с вторьп- входом второго элемента И, вторым входом третьего эпелиента У, вторым входом четвертого элемента И и вторым входом пятого элемента И, третий вход пятого элемента И соединен с прямым выходом триггера, тактовый вход которого соединен с двоичнот-десятичным число- импульсным входом формирователя, установочный вход которого соединен с входом установки в О триггера, кодовым ,:выходом формирователя поразрядно являются соответственно выходы пе вого элемента И, первого элемента

У|гла формирователя эквивалента соеди- ИЛИ, второго элемента ИЛИ, третьего

I. . ,. J «J гч гт 1«лаТ2Ч ТДГГМ TO TiT3ei-i- rij -r-i.4 f гт ft t г Tf Tf f M TT

нен с первым входом первого элемента И, второй вход которого соединен с

элемента ИЛИ, четвертого элемента ИЛИ и пятого элемента И.

Таблица 1

выходом первого элемента НЕ, вход которого соединен с. входом второго разряда кода операции формирователя, вход первого разряда кода операции которого соединен с третьим входом первого элемента И, выход которого соединен с первыми входами с первого псГ третий элементов ИЛИ, вторые входы которых соединены с выходами соответственно с второго по четвертый элементов И, первые входы которых соединены с первым входом пятого элемента И и выходом-второго элемента НЕ, вход которого соединен с входом первого разряда кода операции формирователя и первым входом четвертого элемента ИЛИ, входы соответствующих разрядов двоичного эквивалента младшего разряда двоичного кода дальности соединены соответственно с вторьп- входом второго элемента И, вторым входом третьего эпелиента У, вторым входом четвертого элемента И и вторым входом пятого элемента И, третий вход пятого элемента И соединен с прямым выходом триггера, тактовый вход которого соединен с двоичнот-десятичным число- импульсным входом формирователя, установочный вход которого соединен с входом установки в О триггера, кодовым ,:выходом формирователя поразрядно являются соответственно выходы первого элемента И, первого элемента

ИЛИ, второго элемента ИЛИ, третьего

гч гт 1«лаТ2Ч ТДГГМ TO TiT3ei-i- rij -r-i.4 f гт ft t г Tf Tf f M TT

элемента ИЛИ, четвертого элемента ИЛИ и пятого элемента И.

Таблица 1

О О 1

1

О 1 О

1

0...0

0...0

.„

0...0

, ЧИК (Г))д.д . Dj-(Г))д.д (360° П28+180°. П29+90 -. П30. i, , ,с, , (Л)д.д

0...0 „о

(180- П29+90° ПЗО)

4-А

«-, ,о,(ы)

2д

Таблица 2

4-А

«-, ,о,(ы)

фае. 2

Р|

Лог. /

Х :

5/

3132333

35

J2

/7

j2

Ф51

rV

1 л

Фиг.

/75/

Ж

55

53

Фл

5

5I-J/

5

ф

60

Редактор М.Бланар

Составитель А.Зорин Техред И.Верее

Заказ 5464/55

Тираж 929

ВИИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Корректор в. Романенко

Подписное

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1078422A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода угла в двоично-десятичный код градусов | 1981 |

|

SU993243A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-23—Публикация

1987-04-13—Подача