(54) АСИНХРОННЫЙ АНАЛСТО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1975 |

|

SU530449A1 |

| Преобразователь напряжение-код | 1977 |

|

SU661784A1 |

| Устройство для самонастраивающейся токовой защиты электродвигателя | 1986 |

|

SU1339735A1 |

| Аналого-цифровой преобразователь поразрядного кодирования | 1980 |

|

SU936418A1 |

| Многоканальный аналого-цифровой преобразователь | 1987 |

|

SU1444945A1 |

| Регистр | 1981 |

|

SU1024989A1 |

| ВСЕСОЮЗНАЯ :"tHTtKi-^KflH**F^^^ | 1973 |

|

SU388229A1 |

| МАТРИЧНЫЙ КОММУТАТОР С ПРОГРАММИРУЕМОЙ ЛОГИКОЙ | 2003 |

|

RU2251792C2 |

| Устройство для преобразования напряжения в код системы остаточных классов | 1981 |

|

SU1029410A1 |

| Способ многоканального аналого-цифрового преобразования сигналов и устройство для его осуществления | 1986 |

|

SU1411972A1 |

I

Изобретение относится к импупьсной технике и может быть йспйпьэовано дгш поразрядного кодирования аналоговых сиг напов с максимально достижимей точно стью и быстродействием.

Известен асинхронный аналогр-ойфровой преобразователь поразрядного кодирования с совмещенными тактами сброса н занес ння, содерткащий нул1 орган, цифро-анало говыя преобразователь схему, поразрядHiHTo уравновешивания, каждый разряд котс рой включает триггер. Два кпапава, лйвао задержки, схему ИЛИ и генератор импупь сов ij.

f

. . .

Однако это устрс ство в каждом ра роде содерхшт синхра1газнру1сиций эпементгенерато импульсов, определякиднй такт работы, и корректирующий элеменг-цинию задержки (исключающую преждевременный запуск очередного разряда. Такое вклю-. чеиие не позволяет получить максимапьцое быстродействие преобразователя, в соотве ствии с факшчески необходимым- временем устанюки каждого разряда, которое

уменьшается по мере уменьшения старшиисгва разрядов.

Из иввестных преобразователей ванболее близким по технической сущности к предлагаемому является асинхронный аналог -цифровой преобразователь поразря и ного кодирования, содержащий в каждом разряде схему сравнения с весовымрезио;тором в цифро-анапоговый преобразователь

Однако это устройство характеризуемся низкой точностью кодирования и невысокой функциональной над кностью.

Цель изобретения - получение сочетания максимально достижимой точности и быстродействия аналого-цифрового преобразователя поразряднся о кодирования.

Поставленная цель достигается тем, что в преобразоватедь, содержаашй два компаратора, первые входы котортлх подключены к выходам соответствующих циф ро анапоговых преобразователей и через резисторы - к щине входногостгнала, а вторйые входы - к щине земля, введен регистр поразрядного уравновешивания, каждый разряд которого включает три tlS

361671

риггера, трехвходовый элемент ИЛИ-НЕ етырехвходовый элемент И, два двухвхоовых элемента И, два двухвходовых элеента 11ЛИ, двухвходовый элемент , ричем S-вход первого -триггера соеинен с выходом чегырехвхрдового эпемен- . а И, первый вход которого соединен с пряым выходом первого компаратора, второй вход - с шиной сигнала запуска, третий ход - с инверсным выходом второго компаратора, а четвертый вход соединен с ю нверсным выходом трехвходового элемента ИЛИ-НЕ, прямой выход которого соединен с Я -входом первогоНЬ-триггера, первый вход трехвходового элемента ИЛИ-НЕ соединен с первыми входами двухвходовых эпемёнтов ИЛИ, прямым выходом второго Ц$-триггера и шиной выходных кодов, второй вход соединен с Т1-входами вторсяо и третьего R6-триггеров и шиной сигнала сброса, а третий вход соединен 20 с вто{м 1М входом двухвходовых элементов Или, ИЛИ-НЕ и прямым выходом третьего К S -триггера, g-входы второго и третьего &-1 жггеров подключены к ш 1ходам первого и вторсж о двухвходовых25

элементов И, первые входы когоряых соединены со вторым входом первого двухвходового элемента ИЛИ, первым входом двухвходового элемента и прямым выходом первого Я$-триггера, вторые вхо- ЭО ды которых соединены с прямым и инвероным выходами второго и первого компараторов соответственно, выходы первого двухвходового элемента ИЛИ и двухвходового элемента ИЛИ-НЕ соединены с35 входами первого и BTOpwo цифро-аналоговых преобразователей соответственно, а выход второго двухвходового элемента ,ИЛИ подключен к шине сигнала запуска оче :эдного разряда. 40

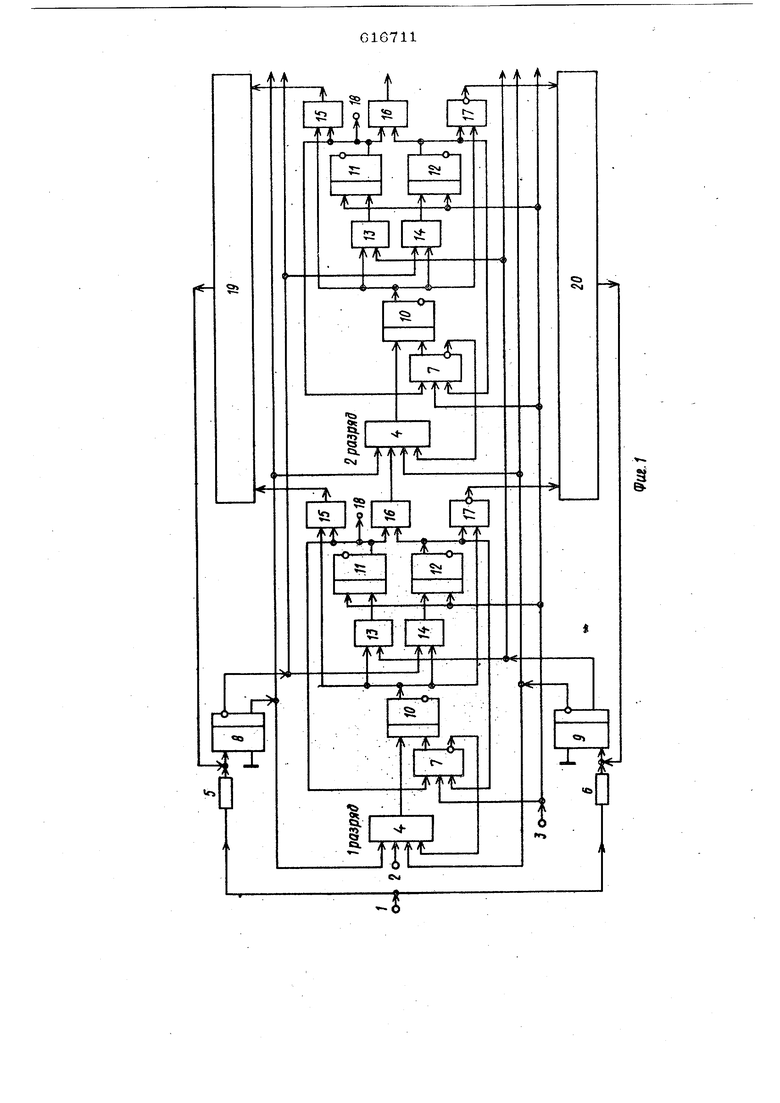

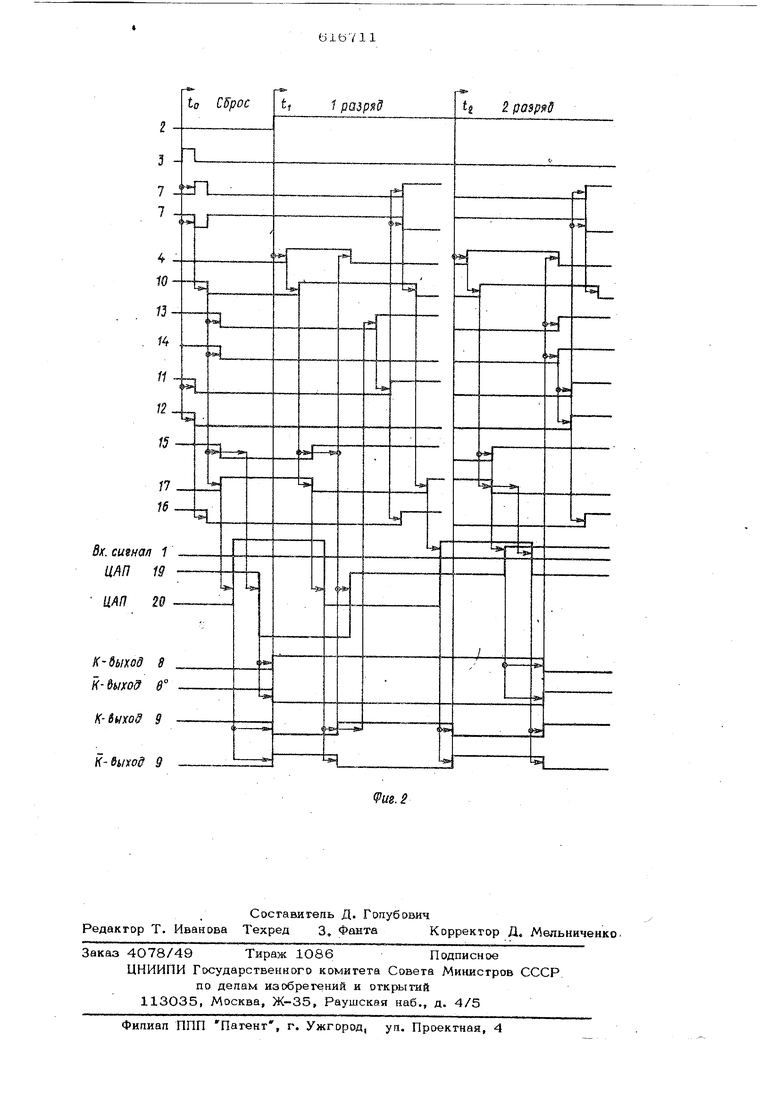

На фиг. 1 преде тав1№на .структурная электрпеская схема аналого-цифрового преобразователя, на фиг. 2 - временные диаграммь, поясняющие его работу.

Устройство содержит шину 1 второго сигнала, шину 2 сигнала запуска, шинуЗ сигналы сброса, четырехвходовый эпемент И 4, резисторы 5 и 6, трехвходовый элемент ИЛИ-НЕ 7, компараторы 8 и 9, KS - триггер Ю, 11 и 12, двухвходовые элементы И 13 и 14, двухвходовые элементы ИЛИ 15 я 16, двухвходовый sneмент ИЛИ - НЕ 17, шину 18 выходных кодовых сигналов, цифро-аналоговые преобразователи 19 и 2О, причем первые входы компараторов 8 и 9 подключены к вы1 ходам цифро-аналоговых преобразователей 19 и 20 соответственно и через резистск оы 5 и 6 - к шине 1 входного сигнала.

I4

а вторые на входы соединены с шиной земпя, S-выход К -григгера 1О соединен с выходом элемента И 4, первый вход которого 1 соединен с прямым выходом компаратора 8, второй вход - с шиной 2 сигнала запуска, третий вход с инверсным выходом компаратора 9, а червертый вход - с инверсным выходом элемента ИЛИ-НЕ 7, прямой выход которого соединен с Т -входом R6-триггера 10, первый Е«од элемента ИЛИ-НЕ 7 соединен с первыми входами двухвходовых элементов ИЛИ 15 и 16, прямым выходом К S-триггера 11 и шиной 18 выходных . кодовых сигналов, второй вход - с К -вхдами Т -трягге ров 11 и 12 и.шинсЛ 3 сигнала сброса, а третий вход - с вто. входами элементов ИЛИ 15 и 16 элемента-ИЛИ-НЕ 17 и прямым выходом -триггера 12, S-входы Я S-триггеров

IIи 12 подключены к выходам элементов И 13 и 14 соответственно, первые входы которых соединены с вторым входом элемента ИЛИ 15, первым входом элемента ИЛИ-НЕ 17 и прямым выходов КЭ-триггера 10, вторые входы которых соединены с прямым и инверсным выходами кмлпаратора 9 и 8 соответственно выходы элемента ИЛИ 15 и элемента ИЛ№-НЕ 17 соединены с входами цифроаналоговых преобрасгователев 19 и 20 соответственно, а выход элемента ИЛИ 16 подключен к шине 2 сигнала запуска оч&редного разряда.

Устройство работает следующим образом.

Напряжение входного сигнала поступае на шину 1 и задает черезрезисторы 5 и 6 ток J )1 , который сравнивается поразрядно на входах компараторов 8 и 9 с коммутируека 1ми эталонными токами з яро-аналоговых преобразователей 19 и 20 Коммутация эталонных токов осуществляется асинхронно при помощи регистра поразрядного уравновешивания.

Импульсный сигнал сброса по шине 3 в момент опоступает непосредственно на И -входы ТГ5-триггеров 11 и 12 и через трехвходовый элемент ИЛИ-НЕ 7на Я -входы Ий-триггераЮ, в результате чеГ о нулевые сигналы двухвходовых элементов ИЛИ 15 отключают все эталонные токи цифро-аналогового преобразователя 19 ( 2 За О),-а единичные сиг налы двухвходовых элементов 17 включают все эталонные токи цифро-аналогового преобразователя 2О ( SJ

2 9мАКС Р fOM ток входного СИГнала 3 Л э 0 переклкмает ком56паратор 8 в вдиничное состояние, а ток 3jj E3jC3j переключает компаратор 9 в нупевое ссгсгояние. Это состояние преобраэоватепя является исходным. Запуск первого разряда преобразоватепя осуществляется путем иодачн в момен fe на ишну 2 единичного сигнала, которы совпадая с единичными сигналами прямого выхода компаратора 8, ииверсного ш 1хоДа компаратора 9 и выхода трехвходового элемента ИЛИ-НЕ 7, переключает -триггер 1О в единичное состояние. Единичный сигнал двухвходового элемента ИЛИ 15 включает эталонный ток первого разрядаЗх.цифро-аналогового преобразова твпя 19, а нулевой сигнал двухвходов ГО элемента ИЛИ-НЕ 17 откшочает этало ный ток первого разряда3 1Шфр« -аналогового преобразователя 2О. При этом могу.т иметь место два случая: ток сохраняет единичное состоя 1ше компаратора 8 а ток . ч. э ЭААА Jj переключает компаратор 9 в единичное состояние (см. г. 2)j ток переключает компаратор 8 в нулевое сосостоянне, а ток S3,j - со .раняет нулевое состояние компаратора 9. В первом случае единичные сигналы прямого выхода компаратора 9 и Гера 10, совпадая на двухвходовом элементе И 13, включает RS-триггер 11 в единичное состояние, которое через трехВХОДОБЫЙ элемент ИЛИ-НЕ 7 Н%;-триггер 1О и двухвходовый элемент ИЛЙ-НЕ 17 включает ток 3 цифро-аналогового П1 еобразовагеля 20.Тогда ток 3 S3., la переключает компаратор -. МАКС 3 y-t „.f f 9 в нуиевое состояние. Единичные сигналы двухвходового элемента ИЛИ .16, прямого выхода коктаратор 8 и инверсного вьисода компаратора 9 трехвходового элемента ИЛИ-НЕ 7 вторило разряь да запускают очередной второй разряд .преобразователя. Единичный сигнал на ши не 18 является кодовым сигналом. Во втором случае , единичные сигналы инверсного выхода компаратора 8 и TIS- триггера 1О , совпадая на двухвходовом элементе И .144 переключают К% -триггер 12 в единичное состояние, кот{. рое через трехвхрдовый элемент ИЛИ-НЕ 7,RS-rpmTep 1О и двухвходовый элемент ИЛИ 15 включает ток цифро-аналогового преобразователя 19. Тогда ток 3 S 3 SО переключает компаратор 8 в единичное состояние. Еднчиные сигналы двухвходового элемента ИЛИ 16, пря MWO выхода кампаратбра8, инверсного вы хода компаратора 9, трехвходового элемента ИЛИ-НЕ 7 второго разряда запуркаюг очередной второй разряд прообразоватепя. Нулевой сигиап на пшне 18 я&пяегся кодовым сигналом. Таким образом, в обоих случаях поспе усгановления кода первого разряда в момент fej осуществляется запуск второго разряда преобразователя, ъ результате которого TIS-триггер 1О переключается в единичное состояние. Единичный сигнал двухвходового элемента ИЛИ 15 включает эталонный ток З-э цифро-аналогового преобразователя 19, а нулевой сигнал двухвходового элемента ИЛИ-НЕ 17 выключает эталонный ток Зд . При этом могут наблюдаться два случая: ток З, переключает компаратор Лэ 2 8 в нулевое состояние, а ток -3 переключает компаратор 9 в единичное состояние (см. фиг. 2); переключает компаратор 8 в нулевое состояние, а ток переключает компаратор 9 в единичное состояние. В обоих случаях единичные сигналы инверсных выходовкомпараторов 8 и 9, RS -триггера 10, совпадая аа (цвухвходовых элементах И 13 и 14,включают R b-триггера 11 и 12 в единичное состояние. Гдиничный сигнал двухвходового элемента ИЛИ 15 и нулевой сигнал двухвходового элемента ИЛИ-НЕ 17 сохраняют включенным эталонный ток.Здд цифро-аналвговсяО преобразователя 19 и выключенным эталонный ток Зэл цифроаналогового преобразователя 20. Нулевые сигналы прямого выхода компаратора 8 и инверсного выхода компаратора 9 запрещают запуск очередного разряда преобразователя. Единичный сигнап на шине 18 второго разряда является кодовым. Процесс формирования кодового сигнала второго (разряда преобразователя характерен для )любого разряда, в котором произошло уравновешивание входного сигнала эталонным. Фор м у ла изобретение Асинхронный аналог ци4фовой преобразователь поразрядного кодирования, ct держащий два компаратора, вврвые входы которых подключены к выходамсоответствующих 1шфр - анапогсшых преобразователей и через резисторы - к шине входного сигнала, а вторые входы - к шине земпя, отличающийся тем, что, с «елью получения сочетания максимально достижимой точности и быстродействия, в него введен регистр поразряд иого уравновешивания, каждый разряд которого включает три Т %-триггера, трея входовый элемент ИЛИ-НЁ, четырехвходо

вый элемент И, два двухвходовых элемента И, два двухахрдовых эпеменга ИЛИ, двухвходоврй эпеменг ИЛИ-НЕ, причем

S -вход первого К%-триггера соединен с выходом чегырехвходрвого эпеменга И, первый Ежш которого соединен с прямым выходом первого компаратора, второй вход - с шнной сигнала запуска,, третий вход - с инверсным выходом, второго компаратора, а четвертый вход соединен с ив версным выходом трехвхвдового эпемента

ИЛИ-НЕ 1 рямой оыход которого соединен с .1 -входом первого Я. -триггера, первый вход трехвходового эпемента соединен с первыми входами, двухвходовых апементов ИЛИ, прямым Еыходом второго i l-триггера и шиной выходных кодов, второй вход соединен с /Т1-входами второго и третьего US-триг геров и (ШИНОЙ сигнала сброса, а третий вход соединен с вторым входсяу двухвходовых элементов ИЛИ Ш1И-НЕ и прямым выходом третьего/RS-триггера, gi-входы второго и третьего Я§ -триггеров подкшочены к первого и второго двух18

входовых эпементов И, первые входы которых соединены со вторым входом первсь го двухвходовмо эггемента , ИЛИ, пе|эБым входом двухвходового эпемента ИЛИ-НЕ и прямым выходом первого RS-триггера, а вторые входы которых соединены с прямым и инверсным выходами второго и первого компаратора соответственно, выходы первого двухвходового элемента ИЛИ и двухвходового элемента ИЛИ-НЕ соединены с входами первого и второго цифроаналоговых пресЛрааователей соответственно, а выход второго двухвходового элемента ИЛИ подкгаючен к шине сигнала запуска очередного разряда.

Источники информации, принятые во внимание при экспертизе:

1в Труды УральсксяО политехническороинсгитута, 1970, сб. 182, с. 133138, рис. 3.

Вх. сигнал 1 ЦАП

ИМ

К-дыкод 8 К- Ьыхо в

К-вихо, 9 K-6t,iwd 9

Авторы

Даты

1978-07-25—Публикация

1976-01-16—Подача