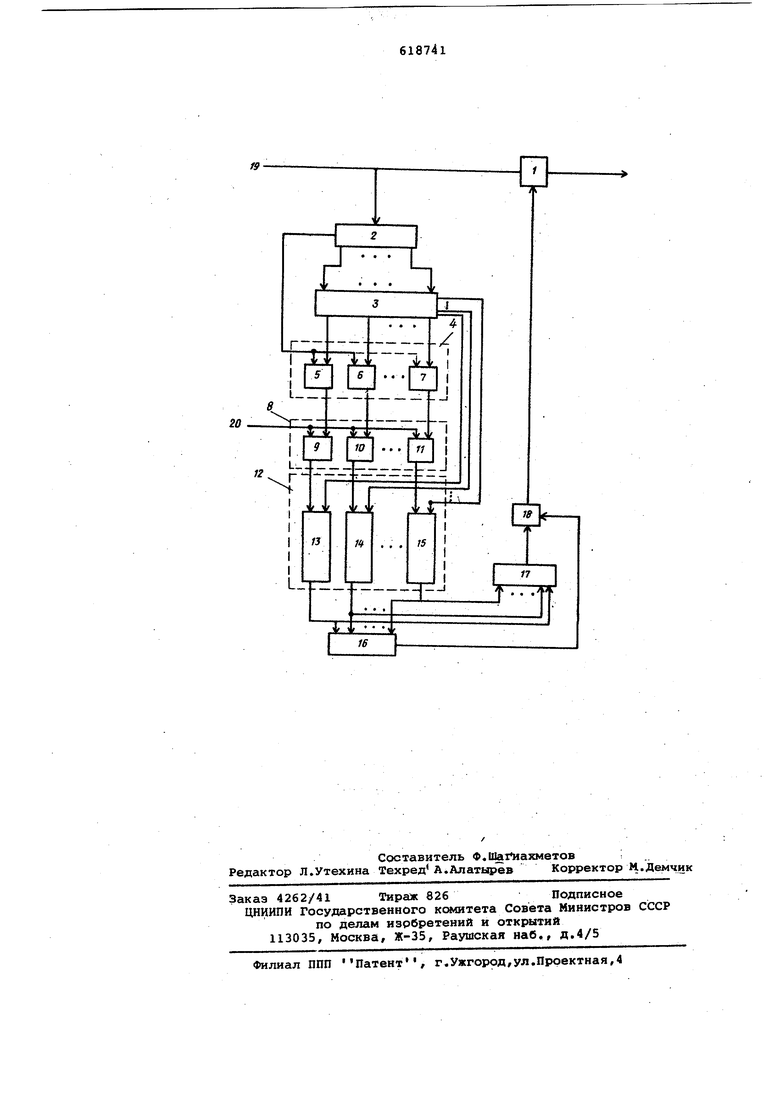

(54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ Устройство для Защиты памяти содержит первый коммутатор 1/ дешифратор 2, второй коммутатор 3, группу 4 триггеров 5-7, группу 8 элементов И 9-11/ . группу 12 регистров сдвига 13-15, датчик времени 16, элемент ИЛИ 17, элемент И 18. Устройство у ботает следующим о0разс 4, В начгшьном состоянии устройство подготавливаетсяк работе. Прк этом на адресный.вход 19 устройства пода ются коды адресов .Ячеек, которые нео6ходим& защищать, а на настроечный вход 20- число 1шпульсрв, равное числу допудтимых обращений к данной ячейке. Код ячейки адреса через дешифратор 2 и коммутатор 3 поступает на единичный вход соответствующего триггера, группы 4, при этом соответс твующий триггер {5г7) выдает сигнал на вход группы 8 элементов И, а на второй вход соответствующего элемента И поступают импульсы со входа 20 устройства, которые проходят через откЕжлтый элемент И и записываются в сортветствунедем регистре сдвига груп пы 12 регистров сдвига. При поступлении следующего кода адреса ячейки дешифратор 2 подает на нулевые входы триггеров 5-7 группы 4 сигнал, по которому все триггеры устанавливаютс в нулевое состояние. Затем цикл работы повторяется. Адрес запрашиваемой ячейки поступает со входа 19 устройства на первый вход коммутатора 1 и на вход дешифратора 2. На соответствующем выходе дешифратора 2 появляется сиг--, нал, который поступает через коммутатор 3 на управляющий вход соответствующего регистра сдвига группы 12. ЕСЛИ в этом регистре записано некоторое число разрешенных обращений, то на его . выходе появляется сигнал, а число разрешенных обрайений. к ячей ке уменьшается на единицу. Сигналы с выходов группы 12 регистров сдвига поступают через элемент ИЛИ 17-На вход элемент И 18 и на вход датчика 16 времени,который вырабатывает временной интервал,в течение которого разрешается допуск к запрашиваемой ячейке памяти.Этот сигнал через открытый «лем нт ИЛИ 17 поступает на управляющий вход коммутатора 1 и раз решает обращение к ячейке в течение сформированного интервала времени. Если в регистре не записано число разрешенных обращений,т.е.допускак ячейке памяти нет, то сигнал на вы 14 ходе регистра не формируется, и допуск к ячейке запрещается. Таким образом предложенное устройство позволяет повысить по сравнению с известные устройством надежность защиты ячеек памяти так как оно позволяет ограничивать число допустимых обращений к ячейке. Если по ходу npprpeUkttttJ произошло непредусмотренное обращение к закрытой ячейке, то это обращение учитывается в дальнейшем при выполнении программы и-при последнем предусмотренном обращении к этой ячейке разрешения на допуск к ней не будет дано. Формула изобретения Устройство для защиты памяти, содержащее первый коммутатор, выход которого является выходом устройства, дешиф атор, группа выходов,которого соединена со входф и второго коммутатора, первая группа, выходов которого соединена с единичными входами триггеров группы триггеров, группу элементов И, первые входы которых соединены с выходами соответствующих хр иггеров группы триггеров, элемент И, первый и второй входа которого соединены соответственно с выходами элемента ИЛИ и датчика времени, причем адресный вход устройства соединен со входе дешифратора и кодовым входом первого кЪммутатора, управляющий вход которого соедин,ен с выходом элемента И, о т л и ч а ю щ е ес я тем, чТо, с целью повышения надежности,оно содержит группу регистров сдвига; причем информационные входы регистров сдвига соединены с выходами соответствующих элементов И группы элементов И, управляющие входы регистров сдвига соединены, с соответствующими выходами второй группы выходов второго коммутатора; .выход дешифратора соединен С-: нулевыми входами триггеров группы триггеров; выходы регистров сдвига соединены с соответствующими входами элемента ИЛИ и датчика времени, а вто1ше входы элементов И группы элементов И соединены с настроечным входом устройства. Источники информации, принятые во внимание при экспертизе; 1.Авторское свидетельство СССР №306463, кл. Q06 Г 11/00, 1973. 2.Заявка 2361297/24,кл. :eil С 29/00,23.11.76, по которой принято решение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты памяти | 1983 |

|

SU1113854A1 |

| Адаптивное устройство для защиты памяти | 1983 |

|

SU1103291A1 |

| Устройство для защиты памяти | 1988 |

|

SU1508216A1 |

| Устройство для идентификации магнитных карт | 1981 |

|

SU1005098A2 |

| Устройство для защиты блоков памяти | 1978 |

|

SU752498A1 |

| Устройство для защиты памяти | 1979 |

|

SU841065A2 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1550523A1 |

| Устройство для защиты памяти | 1977 |

|

SU680060A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство для автоматического проектирования сборки печатной платы | 1983 |

|

SU1125630A1 |

Авторы

Даты

1978-08-05—Публикация

1977-02-01—Подача