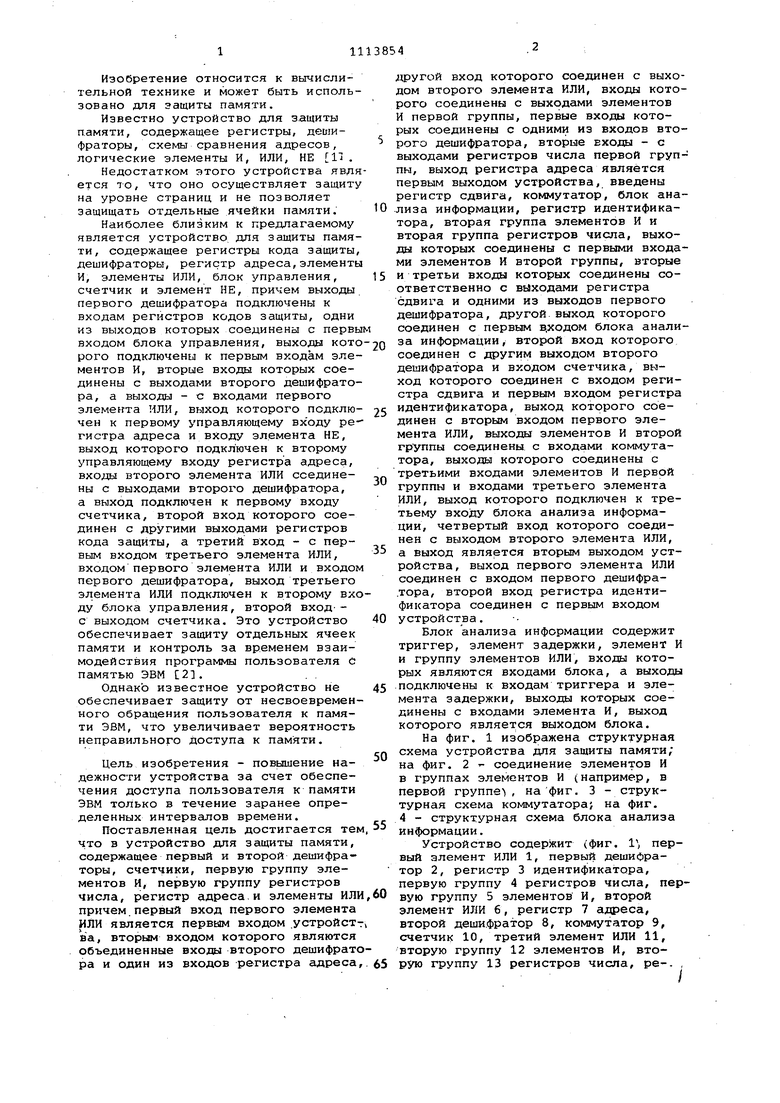

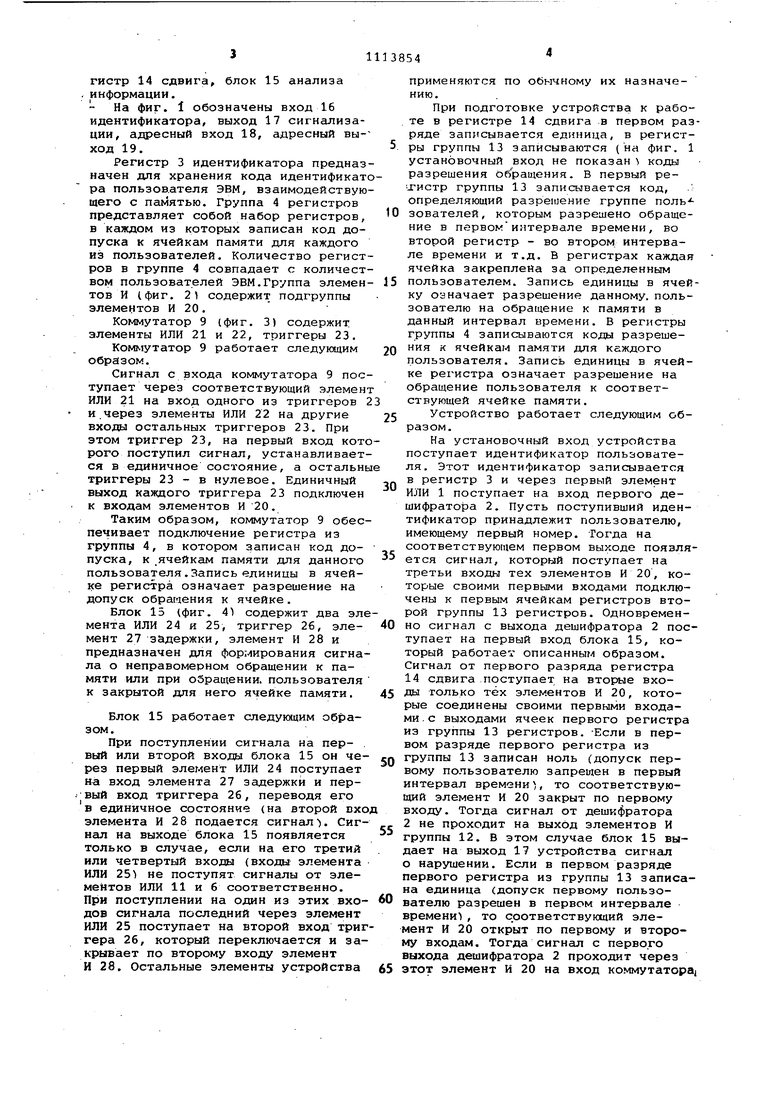

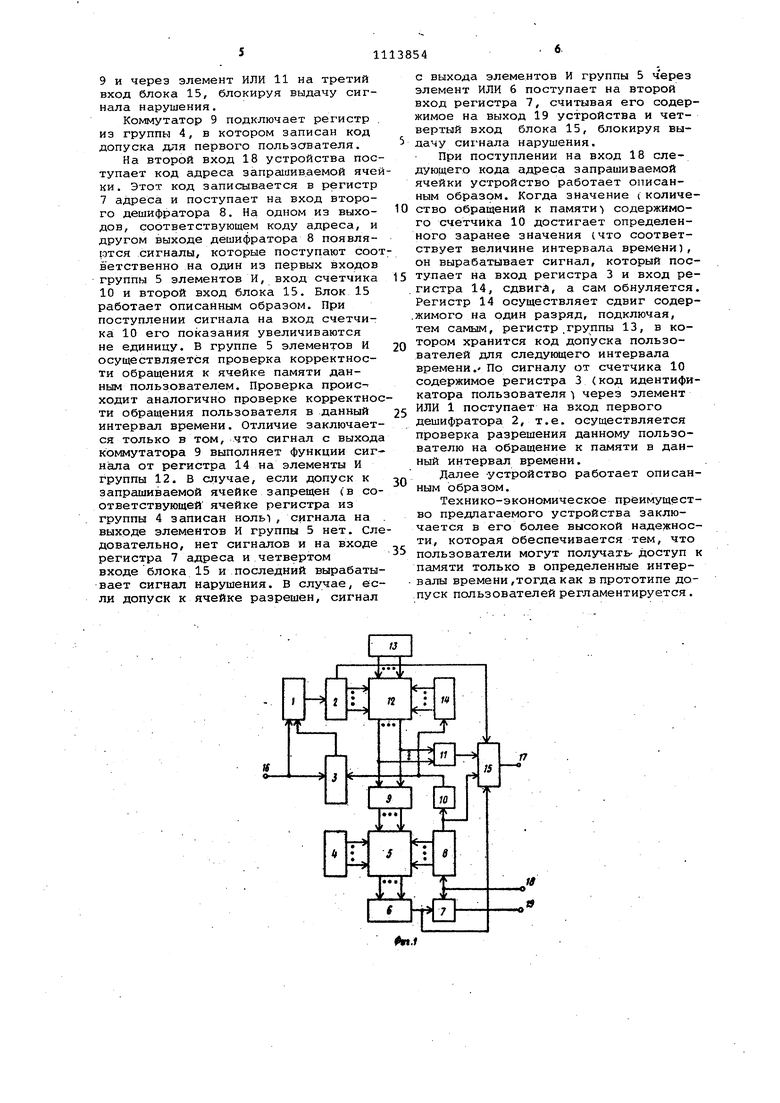

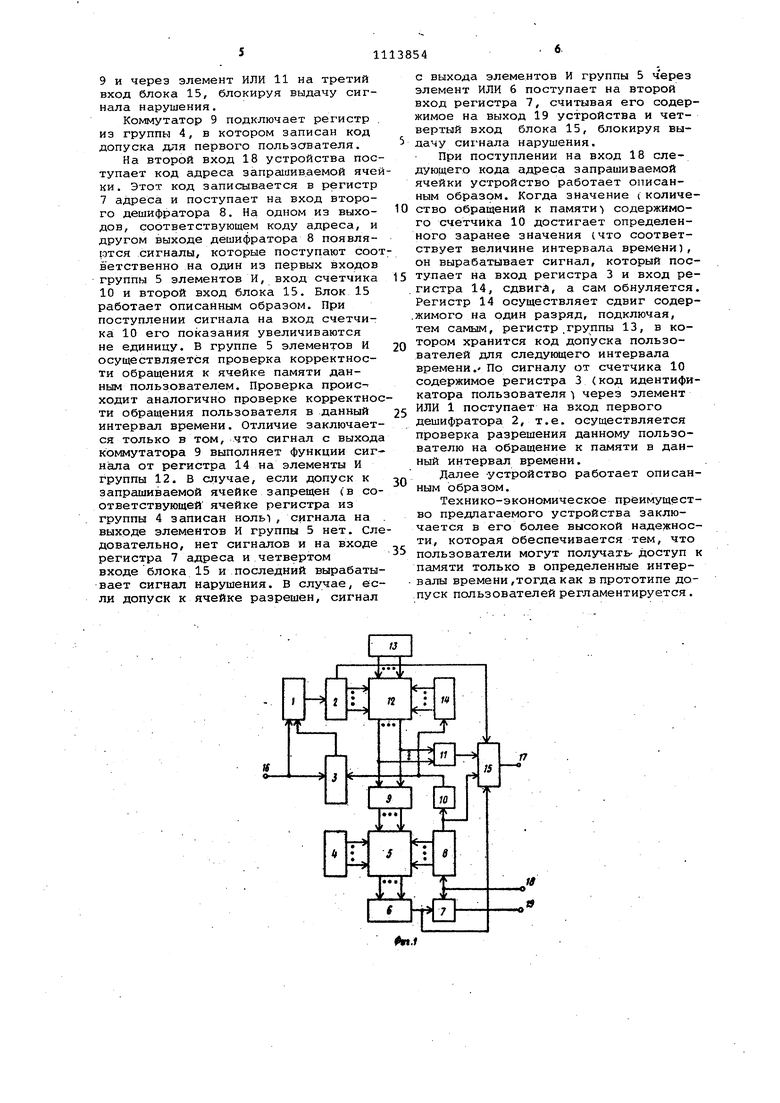

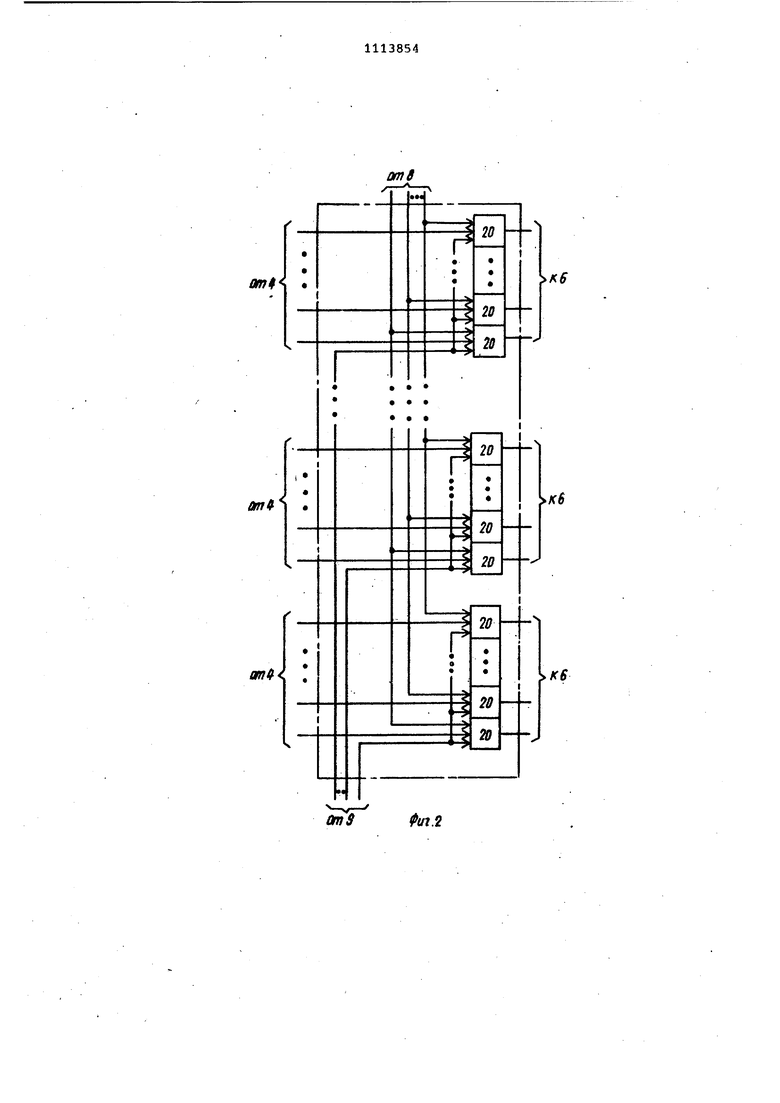

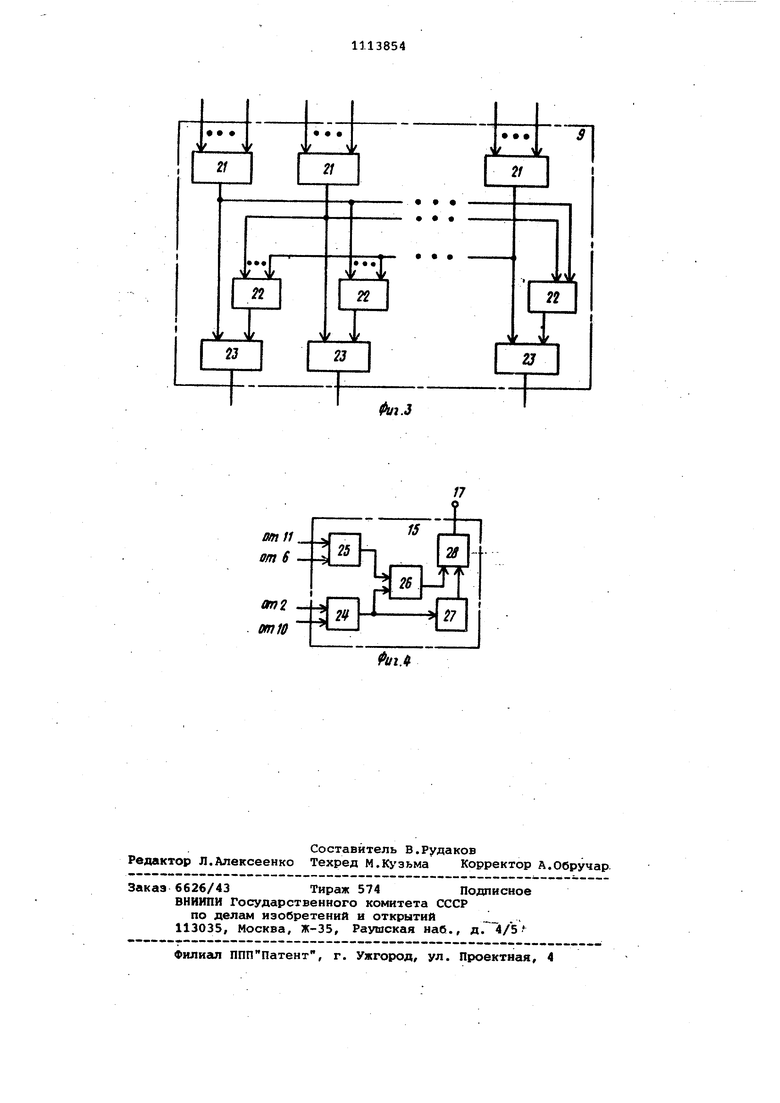

Изобретение относится к вычислительной технике и может быть исполь зовано для защиты памяти. Известно устройство для защиты памяти, содержащее регистры, дешифраторы, схемы сравнения адресов, логические элементы И, ИЛИ, НЕ И . Недостатком этого устройства явл ется 7о, что оно осуществляет защиту на уровне страниц и не позволяет защищать отдельные ячейки памяти. Наиболее близким к предлагаемому является устройство для защиты памя ти, содержащее регистры кода защиты дешифраторы, регистр адреса,элементы И, элементы ИЛИ, блок управления, счетчик и элемент НЕ, причем выходы первого дешифратора подключены к входам регистров кодов защиты, одни из выходов которых соединены с первы входом блока управления, выходы кото рого подключены к первым входам элементов И, вторые входы которых соединены с выходами второго дешифратора, а выходы - с входами первого элемента ИЛИ, выход которого подклю чей к первому управляющему входу ре гистра адреса и входу элемента НЕ, выход которого подключен к второму управляющему входу регистра адреса, входы второго элемента ИЛИ соединены с выходами второго дешифратора, а выход подключен к первому входу счетчика, второй вход которого соединен с другими выходами регистров кода защиты, а третий вход - с первым входом третьего элемента ИЛИ, входом первого элемента ИЛИ и входом первого дешифратора, выход третьего элемента ИЛИ подключен к второму вхо ду блока управления, второй вход-с выходом счетчика. Это устройство обеспечивает защиту отдельных ячеек памяти и контроль за временем взаимодействия программы пользователя С памятью ЭВМ 21. Однако известное устройство не обеспечивает защиту от несвоевременного обращения пользователя к памяти ЭВМ, что увеличивает вероятность неправильного доступа к памяти. Цель изобретения - повышение надежности устройства за счет обеспечения доступа пользователя к памяти ЭВМ только в течение заранее определенных интервалов времени. Поставленная цель достигается тем что в устройство для защиты памяти, содержащее первый и второй дешифраторы, счетчики, первую группу элементов И, первую группу регистров числа, регистр адреса и элементы ИЛИ причем первый вход первого элемента ИЛИ является первым входом устройстт ва, вторым входом которого являются объединенные входы второго дешифрато ра и один из входов регистра адреса другой вход которого соединен с выходом второго элемента ИЛИ, входы которого соединены с выходами элементов И первой группы, первые входы которых соединены с одними из входов второго дешифратора, вторые входы - с выходами регистров числа первой группы, выход регистра адреса является первым выходом устройства, введены регистр сдвига, коммутатор, блок анализа информации, регистр идентификатора, вторая группа элементов И и вторая группа регистров числа, выходы которых соединены с первыми входами элементов И второй группы, вторые и третьи входы которых соединены соответственно с выходами регистра сдвига и одними из выходов первого дешифратора, другой выход которого соединен с первым цходом блока анализа информации, второй вход которого соединен с другим выходом второго дешифратора и входом счетчика, выход которого соединен с входом регистра сдвига и первым входом регистра идентификатора, выход которого соединен с вторым входом первого элемента ИЛИ, выходы элементов И второй группы соединены с входами коммутатора, выходы которого соединены с третьими входами элементов И первой группы и входами третьего элемента ИЛИ, выход которого подключен к третьему входу блока анализа информации, четвертый вход которого соединен с выходом второго элемента ИЛИ, а выход является вторым выходом устройства, выход первого элемента ИЛИ соединен с входом первого дешифра.тора, второй вход регистра идентификатора соединен с первым входом устройства. Блок анализа информации содержит триггер, элемент задержки, элемент И и группу элементов ИЛИ, входы которых являются входами блока, а выходы подключены к входам триггера и элемента задержки, выходы которых соединены с входами элемента И, выход которого является выходом блока. На фиг. 1 изображена структурная схема устройства для защиты памяти; на фиг. 2 т- соединение элементов И в группах элементов И (например, в первой группе , на фиг. 3 - структурная схема коммутатора} на фиг. 4 - структурная схема блока ангшиза информации. Устройство содержит (фиг. 1, первый элемент ИЛИ 1, первый дешифратор 2, регистр 3 идентификатора, первую группу 4 регистров числа, первую группу 5 элементов И, второй элемент ИЛИ б, регистр 7 адреса, второй дешифратор 8, коммутатор 9, счетчик 10, третий элемент ИЛИ 11, вторую группу 12 элементов И, вторую группу 13 регистров числа, ре-. , гистр 14 сдвига, блок 15 анализа . информации. - На фиг. 1 обозначены вход 16 идентификатора, выход 17 сигнализации, адресный вход 18, адресный выход 19. Регистр 3 идентификатора предназ начен для хранения кода идентификат ра пользов.ателя ЭВМ, взаимодействую щего с памятью. Группа 4 регистров представляет собой набор регистров, в каждом из которых записан код допуска к ячейкам памяти для каждого из пользователей. Количество регист ров в группе 4 совпадает с количест вом пользователей ЭВМ.Группа элемен тов И (фиг. 21 содержит подгруппы элементов И 20. Коммутатор 9 (фиг. 3) содержит элементы ИЛИ 21 и 22, триггеры 23. Коммутатор 9 работает следующим образом. Сигнал с входа коммутатора 9 пос тупает через соответствующий элемен ИЛИ 21 на вход одного из триггеров и.через элементы ИЛИ 22 на другие входы остальных триггеров 23. При этом триггер 23, на первый вход кото рого поступил сигнал, устанавливает ся в единичное состояние, а остальны триггеры 23 - в нулевое. Единичный выход каждого триггера 23 подключен к входам элементов И 20. Таким образом, коммутатор 9 обес печивает подключение регистра из группы 4, в котором записан код допуска, к ячейкам памяти для данного пользователя.Запись единицы в ячейке регистра означает разрешение на допуск обращения к ячейке. Блок 15 (фиг. 41 содержит два эле мента ИЛИ 24 и 25, триггер 26, элемент 27 задержки, элемент И 28 и предназначен для формирования сигнала о неправомерном обращении к памяти или при обращении, пользователя к закрытой для него ячейке памяти. Блок 15 работает следующим образом . При поступлении сигнала на первый или второй входы блока 15 он через первый элемент ИЛИ 24 поступает на вход элемента 27 задержки и первый вход триггера 26, переводя его в единичное состояние (на второй вхо элемента И 28 подается сигнал). Сигнал на выходе блока 15 появляется только в случае, если на его третий или четвертый входы (входы элемента ИЛИ 251 не поступят сигналы от элементов ИЛИ 11 и 6 соответственно. При поступлении на один из этих входов сигнала последний через элемент ИЛИ 25 поступает на второй вход триг гера 26, который переключается и закрывает по второму входу элемент И 28. Остальные элементы устройства применяются по обычному их назначению. При подготовке устройства к работе в регистре 14 сдвига в первом разряде записывается единица, в регистры группы 13 записываются (на фиг. 1 установочный вход не показан коды разрешения Обращения. В первый ре хистр группы 13 записывается код, определяющий разрешение группе поль- зователей, которым разрешено обращение в первоминтервале времени, во второй регистр - во втором интервале времени и т.д. В регистрах каждая ячейка закреплена за определенным пользователем. Запись единицы в ячейку означает разрешение данному, пользователю на обращение к памяти в данный интервал времени. В регистры группы 4 записываются коды разрешения к ячейкам памяти для каждого пользователя. Запись единицы в ячейке регистра означает разрешение на обращение пользователя к соответствующей ячейке памяти. Устройство работает следующим образом. На установочный вход устройства поступает идентификатор пользователя. Этот идентификатор записывается в регистр 3 и через первый элемент ИЛИ 1 поступает на вход первого дешифратора 2. Пусть поступивший идентификатор принадлежит пользователю, имеющему первый номер. Тогда на соответствующем первом выходе появляется сигнал, который поступает на третьи входы тех элементов И 20, которые своими первыми входами подключены к первым ячейкам регистров второй группы 13 регистров. Одновременно сигнал с выхода дешифратора 2 поступает на первый вход блока 15, который работает описанным образом. Сигнал от первого разряда регистра 14 сдвига поступает на вторые входы только тех элементов И 20, которые соединены своими первыми входами, с выходами ячеек первого регистра из группы 13 регистров. -Если в первом разряде первого регистра из группы 13 записан ноль (допуск первому пользователю запрещен в первый интервал времени), то соответствующий элемент И 20 закрыт по первому входу. Тогда сигнал от дешифратора 2 не проходит на выход элементов И группы 12. В этом случае блок 15 выдает на выход 17 устройства сигнал о нарушении. Если в первом разряде первого регистра из группы 13 записана единица (допуск первому пользователю разрешен в первом интервале времени, то соответствующий элемент И 20 открыт по первому и второму входам. Тогда сигнал с первого выхода дешифратора 2 проходит через этот элемент И 20 на вход коммутатора 9и через элемент ИЛИ 11 на третий вход блока 15, блокируя выдачу сигнала нарушения. Коммутатор 9 подключает регистр из группы 4, в котором записан код допуска для первого пользователя. На второй вход 18 устройства пос тупает код адреса запрашиваемой яче ки. Этот код записывается в регистр 7 адреса и поступает на вход второго дешифратора 8. На одном из выхоДОН, соответствующем коду адреса, и другом выходе дешифратора 8 появляются сигналы, которые поступают соо ветственно на один из первых входов группы 5 элементов И, вход счетчика 10и второй вход блока 15. Блок 15 работает описанным образом. При поступлении сигнала на вход счетчика 10 его показания увеличиваются не единицу. В группе 5 элементов И осуществляется проверка корректности обращения к ячейке памяти данHfcGM пользователем. Проверка проис ходит аналогично проверке корректнос ти обращения пользователя в данный интервал времени. Отличие заключается только в том, что сигнал с выхода коммутатора 9 выполняет функции сигнала от регистра 14 на элементы И группы 12. В случае, если допуск к запрашиваемой ячейке запрещен (в соответствующей ячейке регистра из группы 4 записан нольч, сигнала на выходе элементов И группы 5 нет. Сле довательно, нет сигналов и на входе регистра 7 адреса и четвертом входе блока 15 и последний вырабатывает сигнал нарушения, в случае, если допуск к ячейке разрешен, сигнал с выхода элементов И группы 5 через элемент ИЛИ 6 поступает на второй вход регистра 7, считывая его содержимое на выход 19 устройства и четвертый вход блока 15, блокируя выдачу сихнала нарушения. При поступлении на вход 18 следующего кода адреса запрашиваемой ячейки устройство работает описанным образом. Когда значение с количество обращений к памяти) содержимого счетчика 10 достигает определенного заранее значения (что соответствует величине интервала времени), он вырабатывает сигнал, который поступает на вход регистра 3 и вход регистра 14, сдвига, а сам обнуляется. Регистр 14 осуществляет сдвиг содержимого на один разряд, подключая, тем самым, регистр ,группы 13, в котором хранится код допуска пользователей для следующего интервала времени.По сигналу от счетчика 10 содержимое регистра 3 (код идентификатора пользователя i через элемент ИЛИ 1 поступает на вход первого дешифратора 2, т.е. осуществляется проверка разрешения данному пользователю на обращение к памяти в данный интервсш времени. Далее -устройство работает описанным образом. Технико-экономическое преимущество предлагаемого устройства заключается в его более высокой надежности, которая обеспечивается тем, что пользователи могут получать- доступ к памяти только в определенные интервалы времени ,тогда как в прототипе допуск пользователей регламентируется.

Ofn$

Af

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты памяти | 1988 |

|

SU1508216A1 |

| Устройство для идентификации магнитных карт | 1981 |

|

SU1005098A2 |

| Устройство для защиты памяти | 1977 |

|

SU618741A1 |

| Адаптивное устройство для защиты памяти | 1983 |

|

SU1103291A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для ввода информации | 1983 |

|

SU1149236A1 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ | 1990 |

|

RU2020564C1 |

| УСТРОЙСТВО ДЛЯ РАЗГРАНИЧЕНИЯ ДОСТУПА ПОЛЬЗОВАТЕЛЕЙ К РАЗДЕЛАМ ТЕКСТОВЫХ ДОКУМЕНТОВ | 2001 |

|

RU2239866C2 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

1. УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ, содержащее первый и второй дешифраторы, счетчики, первую группу элементов И, первую группу регистров числа, регистр адреса и элементы ИЛИ, причем первый вход первого элемента ИЛИ является первым входом устройства, вторым входом которого являются объединенные входы второго дешифратора и один из входов регистра адреса, другой вход которого соединен с выходом второго элемента ИЛИ, входы которого соединены с выходами элементов И первой группы, первые входы которых соединены с одним из выходов второго дешифратора, вторые входы - с выходами регистров числа первой группы, выход регистра адреса является первым выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены регистр сдвига, коммутатор, блок анализа информации, регистр идентификатора, вторая группа элементов И и вторая группа регистров числа, выходы которых соединены с первыми входами элементов И второй группы, вторые и третьи входы которых соединены соответствен,но с выходами регистра сдвига и одними из выходов первого д ешифратора, другой выход которого соединен с первым входом блока анализа информации, второй вход Которого, соединен с другим выходом второго дешифратора и входом счетчика, выход которого соединен с входом регистра сдвига и первым входом регистра идентификатора, выход которого соединен с вторым входом первого элемента ИЛИ, выходы элементов И второй группы соединены с входами коммутатора, выходы которого соедиi нены с третьими входами элементов И первой группы и входами третьего (Л элемента ИЛИ, выход которого подключен к третьему входу блока анализа информации, четвертый вход которого соединен с выходом второго элемента ИЛИ, а выход является вторым выходом устройства, выход первого элемента ИЛИ соединен с входом первого дешифратора, второй вход регистра идентификатора соединен с первым входом устройства. 2. Устройство по п. 1, отлиСАР чающееся тем, что блок аналиСХ) за информации содержит триг1%р, элесл мент задержки, элемент И и группу элементов ИЛИ, входы которых являются входами блока, а выходы подключены к входам триггера и элемента задержки, выходы которых соединены с входами элемента И, выход которого является выходом блока.

ап9

aff

OmS

/f6

KB

uj.2

omil.

от 6

ап2 отю

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для ЗАЩИТЫ ПАМЯТИ | 0 |

|

SU306463A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР 913456, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-09-15—Публикация

1983-05-20—Подача