го

(Л

, 150

Изобретение относится к вычислительной технике и. может быть использовано для защиты ячеек памяти от несанкционированного обращения к ним.

Цель изобретения - расширение области применения.устройства за счет обеспечения возможности управления количеством видов размещенных операций с памятью для программы пользо- вателя,

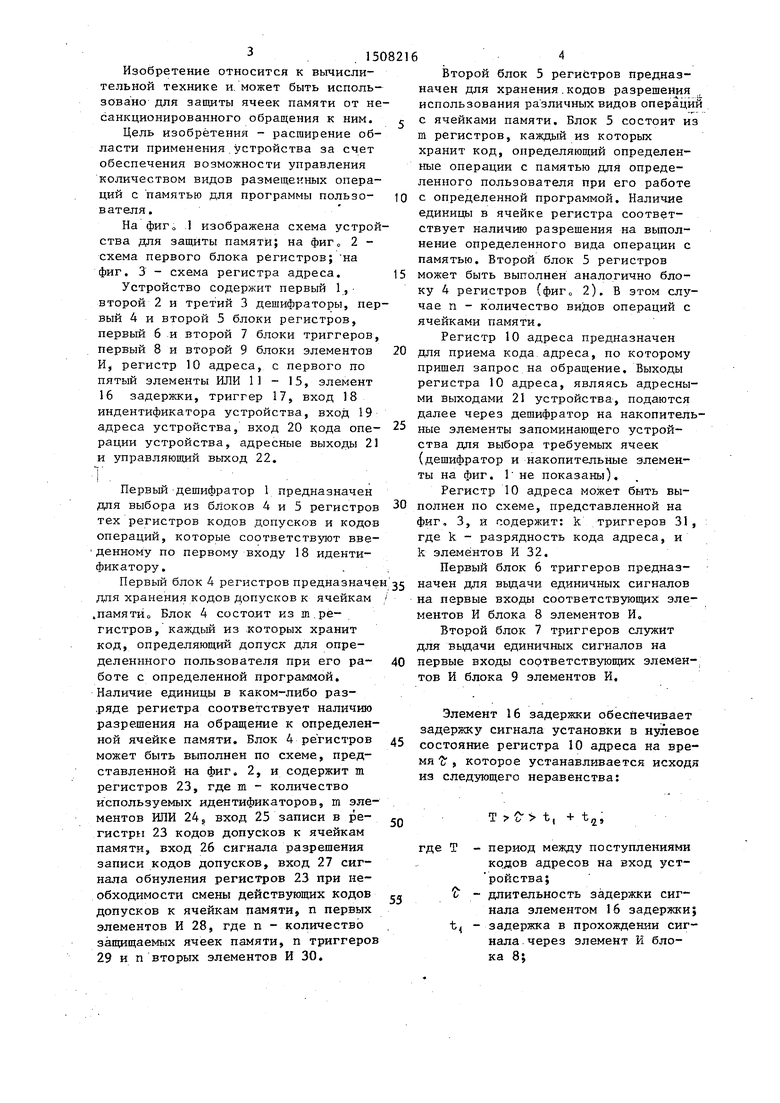

На фиг о 1 изображена схема устройства для защиты памяти; на фиг„ 2 - схема первого блока регистров; на фиг. 3 - схема регистра адреса.

Устройство содержит первый 1, второй 2 и третий 3 дешифраторы, первый 4 и второй 5 блоки регистров, первый 6 и второй 7 блоки триггеров, первый 8 и второй 9 блоки элементов И, регистр 10 адреса, с первого по пятый элементы ИЛИ 11 - 15, элемент 16 задержки, триггер 17, вход 18 индентификатора устройства, вход 19 адреса устройства, вход 20 кода one- рации устройства, адресные выходы 21 и управляющий выход 22.

Т.

Первый дешифратор 1 предназначен для выбора из блоков 4 и 5 регистров тех регистров кодов допусков и кодов операций, которые соответствуют введенному по первому входу 18 идентификатору..

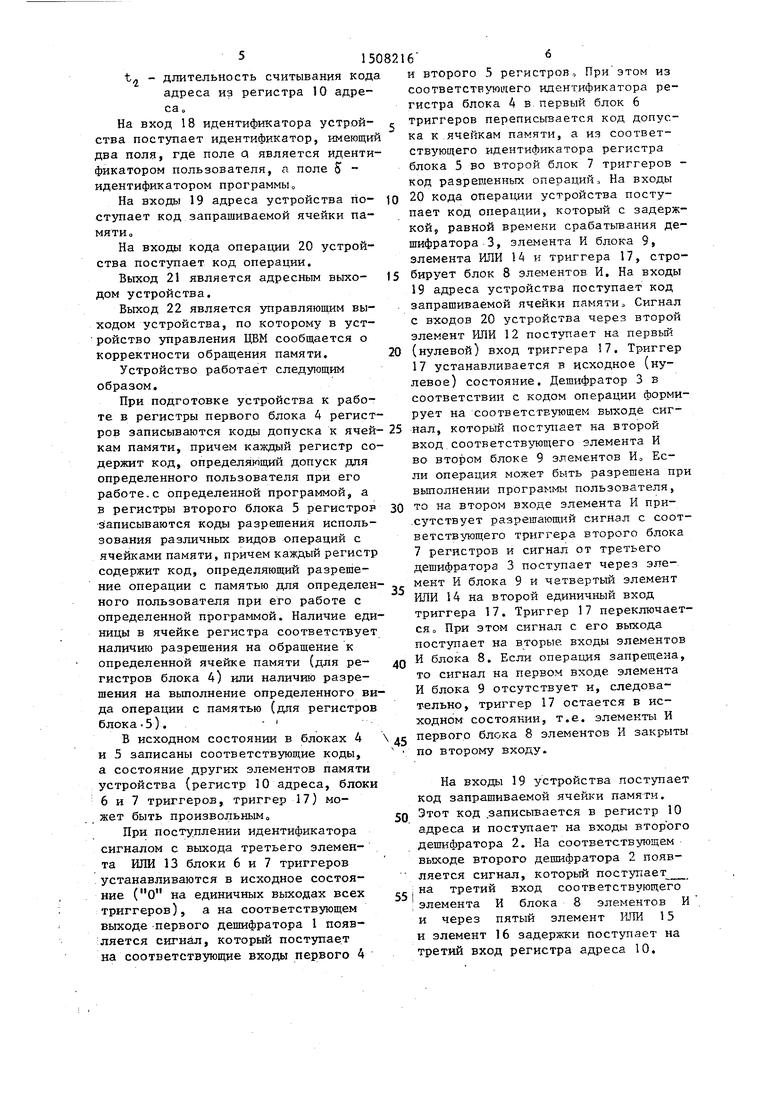

Первый блок 4 регистров предназначе для хранения кодов допусков к ячейкам .памятио Блок 4 состолт из т.регистров , каждый из которых хранит код, определяющий допуск для опре- деленнного пользователя при его ра- боте с определенной программой. Наличие единицы в каком-либо разряде регистра соответствует наличию разрешения на обращение к определенной ячейке памяти. Блок 4 регистров может быть выполнен по схеме, представленной на фиг. 2, и содержит m регистров 23, где m - количество используемых идентификаторов, m элементов ИЛИ 24, вход 25 записи в ре- гистрн 23 кодов допусков к ячейкам памяти, вход 26 сигнала разрешения записи кодов допусков, вход 27 сигнала обнуления регистров 23 при необходимости смены действующих кодов допусков к ячейкам памяти, п первых элементов И 28, где п - количество защищаемых ячеек памяти, п триггеров 29 к п вторых элементов И 30.

4

Второй блок 5 регистров предназначен для хранения.кодов разрешения использования различных видов операций с ячейками памяти. Блок 5 состоит из m регистров, каждый из которых хранит код, определяющий определенные операции с памятью для определенного пользователя при его работе с определенной программой. Наличие единицы в ячейке регистра соответствует наличию разрешения на выполнение определенного вида операции с памятью. Второй блок 5 регистров может быть выполнен аналогично блоку 4 регистров {фиго 2). В этом случае п - количество видов операций с ячейками памяти.

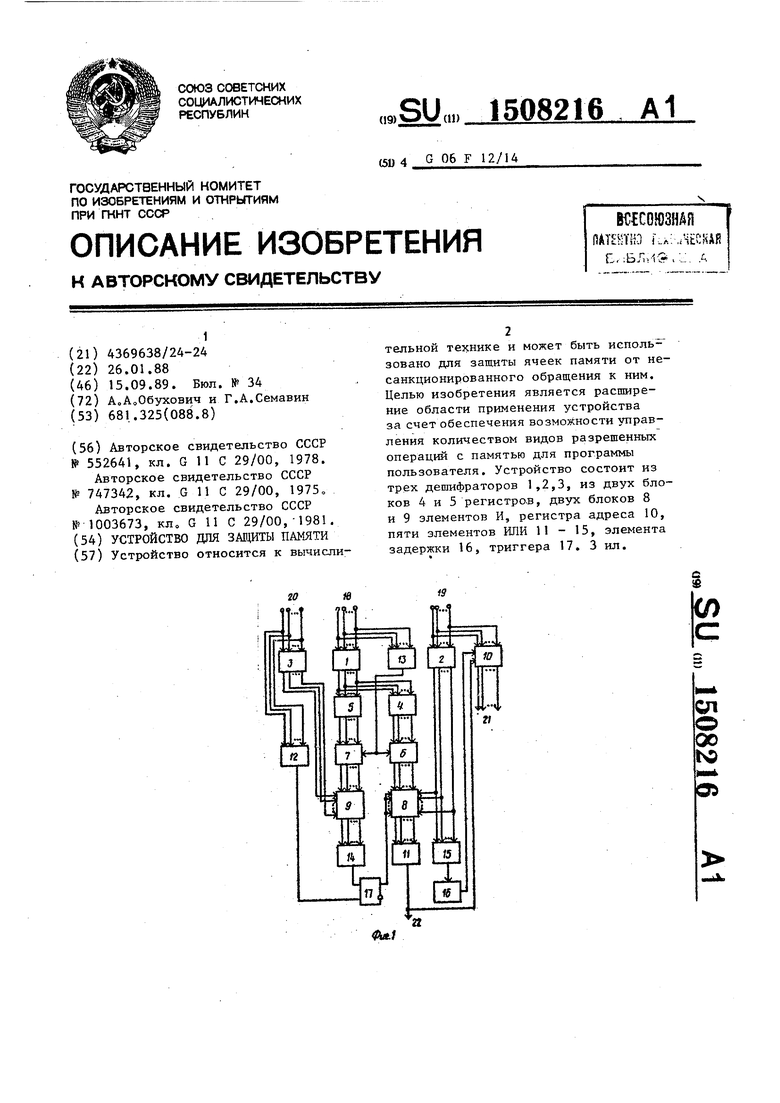

Регистр 10 адреса предназначен для приема кода адреса, по которому пришел запрос на обращение. Выходы регистра 10 адреса, являясь адресными выходами 21 устройства, подаются далее через дешифратор на накопительные элементы запоминающего устройства для выбора требуемых ячеек {дешифратор и накопительные элементы на фиг. 1 не показаны).

Регистр 10 адреса может быть выполнен по схеме, представленной на фиг, 3, и содержит: k триггеров 31, где k - разрядность кода адреса, и k элементов И 32.

Первый блок 6 триггеров предназначен для вьщачи единичных сигналов на первые входы соответствзшщих элементов И блока 8 элементов И,

Второй блок 7 триггеров служит для вьщачи единичных сигналов на первые входы соответствуюш гх элементов И блока 9 элементов И.

Элемент 16 задержки обеспечивает задержку сигнала установки в нулевое состояние регистра 10 адреса на время & , которое устанавливается исходя из следующего неравенства:

Т € t, + t

2

де Т - период между поступлениями кодов адресов на вход уст- ройства;

длительность задержки сигнала элементом 16 задержки; задержка в прохождении сигнала .через элемент И блока 8;

г

t, 515

t - длительность считывания кода адреса из регистра 10 адреса

На вход 18 идентификатора устрой- ства поступает идентификатор, г меющий два поля, где поле а является идентификатором пользователя, а поле 5 - идентификатором программы„

На входы 19 адреса устройства по- ступает код запрашиваемой ячейки памяти о

На входы кода операции 20 устройства поступает код операции.

Выход 21 является адресным выхо- дом устройства.

Выход 22 является управляющим выходом устройства, по которому в устройство управления ЦВМ сообщается о корректности обращения памяти.

Устройство работает следующим образом.

При подготовке устройства к работе в регистры первого блока 4 регистров записываются коды допуска к ячей- кам памяти, причем каждый регистр содержит код, определяющий допуск для определенного пользователя при его работе.с определенной программой, а в регистры второго блока 5 регистров записываются коды разрешения использования различных видов операций с ячейками памяти, причем каждый регистр содержит код, определяющий разрешение операции с памятью для определенного пользователя при его работе с определенной программой. Наличие единицы в ячейке регистра соответствует наличию разрешения на обращение к определенной ячейке памяти (для ре- гистров блока А) или наличию разрешения на вьтолнение определенного вида операции с памятью (для регистров блока -5).-

В исходном состоянии в блоках 4 и 5 записаны соответствующие коды, а состояние других элементов памяти устройства (регистр 10 адреса, блоки 6 и 7 триггеров, триггер 17) может быть произвольнымо

При поступлении идентификатора сигналом с выхода третьего элемента Ш1И 13 блоки 6 и 7 триггеров устанавливаются в исходное состояние (о на единичных выходах всех триггеров), а на соответствующем выходе -первого дешифратора 1 появ- :ляется сигнал, который поступает на соответствующие входы первого 4

5

0

5 0 О

5 0

5

5

6-6

и второго 5 регистров,. При этом из соответствующего идентификатора регистра блока 4 в,первый блок 6 триггеров переписывается код допуска к.ячейкам памяти, а из соответствующего идентификатора регистра блока 5 во второй блок 7 триггеров - код разрешенных операций. На входы 20 кода onepaiyiH устройства поступает код операции, который с задержкой, равной времени срабатывания дешифратора 3, элемента И блока 9, элемента ИЛИ 14 и триггера 17, стро- бирует блок 8 элементов И. На входы 19 адреса устройства поступает код запрашиваемой ячейки памяти Сигнал с входов 20 устройства через второй элемент ИЛИ 12 поступает на первый (нулевой) вход триггера 7. Триггер 17 устанавливается в исходное (нулевое) состояние. Дешифратор 3 в соответствии с кодом операции формирует на соответствующем выходе сигнал, который поступает на второй вход соответствующего элемента И во втором блоке 9 элементов Ио Если операция может быть разрешена при вьшолнении программы пользователя, то на втором входе элемента И при- .сутствует разрешающий сигнал с соответствующего триггера второго блока 7 регистров и сигнал от третьего дешифратора 3 поступает через элемент И блока 9 и четвертьй элемент ИЛИ 14 на второй единичный вход триггера 17. Триггер 17 переключается При этом сигнал с его выхода поступает на вторые входы элементов И блока 8. Если операция запрещена, то сигнал на первом входе элемента И блока 9 отсутствует и, следовательно, триггер 17 остается в исходном состоянии, т.е. элементы И первого блока 8 элементов И закрыты по второму входу.

На входы 19 устройства поступает код запрашиваемой ячейки памяти. Этот код .записывается в регистр 10 адреса и поступает на входы второго дешифратора 2. На соответствующем выходе второго дешифратора 2 появляется сигнал, который поступает

на третий вход соответствующего элемента И блока 8 элементов И и через пятый элемент 1-ШИ 15 и элемент 16 задержки поступает на третий вход регистра адреса 10.

/

Пятый элемент ИЛИ 15 и элемент 16 задержки предназначены для разнесения во времени процессов считывания кода адреса из регистра 10 адреса и стирания кода адреса в регистре 10 адреса, осуществляемого по завершени цикла анализа корректности (разрешено или запрещено) обращенр.я к памяти

Сигнал на выходе элемента И.из блока 8 элементов И появляется только при наличии разрешающих сигналов на его первом входе (сигнал разрешения на обращение к данной ячейке памяти для данного пользователя при его работе с данной программой от соответствующего триггера блока 6 триггеров) и втором входе (сигнал разрешения на выполнение операции данного вида при выполнении данной программы данного пользователя от триггера 17). Этот.сигнал через элемент ИЛИ 11 поступает на второй вход регистра 10 адреса, при этом считывается его содержимое на адресный выход 21 устройства и управляюш 1Й выход 22 устройства, сообщая устройству управления ЦВМ о корректности обращения к памяти. При невыполнении любого из двух условий (вид операции разрешен и допуск к ячейке памяти разрешен) сигнал на выходе первого блока 8 элементов И не появляется. Следовательно, на управляющем выходе устройства 22 сигнал не появляется и код адреса не считывается из регистра 10 адреса на адресный выход 21 устройства, а по сигналу от элемента 16 задержки этот код стирается из регистра 10 адреса. Tie о несанк- ционированное обращение к ячейке памяти предотвращается.

Формула изобретения

Устройство для защиты памяти, содержащее первьй блок регистров, первый блок триггеров, первый блок элементов И, первый элемент ИЛИ, триггер, регистр адреса, два дешифратора, причем входы первого дешифратора являются входами идентификатора устройства, а выходы соединены с информационными входами первого блока регистров, выходы данных первого .блока регистров соединены с соответствующими входами установки триг геров первого блока триггеров, пря8

Q з 0 5 0 Q

5

5

0

5

мые вькоды триггеров первого блока триггеров соединены с первыми входами первого блока элементов И, вторые входы которого соединены с прямым выходом триггера, третьи входы первого блока элементов И соединены с выходами второго дешифратора, входы которого соединены с информационными входами регистра адреса и являются адресными входами устройства, выход регистра адреса является ад-, ресным выходом устройства, выходы первого блока элементов И соединены с входами элемента ИЖ, выход которого соединен с входом разрешения выдачи адреса регистра адреса и является управляющим выходом устройства,отличающееся тем, что, с целью расширения области применения путем обеспечения возможности управления количеством видов разрешенных операций с памятью для программы пользователя, в него введены второй блок регистров, второй блок элементов И, второй блок триггеров, с второго по пятый элементы ИЛИ, элемент задержки и третий дешифратор, входы которого соединены с входами второго элемента ИЛИ и образуют вход задания кода операции устройства, информационные входы второго блока регистров соедрнены с соответствующими выходами первого дешифратора, выходы данных второго блока регистров соединены с соответствующими входами установки триггеров второго блока триггеров, а прямые выходы - с первыми входами второго блока элементов И, вторые входы которого соединены с соответствующими- выходами третьего дешифратора, входы третьего элемента ИЛИ соединены с входами идентификатбра устройства, выход третьего элемента ИЛИ соединен с входами сброса первого и второго блока триггеров, входы четвертого элемента ИЛИ соединены с выходами второго блока элементов И, выход четвертого элемента ИЛИ. соединен с входом установки триггера, вход сброса которого соединен с выходом вторагю элемента ИЛИ, входы пятого элемента ИЛИ соединены с выходами второго дешифратора, выход пятого элемента ИЛИ соединен через Элемент задержки с входом сброса регистра адреса.

От блокад

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты памяти | 1983 |

|

SU1113854A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ | 1990 |

|

RU2020564C1 |

| Устройство для ввода информации | 1989 |

|

SU1661749A1 |

| Адаптивное устройство для защиты памяти | 1983 |

|

SU1103291A1 |

| Устройство для защиты памяти | 1977 |

|

SU618741A1 |

| Устройство для защиты памяти | 1979 |

|

SU841065A2 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

| Устройство для идентификации магнитных карт | 1981 |

|

SU1005098A2 |

| СИСТЕМА УПРАВЛЕНИЯ ДОСТУПОМ К РЕСУРСАМ СЕТИ ИНТЕРНЕТ | 2008 |

|

RU2368004C1 |

| УСТРОЙСТВО ОГРАНИЧЕНИЯ ДОСТУПА К СЕКТОРАМ ЖЕСТКОГО ДИСКА | 2007 |

|

RU2359317C2 |

Изобретение относится к вычислительной технике и может быть использовано для защиты ячеек памяти от несанкционированного обращения к ним. Целью изобретения является расширение области применения устройства за счет обеспечения возможности управления количеством видов разрешенных операций с памятью для программы пользователя. Устройство состоит из трех дешифраторов 1,2,3, из двух блоков 4 и 5 регистров, двух блоков 8 и 9 элементов И, регистра адреса 10, пяти элементов ИЛИ 11-15, элемента задержки 16, триггера 17. 3 ил.

На блок 6

г

о

з:

V %У У N1/у W

I J7.7 J/f Г

I

4 у

311

Ц}иг2

20 w

о ее

у

Jt.

J/7

«

V

21 ЦЗиг.З

| Устройство для защиты памяти | 1975 |

|

SU552641A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР IP 747342, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-09-15—Публикация

1988-01-26—Подача