(54) АДАПТИВНЫЙ КОММУТАТОР.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный коммутатор | 1976 |

|

SU618861A1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Устройство для обработки изображений | 1989 |

|

SU1772806A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Телеметрическое устройство | 1977 |

|

SU703855A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| ТЕЛЕВИЗИОННОЕ СЛЕДЯЩЕЕ УСТРОЙСТВО | 1988 |

|

SU1574152A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

Изобретение относится к радиотех нике и может использоваться в многок нальных информационно-измерительных системах, использующимх квазиобра- тимое сжатие данных. По основному авт. св. № 618861 из вестен адаптивный коммутатор, содержащий входной регистр, выход которого подключен к первому информационному входу арифметического блока, управляющий выход которого подключен к входу формирователя функции приоритета, блок задания апертур, выход которого соединен с управляющим входом арифметического блока, оперативный запоминающий блок, выход и вход которого подключены к второму информационному входу и к первому информа ционному выходу арифметического блока соответственно, блок синхронизации и управления, первый вход которого подключен к входному регистру, второй выход соединен с синхронизирующими входами арифметического блока и оперативного запоминающего блока, а третий выход - к входу формирователя адреса и к синхронизирующему входу формирователя функции приоритета, и выходной регистр, а также дополнительный запоминающий блок, информационный вход которого соединен с вторым информационным выходом арифметического блока и с первым входом выходного регистра, а выход - к второму входу выходного регистра, первый и второй выходы формирователя функции приоритета соединены с первыми управляющими входами дополнительного запоминающего блока и выходного регистра соответственно, первый выход формирователя адреса подключен к управляющему входу формирователя функции приоритета, а второй выход - с вторым и управляющими входами дополнительного запоминаю- щено блока и выходного регистра И Однако известный коммутатор обладает низкой точностью коммутации. Цель изобретения - повыщение точности коммутации. Указанная цель достигается тем, что в адаптивный коммутатор,содержащий входной регистр, выход которого подключен к первому информационному входу арифметического блока, управляющий -выход которого подключен к входу формирователя функции приоритета, блок задания апертур, выход которого соединен с управляю Цймвходон арифметического блока, оперативный запоминающий блок, выход и вход которого подключены к BTdpoMy информационному входу и КП ервому информационному выходу арифметического блока соответственно, блок синхронизации и управления, первый выход которого подключен к входному регистру, второй выход соединен с синхронизующими входами арифметического блока и оперативного запоминающе о блока, а третий выход к входу формирователя адреса и к син.хронизирующему входу формирователя функции приоритета, и выходной регистр, а также дополнительный запоминающий блок, информационный вход которого соединен с вторым информационным выходом арифметического блока и с первым входом выходного регистра, а выход - к второму ходу выходного регистра, первый и второй выходы формирователя функции приоритета соединены с первыми управляюшими входами дополнительного запоминающего блока и выходного регистра соответственно, первый выход формирователя адреса подключен к управляющему входу формирователя функции приоритета, а второй выход - с вторым и управляющими входами дополнительного запоминающего блока и выходного регистра, введены ключевой блок, первый вход и выход которого соединены соответственно с первыг информационным выходом арифметического блока и входом оперативного запоминающего блока, а первый выход формирователя функции приоритета подключен к дополнительному управляющему йходу арифметического блока и к второму входу ключевого блока.

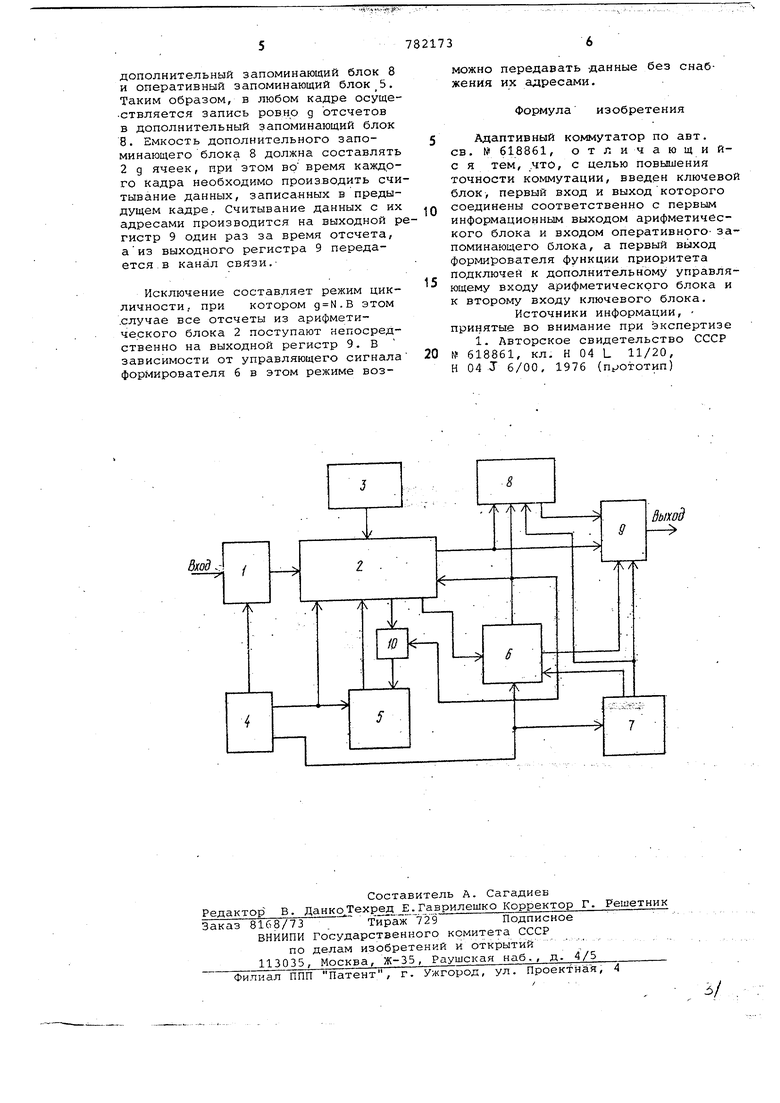

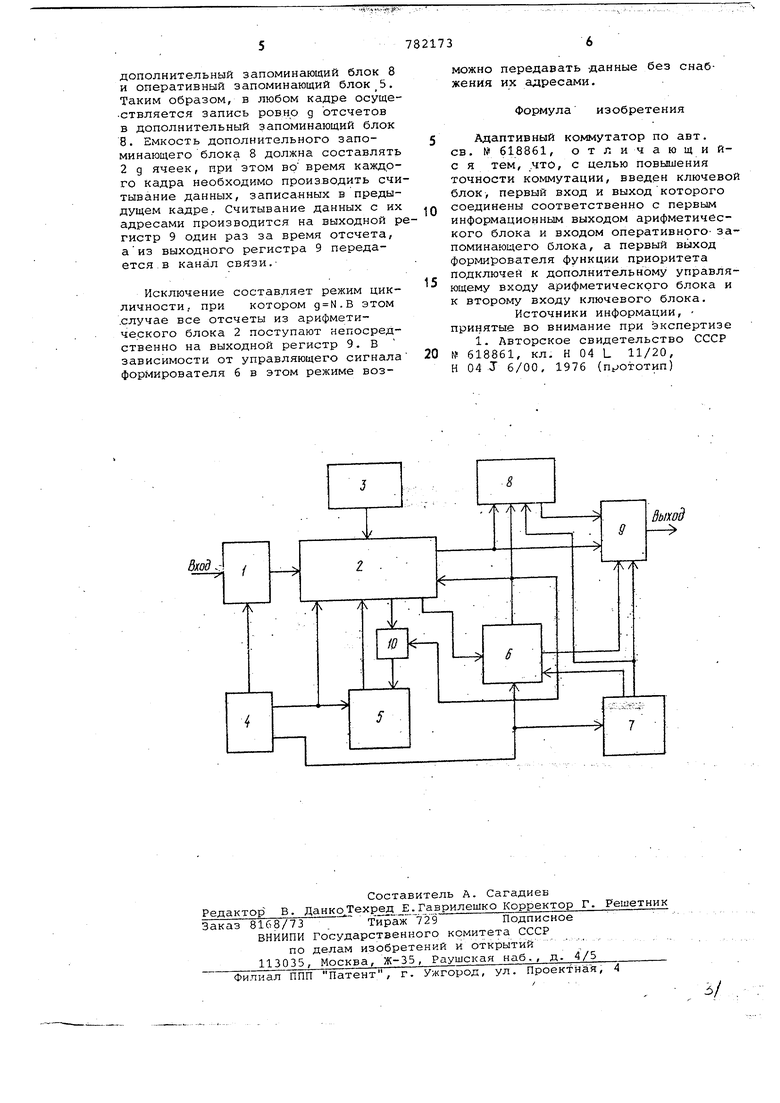

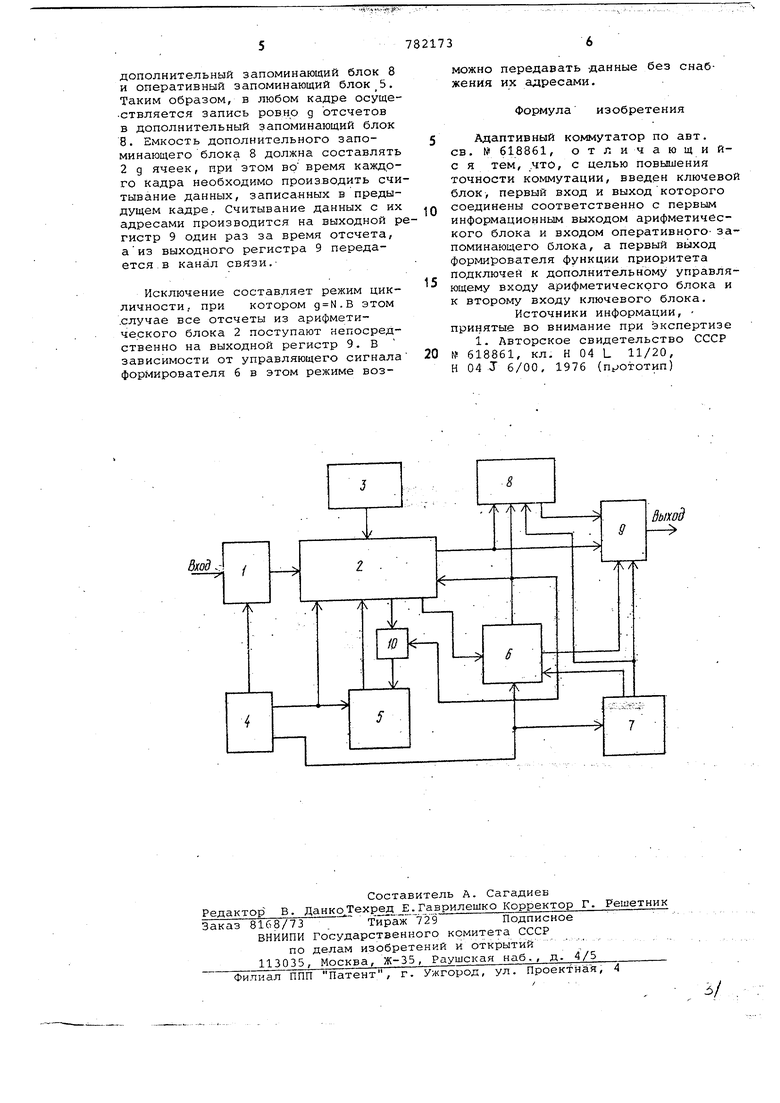

На чертеже приведена структурная электрическая схема предлагаемого коммутатора.

Адаптивный коммутатор содержит входной регистр 1, арифметический блок 2, блок 3 задания апертур, блок 4 синхронизации и управления, оперативный запоминающий блок 5, формирователь 6 функции приоритета, фор мирователь 7 адреса, дополнительный запоминающий блок 8, выходной регистр 9 и ключевой блок 10.

Адаптивный коммутатор работает следующим образом.

Входные сигналы в цифровой форме с циклической частотой поступают на входной регистр 1 и записываются на него по сигналам с первого управляющего выхода блока 4. На втором выходе блока 4 формируются сигналы, синхронизирующие работу арифметического блока 2 и оперативного запоминающего блока 5. По этим сигналам на арифметический блок 2 поступают код входного параметра с входного регистра . 1 и код предшествующего существенного отсчета данного канала из one- .

1P,...

ративного запоминающего блока 5. Арифметический блок 2 находит модуль разности этих двух кодов и сравни,вает его с величиной апертуры для данного канала, задаваемой блоком 3. Если разность превышает апертуру, на 5 управляющем выходе арифметического блока 2 появляется сигнал существенности.

Код текущего отсчета, снабженO ный специальным признаком перезаписи, формируется на первом информационном выходе арифметического блока 2 и, при открытом ключевом блоке 10, переписывается в ячейку оперативного запог минающего блока 5, предназначенную для хранения кодов существенных отсчетов данного канала. Сигналы существенности с управляющего выхода арифметического блока 2 подаются на формирователь 6, где осуществляется

их подсчет. Если за время кадра

еще не появилось необходимого числа g существенных отсчетов, формирователь б устанавливает в открытое состояние ключевой блок 10, а также разрешает перепись на дополнительный запоминающей блок 8 кодов существенных отсчетов со второго информационного выхода арифметического блока 2, снабх енных адресами (номерами каналов. информационно-измерительной системы) , которые определяет формирователь 7. После того как с начала кадра в формирователь 6 подано g сигналов существенности на выходе

5 формирователя 6 появляется сигнал,

закрывающий ключевой блок 10 и запрещающий запись данных в дополнительный запоминающий блок 8. Запрещение записи в дополнительный запоминающий блок О приводит к тому, что число существенных отсчетов, записываемых за время кадра, будет не более, чем 9. Если после g существенных отсчетов кадра до его окончания появятся новые существенные отсчеты, они не

5 занесутся ни в дополнительный запоминающий блок 8, ни в оперативный запоминающий блок 5. Поскольку содержимое оперативного запоминающего блока 5 остается неизменным,

0 при следующем опросе данного ка,нала отсчет оказывается сущест- венным и, если перед ним не было g существенных отсчетов (вероятность чего невелика, поступает в до полнитель.ный запоминающий блок 8. В тех случаях, когда в первых (N-i) каналах кадра оказалось (g-i) существенных отсчетов, формирователь б выдает специальный сигнал на второй управляющий вход арифметического

0 блока 2. С приходом этого сигнала арифметический блок 2 переходит в режим принудительной существенности, и отсчеты в последних I каналах кадра, вне зависимости от их дейст5 витальной величины, записываются в

дополнительный запоминающий блок 8 и оперативный запоминающий блок 5. Таким образом, в любом кадре осуществляется запись ровно g отсчетов в дополнительный запоминающий блок 8. Емкость дополнительного запоминающего блока 8 должна составлять 2 g ячеек, при этом во время каждого кадра необходимо производить считывание данных, записанных впредыдущем кадре. Считывание данных с их адресами производится на выходной ргистр 9 один раз за время отсчета, а из выходного регистра 9 передается в канал связи.Исключение составляет режим цикличности, при котором .B этом .случае все отсчеты из арифметического блока 2 поступают непосредственно на выходной регистр 9. В зависимости от управляющего сигнала формирователя б в этом режиме возВход,:

можно передавать данные без снабжения их адресами.

Формула изобретения

Адаптивный коммутатор по авт. св. № 618861, отличающийс я тем, .что, с целью повышения точности коммутации, введен ключевой блок, первый вход и выход которого соединены соответственно с первым

0 информационным выходом арифметического блока и входом оперативного- запоминающего блока, а первый выход формирователя функции приоритета подключей к дополнительному управля5ющему входу арифметического блока и к второму входу ключевого блока.

Источники информации, принятые во внимание при экспертизе

0 № 618861, кл. Н 04 L 11/20, Н 04 J 6/00, 1976 (прототип)

Авторы

Даты

1980-11-23—Публикация

1979-02-23—Подача