(54) АНАЛОГОВОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1977 |

|

SU666584A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU991514A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU680058A1 |

| Емкостное накопительное устройство | 1975 |

|

SU555540A1 |

| Устройство для контроля сопротивления резистивного элемента | 1988 |

|

SU1707789A1 |

| Ячейка памяти | 1979 |

|

SU1022222A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU920843A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1506368A1 |

| Переключающее устройство | 1984 |

|

SU1200408A1 |

| Аналоговое запоминающее устройство | 1976 |

|

SU633073A1 |

Изобретение относится к области вычислительной техники, Б частности к запоминающим устройствам.

Известно аналоговое запоминающее устройство, состоящее из электронного ключа, запоминающего конденсатора и буферного усилителя LIJ. В режиме хранения информации такому устройству присуща погрешность, обусловленная конечным сопротивлением разомкнутого ключа.

Известно так же аналоговое запоминающее устройство, содержащее ключ заряда, выполненный на МДП-транзисторе, исток которого подключен к накопительному элементу, например конденсатору, и входу усилителя, и блок управления 2.

Однако в режиме хранения информации в известном устройстве возникает погрещность, обусловленная разрядом конденсатора паразитными токами, которые вызваны разностью потенциалов истока и затвора, а также истока и подложки МДП-транзистора; указанная погрещность является одной из причин, ограничивающих время

хранения информации в устройствах данного типа.

Целью изобретения является увеличение времени хранения.

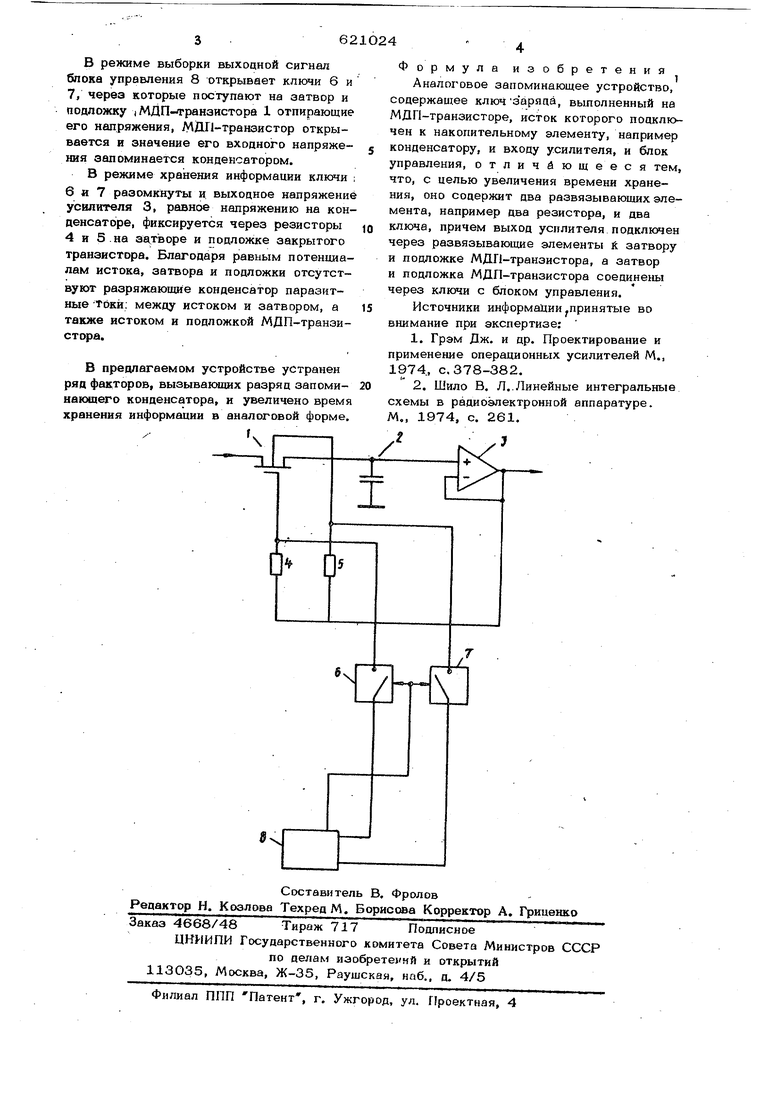

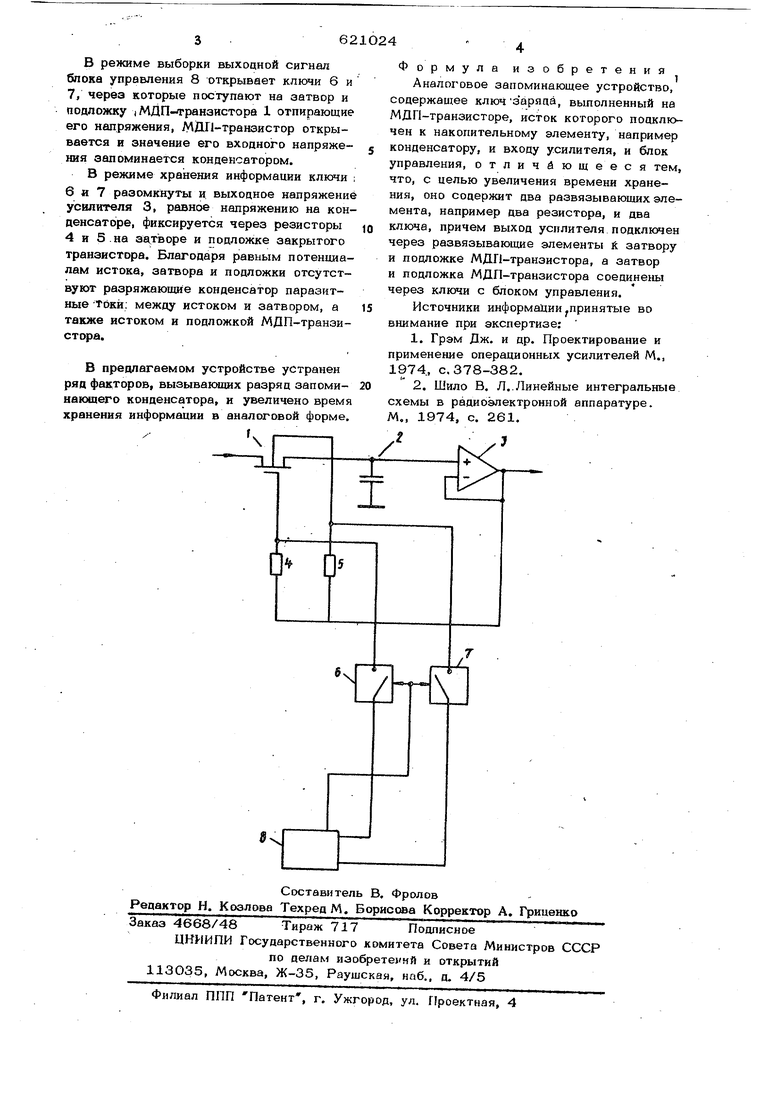

Это достигается тем, что аналоговое запоминающее устройство содержит два развязывающих элемента, например два резистора, и два ключа, причем выход усилителя подключен через развязывающие элементы к затвору и подложке МДП-гранзистора, а затвор и подложка МДП-транзистора соединены через клгчи с блоком управления.

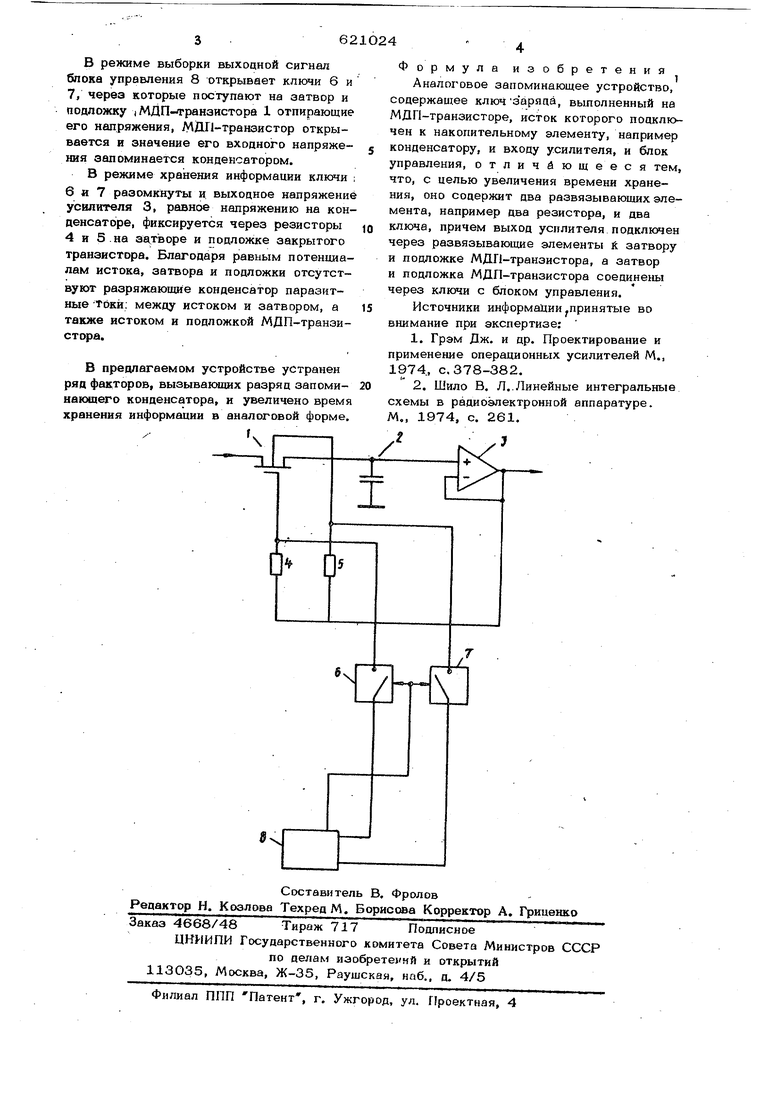

На чертеже показана принцклиальная схема устройства.

Аналоговое запоминающее устройство содержит ключ заряца выполненный на МДП-транзисторе 1, накопительный элемент .выполненный на конденсаторе 2, угцлитель 3, первый и второй развязывающие элементы 4 и 5, выполненные на резисторах, первый и второй ключи 6 и 7 и блок управление 8.

Устройство работает следующим образом. В режиме выборки выходной сигнал блока управления 8 открывает ключи 6 и 7, через которые поступают на затвор и подложку ) МДП-транэистора 1 отпирающие его напряжения, Д ДП-транзистор открывается и значение его входного напряжения запоминается конденсатором. В режиме хранения информации ключи 6 и 7 разомкнуты и выходное напряжение усилителя 3, равное напряжению на кон денсаторе, фиксируется через резисторы 4 и 5.на затворе и подложке закрытого транзистора. Благодаря равным потенциалам истока, затвора и подложки отсутствуют разряжающие конденсатор паразитные -тькй: между истоком и затвором, а также истоком и подложкой МДП-транэистора. В предлагаемом устройстве устранен ряд факторов, вызываклцих разряд запоминающего конденсатора, и увеличено врем хранения информации в аналоговой форме

:г Формула изобретения Аналоговое запоминающее устройство, содержащее ключзаряай, выполненный на МДП-транзисторе, исток которого подключен к накопительному элементу, например конденсатору, и входу усилителя, и блок управления, отличающееся тем, что, с целью увеличения времени хранения, оно содержит два развязывающих элемента, например два резистора, и два ключа, причем выход усилителя подключен через развязывающие элементы и затвору и подложке МДП-транзистора, а затвор и подложка МДП-транзистора соединены через ключи с блоком управления. Источники информации,принятые во внимание при экспертизе; 1. Грэм Дж. и др. Проектирование и применение операционных усилителей М., 1974, с. 378-382. 2. Шило В. Л..Линейные интегральные схемы в радиоэлектронной аппаратуре. М., 1974, с. 261.

Авторы

Даты

1978-08-25—Публикация

1977-02-08—Подача