(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU830583A1 |

| Устройство для хранения и выборкииНфОРМАции | 1979 |

|

SU841058A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1065889A1 |

| Устройство для управления сигнальными лампами светофора | 1988 |

|

SU1674214A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU875465A1 |

| Коммутатор аналоговых сигналов | 1987 |

|

SU1458971A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU890440A1 |

| Управляемый мультивибратор | 1986 |

|

SU1420646A1 |

| Ключ переменного тока | 1990 |

|

SU1725380A1 |

1

Изобретение предназначено, для использования в схемах автоматики, в частности в корректурах нуля промышленных хроматографов, в устройствах Для интегрирования и запоминания сигналов, отражакицих площади пиков анализируемых компонентов, а также в устройствах определения высот и дискриминации неразделенных пиков.

Известно аналоговое запоминающее устройство, содержащее накопительный конденсатор, соединенный соответственно со входом дифференциального усилителя постоянного тока и ключом, через который поступает усиленный сигнал дрейфа нулевой линии хроматографа в промежутках между анализами ij . Это устройство характеризуется малым временем и низкой точностью хранения информации. Из известных аналоговых запоминающих устройств наиболее близким к изобретению является аналоговое запомингиощее устройство, содержащее повторитель напряжения, вход которого подключен через накопительный злемент к шине нулевого потенциала, один из выходов повторителя напряжения соединен с первым входом дифференциального усилителя 2. В этом известном устройстве

непостоянство хранимой информации, зависит от утечек заряда накопительного элемента, а так как в процессе хранения информации имеют место различные скорости спада напряжения на накопительном злементе, обусловленные экспоненциальным законом изменения напряжения на нем, то с увеличением времени хранения абсолютное значение потериинформации увеличивается и будет тем больше, чем боЛьше начальное значение напряжения, которое необходимо запомнить. Кроме того конденсаторы, применяемые в качестве накопительных элементов, имеют существенный разброс такого параметра, как сопротивление изоляции определяемое отношением приложенного к конденсатору напряжения к величине тока утечки i ут . Разброс этого параметра накладывает дополнительную погрешность от образца к образу в известных запоминающих устройствах. Таким образом, известное запоминающее устройство имеет низкую точность и малое время хранения информации, что особенно проявляется с увеличением абсолютных значений напряжений и делает это устройство непригодным для применения в измерительной технике,

где необходима точная количественная оценка информации

Целью изобретеЙия является поныше iHe точности и увеличение времени хранения информации.

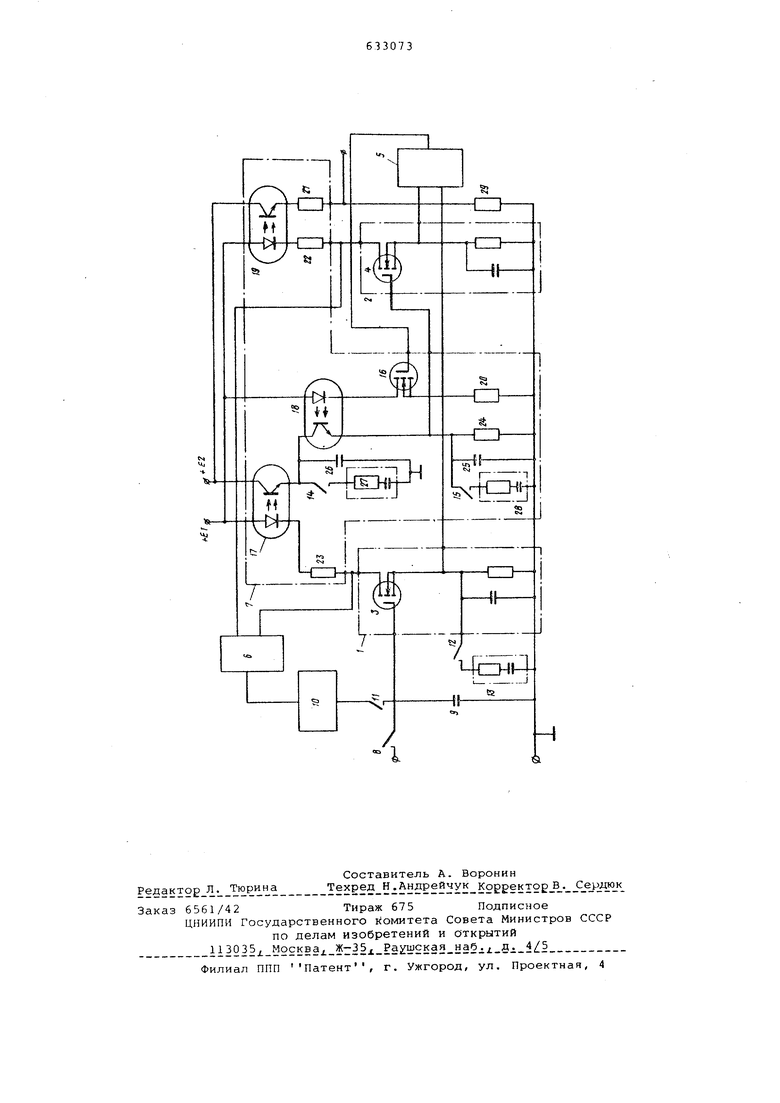

В описываемом устройстве это достигается тем, что дополнительно содержит блок сравнения, блок коррекции, блок подзаряда, элемент задержки, ключи и дополнительный повторитель напряжения, выходы которого соединены со вторым входом дифференциального усилителя, с первым выходом блока коррекции и одним из входов блока сравнения соответственно, вход дополнительного повторителя напряжения соединен со вторым выходом блока коррекции, один из входов которого соединен с выходом дифференциального усилителя, другой вход блока коррекции подключен .к другому повторителя напряжения и другому входу блока ера8не зия, выход которого соединеа с вкодом блока подэаряда, вы- код блока подзаряда через первый пояйлючен к накопительному элементу, один из выходов повторителя иапряж 2иия подключен через последовательно соединенные второй ключ и элемент задержки .к шине нулевого, потенциала. При этом блок коррекции содержит ключи, МОП-транзистор, резисторы, конденсаторы, оптроны -цепи причем Si tTTep фототранзистора пер вого оптрона -соединен с,коллектором фототранзистора второго оптрона- к через последовательно соединенные первый ключ и первую Т С -цепь - с шиной нулевого потенциала, эмиттер фототранзистора второго оптрона соединен со вторым выходом блока коррекции и через резистор и последовательно соединенные второй ключ и вторую - с шиной нулевого потенциала, катод светодиода второго оптрона через последовательно соединенные МОП-транзистор и первый резистор подключен к шине нулевого потенциала, затвор МОП-транзистора соединен с одним из входов блока коррекции, эми тер фототранзистора третьего оптрона .через второй резистор соединен с третьим выходом блока коррекции, катод еветодиода третьего оптрона чере третий резистор соединен с nepBHivi выходом блока коррекции, катод светоди да первого оптрона через четвертый резистор соединен е другим входом блка коррекции, аноды светодиодов всех оптронов и коллекторы фототранзисто.ров первого и третьегооптронов соединены с шинами напряжения питания. На чертеже представлена принципиальная электрическая схема описы.ваемого устройства.

Оно содержит повторитель напряжения 1 и дополнительный повторитель .напряжения 2, выполненные на МОП-тра зисторах 3 и 4 (с индуцнрованньол каналом п -типа), истоки которых, являющиеся одними выходами повторителей напряжения 1 и 2, соединены соответственно с первым и вторым выходами дифференциального усилителя 5. Стоки МОП-транзисторов 3 и 4, являющиеся другими выходами повторителей напряжения 1 и 2, подключены ко входам блока сравнения 6, причем указанный выход повторителя напряжения 1 соединен также со входом блока коррекции 7, а указанный выход дополнительного повторителя напряжения 2 соединен с первым выходом блока коррекции 7, Вход повторителя 1 соединен с ключом 8 и накопительным элементом (конденсатором.) 9, а вход дополнительного повторителя напряжения 2 подключен ко второму выходу блока коррекции 7. Выход блока сравнения 6 соединен со входом блока подзаряда 10, выход которого через первый ключ 11 подключен ко входу повторителя напряжения 1, выход которого через второй ключ 12 подсоединен к элементу задержки 13, соединенному с шиной нулевого потенциала. Блок коррекции 7 содержит первый ключ 14, второй ключ 15, МОП-транзистор 16, первый оптрон 17, второй оптрон 18, третий оптрон 19, первый резистор 20 второй резистор 21, третий резистор 22, четвертый резистор 23 и резистор 24, конденсаторы 25 и 26, первую RC -цепь 27 и вторуюТ С -цепь 28, нагрузочный резистор 29. Эмиттер фототранзистора первого оптрона 17 соединен с коллектором фототранзистора второго оптрона 18 и через последовательно соединенные первый ключ 14 и первуюТ С -цепь 27 - с шиной нулевого потенциала. Эмиттер фототранзистора второго оптрона 18 соединен со вторым выходом блока коррекции 7 и через резистор 24 и последовательно соединенные второй ключ 15 и вторую -цепь 28 - с шиной нулевого потенциала. Катод светодиода второго оптрона 18 через последовательно Соединенные МОП-транзистор 16 и первый резистор 20 подключен к шине нулевого потенциала, а затвор МОПtpaHSHCTopa 16 соединен с одним из входов блока коррекции 7. Эмиттер фототранзистора третьего оптрона 19 через второй резистор 21 соединен с Третьим выходом блока коррекции 7, катод светодиода третьего оптрона 19 через третий резистор 22 соединен с первым выходом блока коррекции 7, а катод светодиода первого оптрона 17 «ерез четвертый резистор 23 соединен со входом блока коррекции 7. Аноды светодиодов всех оптронов 17, 18 и 19 и коллекторы фототранзисторов первого и третьего оптронов 17 и 19 соединены с шинами напряжения питания.

Работа устройства состоит из режима установления заряда на накопительном элементе 9 и режима хранения заряда (информации), причем режим уста новления заряда в зависимости от характера (увеличения или уменьшения) изменяющегося напряжения, подлежащег запоминанию, может быть режимом увеличения или уменьшения заряда на накопительном элементе 9. В режиме установления (увеличения) заряда на накопительном элементе 9 ключи 14 и 15 блока коррекции, а также ключи 1 и 12 - разомкнуты, а ключ 8 - замкну С возрастанием напряжения на накопительном элементе 9 увеличивается про водимость канапа МОП-транзистора 3, что вызывает увеличение тока через светодиод первого оптрона 17 блока коррекции 7. При этом возрастающее излучение света светодиода первого оптрона Г7 посредством оптической связи, обеспечивающей гальваническую развязку и повьзшение устойчивости, увеличивает проводимость фототранзистора этого оптрсна. Это вызывает увеличение тока по цепи от источника Е2 через фототранзистор пер вого оптрона 17, не полностью откры тый фототранзистор второго оптрона 18 и резистор 24. Возрастающее напряжение на резисторе 24 блока кор рекции 7 по абсолютной величине повторяет напряжение на накопительном элементе 9. Если это напряжение на каком-либо участке рабочего диапазона запоминаемых напряжений не равно напряжению на накопительном элементе 9, то под действием появивщегося сигнала разбаланса, поступающего с повторителя напряжения 1 и дополнительного повторителя напряжения 2 на входы дифференциального усилителя 5, выходной сигнал которого поступает на МОП-транзистор 16, изменяется проводимость фототранзистора второго оптрона 18 блока коррекции 7 так, что напряжени,. на резисто ре 24 становится равньлм напряжению на накопительном элементе 9, т.е. осуществляется постоянное отслеживание сигнала. Если напряжение поступающее на накопительный элемент 9 после возрастания начинает уменьшать ся, то на резисторе 24 блока коррекции 7 оно по абсолютной величине повторяется также. Конденсаторы 25 и 26 обеспечивают неизменность напряжения на резисторе 24 и на коллекторе фототранзистора второго оптрона 18 непосредственно до и после коммутации при переключении на режим хранения заряда. В режиме хранения заряда на накопительном элементе 9 ключ 8 - разомкнут, ключи 14 и 15 блока коррекции, а также ключи 11 и 12 - замкнуты. Изменение напряжения на накопительном элементе 9 за счет утечек его заряда должно вызывать через некоторое время, называемое временем за6б дсржки tJ, изменение напряжения на истоке МОП-транзистора 3 и на стоке МОП-транзистора 4, определяемое напряжением на резисторе 24. Следовательно, в течение некоторой части (начального участка) времени задержки i напряжение на входе дифференциального усилителя 5 и на стоке МОП-транзистора 4 остается практически неизменным, а напряжение на стоке МОП-транзистора 3 изменяется (повышается) , поскольку уменьшается проводимость его клапана, из-за понижения потенциала на его затворе, соеди- . ненного с накопительным элементом 9. Таким образом, в это время нарушается равенство напряжения на стоках МОП-транзисторов 3 и 4. Под действием разности напряжения на входе блока сравнения 6, управляющего работой блока подзаряда 10, восстанавливается потенциал на накопительном элементе 9 путем его подзаряда, осуществляемого блоком подзаряда 10. При этом время восстановления -tg значительно меньше времени задержки tj. Для детального анализа работы устройства рассмотрим время задержки tj Представим изменяющееся напряжение на накопительном конденсаторе в виде бесконечной суммы ступенек или импульсов . Каждый такой импульс характеризуется экспоненциальным фронтом с постоянной времени изменения tф . Этот импульс поступает на вход схемы блока коррекции, обладающей свойством интегрирующей цепи с постоянной времените ц. Известно, что вид функции, выражающей сигнал на выходе интегрирующей цепи, определяется в зависимости от соотношения между t ц . При f-ф и, сигнал (напряжение) на выходе интегрирующей цепи сдвигается во времени, т.е. имеет место задержка сигнала. Так, например, известно, что в случае идеального скачка при 1ц -е t ф время задержки определяется t3 05tu. При , этом время восстановления потенциала на накопительном конденсаторе должно быть значительно меньше-времени задержки, т.е. должно соблюдаться условие t J, -i t 3 причем время восстановления определяется постоянными времени блоков сравнения и подзаряда. Следовательно, повышается точность описываемого устройства и увеличивается время хранения информации. Кроме того, за счет малого времени восстановления потенциала на накопительном конденсаторе разброс величины сопротивления его изоляции не вносит погрешности в процессе хранения информации. Таким образом, описываемое аналоговое запоминающее устройство обеспечивает хранение информации с более 76 высоким классом точности длительное время (обеспечивается практически неизменное во времени хранение инфор мации) , что позволяет использовать его не только в хроматографической аппаратуре, но и как блок аналоговой пгиняти в целом ряде систем автоматини и телемеханики, в информационноизмерительной и вычислительной технике, в устрюйствах регулирования и управления технологическим процессом, в решении задач автоматизации научного эксперимент.а, в системах связи, основанных на методе накопления и корреляционном методе приема, где обязательным элементом служат накопители сигнала, а также и в других устройствах, где требуется для целей измерения или управления накоп ление информации в аналоговой форме. Формула изобретения 1. Аналоговое запоминающее устройство, -содержащее повторитель напряжения, вход которого подключен че рез накопительный элемент к шине нулевого потенциала, один из выходов повторителя напряжения соединен с первым входом дифференциального усилителя, отличающееся тем, что, с целью повьшиения точности и увеличения времени хранения, устройство содержит блок сравнения, бло коррекции, блок подзаряда, элемент задержки, ключи и дополнительный пов торитель напряжения, выходы которого соединены со вторым входом дифференциального усилителя, с первым выходом блока коррекции и одним из входо блока сравнения соответственно, вход дополнительного повторителя напряжения соединен со вторым выходом блока коррекции, один из входов которого соединен с выходом дифференциального усилителя, другой вход блока коррекц подключен к другому выходу повторителя напряжения и другому входу блока сравнения, выход которого соедине с входом блока подзаряда, выход блока подзаряда через первый ключ подключен к накопительному элементу, один из выходов повторителя напряжения подключен через последовательно соединенные второй ключ и элемент задержки к шине нулевого потенциала. 2. Аналоговое запоминающее устройство попЛ, отличающееся тем, что блок коррекции содержит ключи, МОП-транзистор, резисторы, конденсаторы, оптроны -цепи, причем эмиттер фототранзистора первого оптрона соединен с коллектором фототранзистора второго оптрона и через последовательно соединенные первый ключ и первуюТ С -цепь - с шиной нулевого потенциала, эмиттер фототранзистора второго оптрона соединен со вторым выходом блока коррекции и через резистор и последовательно соединенные второй ключ и вторую RC -цепь - с шиной нулевого потенциала, катод светодиода второго оптрона через последовательно соединенные МОП-транзистор и первый резистор подключен к шине нулевого потенциала, затвор МОП-транзистора соединен с одним из входов блока коррекции, эмиттер фототранзистора третьего оптрона через второй резистор соединен с третьим выходом блока коррекции, катод светодиода третьего оптрона через третий резистор соединен с первым выходом блока коррекции, катод светодиода.первого оптрона через четвертый резистор соединен с другим входом блока коррекции, аноды снетодиодов всех оптронов и коллекторы фототранзисторов первого и третьего оптронов соединены с шинами напряжения питания. Источники информации, принятые во внимание при экспертизе: 1.Патент США № 3886786, кл. 7327, 1975. 2.Конев Ю.И. Электронная техника в автоматике. Советское радио , М., 1975, с. 140-144.

Авторы

Даты

1978-11-15—Публикация

1976-11-26—Подача