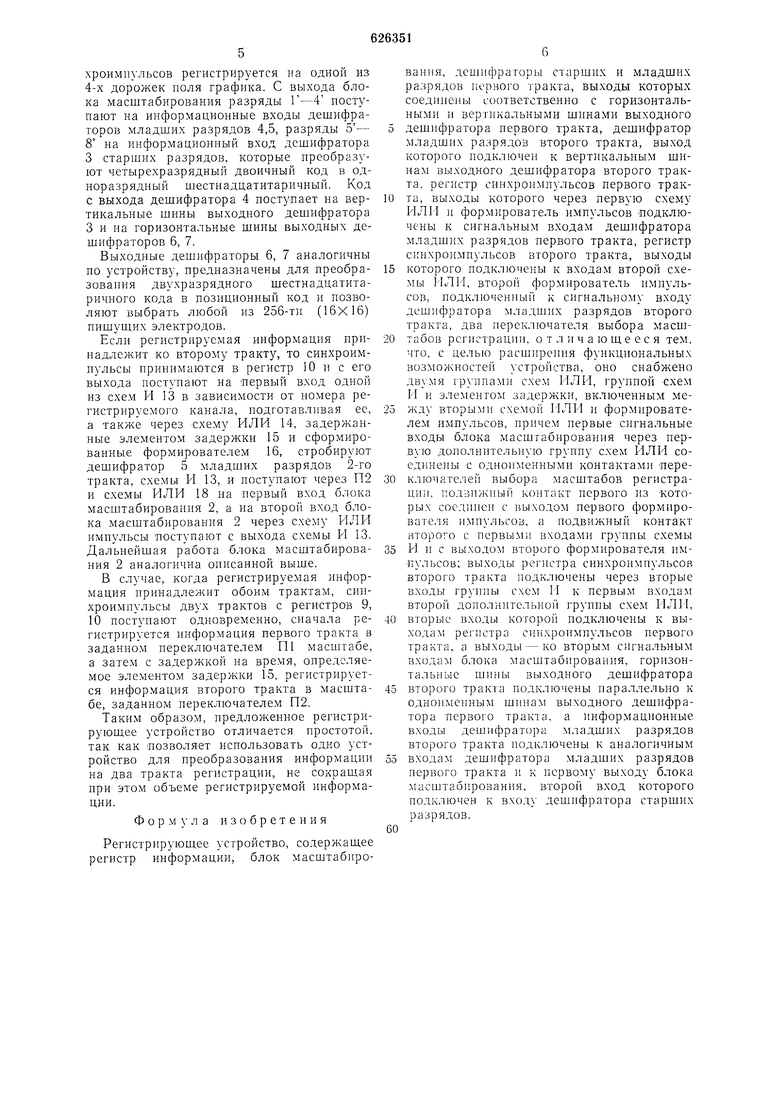

подключены параллельно к одпоиме15ным шипам выходпого дешифратора первого тракта, а ипформацпоппые входы дешифратора младших разрядов второго тракта подключены к аналогичным входам дешифратора младших разрядов aiepBoro тракта и к первому выходу блока масштабирования, второй выход которого подключен к входу дешифратора старших разрядов. Блок-схема предлагаемого устройства 10 изображена иа чертеже. Регистрируюш,ее устройство содержит регистр информации 1, выходы которого через б.ток масштабироваиия 2 подключены к информационным входам дешифрато- 15 ра .старших разрядов 3 и дешифраторов младших разрядов 4, 5 первого п второго тракта, выходные дешифраторы 6, 7 горизонтальные шипы которых подключены параллельно к выходу дешифратора старгних 20 разрядов 3, а вертикальные н-1ииы соответетвеино к выходам дешифраторов младших разрядов 4, 5, блоки регистрации 8, 8, нодключенные к выходным дешифраторам, регистры 9, 10 синхроимпульсов измерн- 25 тельных каналов, нричем выходы регистра 9 через схему ИЛИ 11 и формирователь иМпульсов 12 иодключсны к сигиал1эиому входу дешифратора младших разрядов 4 первого тракта, а выходы регистра 10 под- 30 ключсны к иервым входам группы схем И 13, а также через схему ИЛИ 14, элемент задержки 15 и формирователь импульсов 16 ко вторым входам группы схем И 13 и к сигнальному входу дешифратора 5 млад- 35 ших разрядов второго тракта. Выходы схем И 13 и регистра 9 через грунну схем 5 О ИЛИ 17 подключены ко вторым входам блока масштабирования 2, к первым входам которого через груииу схем ИЛИ 18 подключеиы одноименные контакты лереключателей выбора масштаба И1, И2, подвижпые контакты которых соедпнсны с выходами формирователей 12, 16 соответстзенпо. Следует, отметить, что каждый тракт предлагаемого устройства позволяет регистрировать информацию четырех измерительных каналов в масштабах 1:1 1 ;4. Устройство работает следуюшим Синхроимпульсы измерительных лов. например, первого тракта иоступают в регистр 9 и запоминаются на время, определяемое длительностьк} нмпульса формн ювателя 12, одновременно информация, иодлежащая регистрации, иринимается в регистр 1 и далее поступает в блок масштабпроваиня 2. Ири этом информация каждого ка}1ала па вход блока масштабирования поступает 3 виде восьмиразрядного парал.тельного двоичного кода. Кроме того, в бл(ж масьлтабирования 2 поступает сигиал с выхода регистра 9 через одиу из схем 1-1ЛИ 17 л признак мас1нтаба региетрацнн с одной n:i схем ИЛИ 18. В блоке маснпабировгишя 2 в зависимости от выбрапного маспггаба регистрации и номера измер ггсльного канала (сиихронмцульсов) произьодится нреобра: ованне илформации, которое может быть проиллюстрировано следуюишй таблицей:

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистрирующее устройство | 1977 |

|

SU748137A1 |

| Регистрирующее устройство | 1977 |

|

SU669192A1 |

| Регистрирующее устройство | 1986 |

|

SU1500830A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ БЫСТРОМЕНЯЮЩЕГОСЯ ПРОЦЕССА | 1990 |

|

RU2007756C1 |

| Устройство для отображения информации | 1987 |

|

SU1513439A1 |

| Устройство регистрации информации с координатной камеры | 1983 |

|

SU1172381A1 |

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1560980A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| УСТРОЙСТВО ДЛЯ ПЕРВИЧНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1973 |

|

SU367426A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

Как видно из таблицы при регистрации информации в маештабе 1 :1 информация проходит через блок масштабирования 2 без сдвига н регистрируется Но нолю графика; в масштабе 1 :2 информация сдвигается на один разряд в сторону младших разрядов, т. е. делится на два. Ири этом, если информация иринадлежит первому и третьему каналам, она регистрируется на первой половине дорожки поля графика, если информация принадлежит второму или четвертому каналу, то к значению информации по сиихроимнульсу этих каналов в 8-й разряд вводится «единица, т. е. добавляется число 128 и информация регистри)уется на второй дорожке; в масиггабе 1 :4 информация делится на 4 и в зависимости от номера синхроимиульсов регистрируется на одной из 4-х дорожек иоля графика. С выхода блока масштабирования разряды 1-4 постуиают на информационные входы дешифраторов младших разрядов 4,5, разряды 5- 8 на информационный вход дешифратора 3 старших разрядов, которые преобразуют четырехразрядный двоичный код в одноразрядиый шестиадцатитаричный. Код с выхода дешифратора 4 постунает на вертикальные шины выходного дешифратора 3 и на горизонтальные шины выходных дешифраторов 6, 7.

Выходные дешифраторы 6, 7 аналогичны по устройству, предназначены для преобразования двухразрядного шестнадцатитаричного кода в позиционный код и позволяют выбрать любой из 256-Tii (16X16) пишущих электродов.

Если регистрируемая информация принадлежит ко второму тракту, то синхроимпульсы принимаются в регистр 10 и с его выхода поступают на первый вход одной из схем И 13 в зависимости от номера регистрируемого канала, подготавливая ее, а также через схему ИЛИ 14, задержанные элементом задержки 15 п сформированные формирователем 16, стробируют дешифратор 5 младших разрядов 2-го тракта, схемы И 13, и поступают через И2 и схемы ИЛИ 18 на первый вход блока масштабирования 2, а на второй вход блока масштабирования 2 через схему ИЛР1 импульсы поступают с выхода схемы И 13. Дальнейшая работа блока масштабирования 2 аналогична оиисанной выше.

В случае, когда регистрируемая информация принадлежит обоим трактам, синхроимпульсы двух трактов с регистров 9, 10 поступают одновременно, сначала регистрируется информация первого тракта в заданном переключателем П1 масштабе, а затем с задержкой на время, определяемое элементом задержки 15, регистрируется информация второго тракта в масштабе, заданном переключателем П2.

Таким образом, предложеиное регистрирующее устройство отличается простотой, так как позволяет использовать одно устройство для преобразования информации на два тракта регистрации, не сокращая при этом объеме регистрируемой информации.

Формула изобретения

Регистрирующее устройство, содержащее регистр информации, блок масштабирования, дешифраторы старших и младших разрядов первого тракта, выходы которых соединены соответственно с горизонтальными и вертикальными шинами выходного дешифратора первого тракта, дешифратор младших разрядов второго тракта, выход которого подключен к вертикальным щинам выходного дешифратора второго тракта, регистр синхроимпульсов первого тракта, выходы которого через первую схему ИЛИ и формирователь импульсов подключены к сигнальным входам дешифратора младших разрядов первого тракта, регистр синхроимпульсов второго тракта, выходы

которого подключены к входам второй схемы ИЛИ, BTOpoii формирователь импульсов, подключенный к сигнальному входу дешифратора младших разрядов второго тракта, два переключателя выбора масштабов регистрации, отличающееся тем. что, с целью расширения функциональных возможностей устройства, оно снабжено двумя группами схем ИЛИ, группой схем И и элементом задержки, включенным между вторыми схемой ИЛИ и формирователем импульсов, причем первые сигнальные входы блока масштабирования через первую дополнительную группу схем ИЛИ соединены с одноименными контактами переключателеП выбора масштабов регистрации, подвижиьи контакт первого из которых соединен с выходом первого формирователя импульсов, а подвижный контакт второго с первьпги входами группы схемы

И и с выходом второго формирователя импульсов; выходы регистра синхроимпульсов второго тракта подключены через вторые входы группы схем И к первым входам второй дополнительно схем ИЛИ,

вход которо подключены к выходам регистра С нхро 1мпульсов перво Ч) тракта, а выходы - ко вторым с 1гнальнь М входам блока мас11 таб рова} Я, гор 13онталь Пз1е выходного дешифратора

вто)ого тракта одкл очены араллельно к одноименным шипам выходного дешифратора первого тракта, а информационные входы деш фратора младших разрядов второго тракта подкл очены к аналогичным

входам деш 1фратора младших разрядов первого тракта i к первому выходу блока масштаб рован я, второй вход которого подключен к входу дешифратора старших разрядов.

Авторы

Даты

1978-09-30—Публикация

1975-09-01—Подача