образования и задержки кода, а входы первого приоритетного шифратора его второй группой из лГй входов, выходы первого приоритетного шифратора соединены с входами дешифратора, с группой управляющих (адресных) входов всех мультиплексоров и являются информационными выходами старших раз рядов координат, выходы мультиплексоров подключены к первым управляющим входам соответствующих им триггеров -|п разрядного регистра, прямые выходы которых подключены к входам второго приоритетного шифратора и к первым входам соответствующих элементов И первой группы, выходы которых через соответствующие им элементы ИЛИ первой группы соединены с вторыми управляющими входами соответствуюш;их триггеров, -fn разрядного регистра, инверсные выходы которых через соответствующие элементы задержки первой группы из -jn элементов задержки подключены к первым входам элементов И второй группы, вторые входы элементов И обеих групп подключены к выходу элемента И второй группы предыдущего разряда, а вторые входы элементов И, обеих групп, относящиеся к триггеру ЧтГ разрядного регистра наивысшего приоритета, через первый элемент задержки соединены с управляющим входом второго приоритетного шифратора-и с выходом первого элемента И, первый

вход которого через второй элемент задержки соединен с первым управляющим выходом второго приоритетного шифратора, первый управляюш 1Й выход первого приоритетного шифратора подключен к первому входу второго элемента И, к входу одновибратора и через третий элемент задержки - к второму входу первого элемента И, выход второго элемента И соединен с управляющим входом одновибратора и с управляющим входом дешифратора, второй вход второго элемента И через четвертый элемент задержки подключен к второму управляющему выходу второго приоритетного шифратора, выход одновибратора соединен с управляющим (стробируюш 1м) входом всех мультиплексоров, выходы дешифратора соединены с входами соответствующих им элементов ИЛИ второй группы, вторые входы всех элементов ИЛИ первой и второй групп объединены и соединены с вторым управляющим входом блока, выходы второго приоритетного шифратора являются информационными выходами младших разрядов координат события, управляющий вход первого приоритетного шифратора является первым управляющим входом блока, а его второй управляющий выход является выхо. дом конца преобразования координат события, а выход первого элемента И является первым управляющим выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство регистрации информации с координатной камеры | 1989 |

|

SU1612269A1 |

| Устройство для ввода информации | 1983 |

|

SU1108427A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 1997 |

|

RU2121754C1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Устройство для магнитной записи и воспроизведения цифровой информации | 1981 |

|

SU970441A1 |

1. УСТРОЙСТВО РЕГИСТРАЦИИ ИНФОРМАЦИИ С КООРДИНАТНОЙ КАМЕРЫ, содержащее п входных усилителей, празрядный регистрJ разделенный на -jti групп триггеров н запоминающее устройство, содержащее информационные входы и два управляюш 1х входа: синхронизации и стробирования, причем выходы входных усилителей подключены к первым управляющим входам соответствующих им п групп триггеров п-разрядного регистра, отличающеес я тем, что, с целью увеличения быстродействия с одновременным сокращением электронного оборудования, в него введены блок асинхронного преобразования и задержки кода, содержащий первую группу из п входов, вторую группу из входов, два зп равляющих входа, группу из лГп управляющих выходов, информационные выходы и два управляющих выхода, а также (-Jn+1) элементов ИЛИ, имеющих каждый -Jn входов, причем выходы триггеров п-разрядного регистра подключены к первой группе из п входов блока асинхронного преобразования и задержки кода, выходы каждой группы триггеров подключены к входам соответствующих им лГп элементов ИЛИ, выходы которых соединены со второй группой из входов блока асинхронного преобразования и задержки кода и к входам ()-элемента ИЛИ, выход которого подключен к вторым управляющим входам -in групп триггеров п-разрядного регистра и к. первому управляющему входу блока асинхронного преобразования и задержки кода, второй управляющий вход которого является входом установки в исходное состояние устройства, группа из управляющих выходов блока асинхронного преобразования и задержки кода подключена (Л соответственно к третьим управляюпщм входам -И групп триггеров п-раз рядного регистра, информационные выходы и первый управляющий выход блока асинхронного преобразования и задержки кода подключены к информационным входам и управляющему входу синхронизации запоминающего устройства, а второй его управляющий выход является выходом конца преобразования координат события. 2. Устройство по п.1,отличающееся тем, что блок асинхронного преобразования и задержки кода содержит первый и второй приоритетные шифраторы, -Гп мультиплексоров, дешифратор, две группы из -{rf элементов И, два элемента И, группу из 4п элементов задержки, четьфе элемента задержки, -yln разрядный ре-гистр, одновибратор, две группы из - элементов ИЛИ, причем входы мультиплексоров являются первой группой из п входов блока асинхронного пре

1

Изобретение относится к области экспериментальной ядерной физики и может быть применено в электронных схемах ядерного излучения и в других регистрирующих годоскопических сиетемах. Известно устройство регистрации информации с координатной камеры содержащее п идентичных каналов регистрации. Каждый канал регистрации содержит усилитель, регулируемый элемент задержки, например одновибратор, который одновременно выполняет функции формирователя сигналов, и запоминающий элемент, выполненный на D-триггере. Причем выход элемента за держки соединен с входом синхронизации триггера, а D-вход соединен с выходом решающего устройства, в ко- . тором вырабатывается сигнал регистрации полезного события.. Недостаток такого устройства состоит в том, что дпя его реализации требуется большее количество электронного оборудования, так как информация в устройстве регистрируется в унитарном позиционном коде.

Наиболее близким по техническому решению к изобретению является устройство регистрации информации с координатной камеры,, содержащее п входных усилителей, п-разрядный регистр, разделенный на - групп триг3геров, и запоминающее устройство, со держащее информационные входы и два управлянщих входа: синхронизации и стробирования, причем выходы входных усилителей подключены к первым управляющим входам соответствующих им -(п групп триггеров п разрядного регистра. Причем прямой выход каждого триггера п-разрядного регистра подключен к входу первого элемента И, второй вход которого соединен с входами второго и третьего элементов И, а выход подключен к входу шифратора, инверсный выход соединен с вторым входом второго элемента И и с входом первого элемента ИЛИ, выход которого подключен к общему управляющему входу триггеров регистра и через элемент задержки с вторым входом третьего элемента И, выход которого через второй элемент ШШ соединен с третьим зт равляющим входом соответствующего ему триггера регистра, второй вход второго элемента ШШ соединен с общим входом установки на О устройства, а выход второго элемента И подключен к вторым входам второго и третьего элементов И следующего разряда регистра. Работает прототип следующим образом. В исходном состоянии с выхода пер вого элемента ИЛИ, входы которого со единены с выходами всех триггеров регистра, подается разрешающий уровень на вторые управляюпще входы триггеров регистра. Сигналы от нитей камеры после усиления поступают на первые управляющие входы соответствующих им триггеров регистра и последние устанавливаются на 1. Уровень с выхода первого элемента ИЛИ запрещает занесение новых данных на триг геры регистра. После этого на вторые входы элементов И самого младшего разряда подается сигнал опроса. Этот сигнал проходит через те разряды регистра, которые установлены на О. Если же в первом по порядку триггере содержится 1, то этот сиг нал проходит открытый первый элемент И и далее поступает на вход шифратора, на выходе которого формируется двоичный код. Далее на вход третьего элемента И подается следующий им-. ; пульс, который проходит тот элемент И, проходит второй элемент ИЛИ и устанавливает на О триггер данного 814 разряда. Для преобразования следующей координаты подается следующий управляющий импульс на самый младший разряд регистра. Основной недостаток прототипа состоит в том, что дпя его реализации требуется большое количество электронного оборудования, а также его малое быстродействие. Цель изобретения - увеличение быстродействия с одновременным сокращением электронного оборудования. Указанная цель достигается тем, что в устройство регистрации информации с координатной камеры, содержащее п входных усилителей, п-разрядный регистр, разделенный на -JiT групп триггеров, запоминающее устройство, содержащее информационные входы и два управляющих входа: синхронизации и стробирования, причем выходы входных усилителей подключены к первым управляющим входам соответствующих им групп триггеров п-разрядного регистра, введены блок асинхронного преобразования и задержки кода, содержащий первую группу из п входов, вторую группу из входов, два управляющих входа, группу из управлякицих выходов, информационные выходы и два управляющих выхода, а также (-fti- -) элементов ИЛИ, имеющих каждый - входов, причем выходы триггеров п-разрядного регистра подключены к первой группе из п входов блока асинхронного преобразования и задержки кода, выходы каждой группы триггеров подключены к входам соответствующих им -|п элементов ШШ, выходы которых соединены со второй группой из входов блока асинхронного преобразования и задержки кода и к входам (-Гп+1)-элемента ИЛИ, выход которого подключен к вторым управляющим входам -Jp групп триггеров п-г-разрядного регистра и к первому управляющему входу блока асинхронного преобразования и задержки кода, второй управляющий вход которого является входом установки в исходное состояние устройства, а группа из - управляющих выходов блока асинхронного преобразования и задержки кода подключена соответственно к третьим управляющим входам -fS групп триггеров п-разрядного региста, а информационные выходы и пер5 1

вый управляющий выход блока асинхронного преобразования и задержки кода подключены к информационным входам и управляющему входу синхронизации запоминающего устройства, а второй его управляющий выход является выходом конца преобразования координат события.

Поставленная цель достигается также тем, что блок асинхронного преобразования и задержки кода содержит первый и второй приоритетные шифраторы, 4гг мультиплексоров, дешифратор, две группы из п элементов И, два элемента И, группу изЧп :элементов задержки, четыре элемента задержки, -Ir разрядный регистр, одновибратор, две группы из 4п элементов ИЛИ, причем входы мультиплексоров являются первой группой из п входов блока асинхронного преобразова-: ния и задержки кода, а входы первого приоритетного шифратора - его второй группой из In входов, выходы первого приоритетного шифратора соединеш; с входами дешифратора, с группой управляюш 1Х (адресных)входов всех мультиплексоров и являются информационными выходами старших разрядов координат, выходы мультиплексоров подключены к первым управляющим входам соответствующих триггеров rin разрядного регистра, прямые выходы которых подключены к входам второго приоритетного шифратора и к первым входам соответствуюш 1Х элементов И первой группы, выходы которых через соответствующие им элементы ИЛИ первой группы соединены с вторыми управляющими входами соответствуюш х триггеров -|т1 разрядного регистра, инверсные выходы которых через соответствующие элементы задержки первой группы из элементов задержки подключены к первым входам элементов И второй группы, вторые входы элементов И обеих групп подключены к вьпсоду элемента И второй группы предыдущегб разряда, а вторые входы элементов И, относящиеся к триггеру -(гГ разрядного регистра наивысшего приоритета, через первый элемент задержки соединены с управляющим входом второго приоритетного шифратора и с выходом первого элемента И, первый вход которого через второй элемент задержки соединен с первым управляющим выходом второго приоритетного шифрато816

ра, первый управляющий выход первого приоритетного шифратора подключен к первому входу зт- -рого элемента И, к входу одновибратора и через третий элемент задержки - к второму входу первого элемента И, выход второго элемента И соединен с управляющим входом одновибратора и с управляющим входом дешифратора, второй вход второго элемента И через четвертый элемент задержки подключен к второму управляющему выходу второго приоритетного шифратора, выход одновибратора соединен с управляющим (стробируюш да) всех мультиплексоров, выходы дешифратора соединены с входами соответствующих им элементов ИЛИ второй группы, вторые входы всех элементов ИЛИ первой и второй групп объединены

и соединены с вторым управляющим входом блока, выходы второго приоритетного шифратора являются информационнь ми выходами младших разрядов координат события, управляющий вход первого приоритетного шифратора является первым управляющим входом блока, а его второй управляющий выход является выходом конца преобразования координат события, а выход первого

элемента И является первым управляю щм выходом блока.

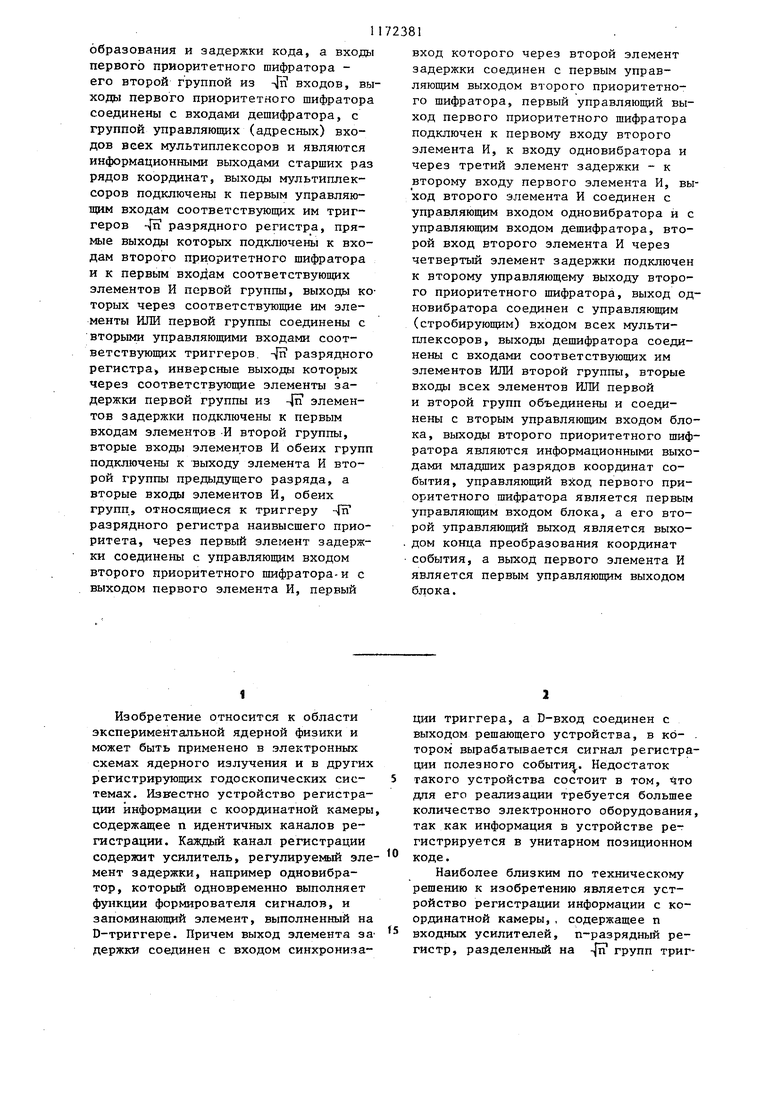

На фиг.1 приведена структурная схема устройства регистрации инфор1 1ации с координатной камеры; на

фиг.2 - структурная схема асинхронного преобразования и задержки кода. На фиг.1 приведена схема устройства для случая, когда число входов . Входы пронумерованы от О до

3-0...3-16 элементов ИЛИ, 4 - блок асинхронного преобразования и задержки кода, 5 - запоминающее устройство 6, первый управляющий вход блока 4, 7 - второй управляющий вход

блока 4, 8 - информационные выходь блока 4, 9 - первый управляющий выход блока 4, 10 - второй управляющий выход блока 4, 11 - третий управляющий вход устройства (управляющий вход

стробирования блока записи),(12-0... 12-15) группа из 16 управляющих выходов блока 4. Входы усилителей подключены к нитям координатного детектора. 7 Выхода усилителей 1 соединены с пер выми управляющими входами соответст вующих триггеров регистра 2. Тригге ры регистра разделены на равные гру пы по 16 триггеров в группе. Выходы триггеров подключены к первой групп из 256 входов блока асинхронного пр образования и задержки кода. Выходы триггеров каждой группы соединены тавсже с входами соответствующих им элементов ИЛИ 3-0...3-15, выходы ко торых подключены к второй группе из 16 входов блока асинхронного преобразования и задержки кода и к входам элемента ИЛИ 3-16. Выход элемента ИЛИ 16 соединен с вторыми п управляющими входами триггеров регистра (на фиг.1 показано одной связью на каждую группу). Если хотя бы на одиом из триггеров регистра 2 содержит ся информация, то на выходе элемента ИЛИ 3-J6 вырабатывается сигнал запрещающий занесение данных на регистр. На управляющий вход 7 подается сигнал сброса блока 4 в исходное состояние (от внещних устройств). На управляющий вход 6 подается сигнал Пуск с выхода элемента ИЛИ 3-16. Информационные выходы 8 блока 4 соединены с информационными входами запоминающего устройства 5. На первом управляющем выходе 9 вырабатываются синхроимпульсы, необходимые для записи данных в запоминающее устройство. На управляющем выходе 10 вырабатывается сигнал конца преобразования На управляющий вход 11 подаете сигнал медленного сброса (строб от внещ них устройств), что позволяет записывать в запоминающее устройство только полезные события. Группа управляющих выходов 12-0...12-15 подключена соответственно к тр-етьим управляющим входам групп триггеров регистра (ко всем триггерам в группе). Число выходов в группе 12 соответствует числу групп триггеров. Устройство работает следующим образом. В исходном состоянии все триггеры регистра 2 устаиорлены на О сигналом Сброс через блок 4 и группу управляющих выходов 12-0...12-15. С выхода элемента ИЛИ 16 на вторые управляющие входы триггеров подается разрешающий уровень напряжения. Импульсы от нитей координатной камеры после усиления поступают на пер3818вые управляющие входы соответствующих триггеров. Для простоты положим, что сигнал поступил от первой проволочки, т.е. на вход 1-1. Тогда первый триггер 2-0-1 в нулевой группе 2-0 установится на 1. Сигнал с выхода этого триггера через элементы ИЛИ 3-0 и 3-16 поступает на вторые управляющие входы триггеров регистра 2 и блокирует занесение новых данных. Кроме того, сигнал с выхода триггера 2-0-1 поступает на вход блока асинхронного преобразования и задержки кода. На вход этого блока поступает также сигнал с выхода элемента ИЛИ 3-0, В блоке 4 по сигналу Пуск происходит преобразование унитарного кода в обыкновенный двоичный код, который поступает на информационные входы запоминающего устройства 5; Одновременно на выходе 9 вырабатывается синхроимпульс, с помощью которого двоичный код записывается в запоминающее устройство. Причем запись происходит лишь в том случае, если синхроимпульс совпадает с импульсом медленного строба, который поступает на вход 11 от решающего внешнего устройства, которое определяет полезность регистрируемого события. После выработки синхроимпульса на выходе 12-0 вырабатывается импульс, с помощью которого устанавливаются на О триггеры группы 2-0, а на выходе 10 формируется импульс конец преобразования и устройство готово к регистрации новых данных. Если бы в группе 2-0 бьши установлены на 1 все триггеры, то импульс установки на О поступает после преобразования всех 16 координат. Следует отметить, что в блоке 4 выполняется не только преобразование координат, но и регулировка задержки поступления кода на входы запоминающего устройства 5, которая необходима для подготовки совпадения сигнсшов, поступаемых с выхода 9 и на вход 1-1.. На 4ИГ.2 приведена структурная схема блока асинхронного преобразования и задержки кода дпя случая, когда число входов . Здесь приняты следующие обозначения: 0...255ходе. мультиплексоров 13-0... 13-15 ли первая группа из 256 входов блоа 4,14-0...14-15 - входы первого риоритетного шифратора 15 или вто9 .

рая группа из 16 входов блока 4; 16дешифратор, 17-0... 17-15 и 18-0... 18-15 - элементы И первой и второй групп; 19-0...19-15, 19-16...19-31 вторая и первая группы элементов ИЛИ 20-0.. ..20-15-16-разрядный регистр; 21 - второй приоритетный шифратор; 22, 23 - первый и второй элементы И; 24 - одновибратор, 25-0... 25-15 - группа из -jn элементов задержки; 26, 27, 28, 29 - соответственно третий, первый, второй и четвертый элементы, задержки; 30 - информационные выходы старших разрядов координат; 31-34 - группа управляюш 1х (адресных) входов мультиплексоров; 35 - Первый управляющий выход первого приоритетного шифратора; 36 - управляющий (стробируемый) вход мультиплекторов; 37 - первый управляющий выход второго приоритетного шифратора; 38.- управляющий вход второго приоритетного шифратора; 39 - ВЫХОДА младших разрядов координат; 40 - второй управляющий выход второго приоритетного шифратора. На фиг.2 приведена также нумерация входов и выходов, которая совпадает с нумерацией на фиг.1:6- первый управлянэдий вход блока 4 - сигнал пука первого приоритетного шифратора

15; 7 - второй управляющий вход блока 4 - вход установки на О триггерор регистров 20 и 2; 9 - первый управляющий выход блока 4; 10 - второй управляющий выход блока 4; 12-0... 12-15 - группа из - управляющих выходов блока 4. Информационные выходы старших 30 и младших 39 разрядов координат в Сумме составляют выходы 8 блока 4 на фиг.1. Входы 14-0...14-15 соединены с выходами элементов ИЛИ 3-0...3-15 (фиг.1). Выходы первого приоритетного шифратора 15 соединены с входами дешифратора 16, группой управляющих (адресных)входов 31-34 мультиплексоров 13-0... 13-15 и одновременно являются выходами старших разрядов 30 координат. Входы 0-255 мультиплексоров подключены к выходам триггеров 256-разрядного регистра (2-0, 2-15, фиг.1). Выходы мульти-г плексоров соединены с первыми управляющими входами триггеров 16 - разрядного регистра 20-0...20-15. Прямые выходы триггеров этого регистра соединены с входами второго приоритетного шифратора 21 и с первыми вхо2381.10

дами элементов И 17-0...17-15 первой группы. Наиболее высокий приоритет имеет триггер 20-0. Поэтому вторые входы элементов И 17-0 и 18-0 через элемент задержки 27 соединены с выходом элемента И 22, на котором вырабатываются сигналы опроса регистра 20-0...20-15. Инверсные выходы триггеров через группу элементов задержки 25-0...25-15 соединены с вторыми входами элементов И 18-0... 1815 второй группы. Выход элемента И второй группы ш-го разряда подключен к вторым входам элементов И первой 5 и второй группы следующего разряда.Выхода первых элементов И через группу элементов ИЛИ 19-16... 19-31 соединены со вторыми управляющими входами триггеров регистра. Вторые 0 входы всех элементов ИЛИ 19-0... 1931 подключены к общему входу 7 установки на О всех триггеров, включая и входной регистр 2 (фиг.1). Первые входы группы элементов ИЛИ 19 О... 15-15 соединены с выходами дешифратора 16, а их выходы 12-0...12-15 подключены к третьим управляющим входам соответствуюш 1х групп триггеров входного регистра 2 (фиг.1). Ут1рав0 выход 35 соединен с первым входом элемента И 23 и через задержки 26 подключен к первому входу элемента И 22,второй вход которого через элемент задержки 28 соединен с 5 первым управляющим выходом 37 второго приориТетного шифратора 21, второй управляющий выход которого 40 через элемент задержки 29 соединен со вторым входом элемента И 23, выход 40 которого подключен к управляющим входам одновибратора 24 и дешифратора 16. Выход одновибратора 24 соединен с общим управляющим входом 36 мультиплексоров . Выходы 39 являются выходами младщих разрядов координат, а на управляющем выходе 10 вырабатывается сигнал, по которому можно судить о. конце регистрации и преобразования всех координат данного события. На 50 управляющий вход 6 подается сигнал Пуск, по которому начинается работа блока. Работает устройство следуннцим образом. Допустим, что сигналы поступили от 18 и 34 нитей, что 55 соответствует двоичным кодам 0001001Q и01010100. Эти коды с выходов триггеров регистра поступают на соответствующие входы мультиплексоров 130...13-15 и с вь:ходов элементов ИЛИ 3-1 и 3-2 поступают на входы 14-1 и 14-2 первого приоритетного шифратора 15. В стандартном исполнении приоритетный шифратор, например, 155 ИВ1, помимо информационных входов - выходов имеет также управляющий вход, на который попадает сигнал Пуск, и два управляющих выход На первом из них в течение времени преобразования данных вырабатывается импульс соответствующей ширины. На втором управляющем выходе импульс вырабатывается всякий раз, когда на его входах устанавливается код соотвествующий нулю. После поступления сигнала Пуск на вход 6 на выходах 30 формируется код 0001, который соответствует двоичному номеру группы нитей, в которой имеется хотя бы одна сработавшая нить. Этот код поступает на выходы устройства в качест ве старших разрядов координаты сработавшей нити и на общие управляющие (адресные) входы 31-34 мультиплексоров 13-0...13-15. Одновременно с пер вого управляющего,выхода 35 приоритетного шифратора 15 вырабатывается импульс, который запускает одновибра тор 24, сигнал с выхода которого пос тупает на общий управляющий (стробирующий) вход 36 мультиплексоров 130...13-15. В результате триггер 20-1 устанавливается на 1 импульсом, поступившим с выхода мультиплексора 131. Кроме того, импульс с выхода 35 через элемент задержки 26 поступает на вход элемента 22, который открыт по второму входу разрешающим уровнем поступившим с первого управляющего выхода 37 второго приоритетного шифратора 21 через элемент задержки 28. Импульсом с выхода элемента И 22 раз решается работа второго приоритетного шифратора (управляющий вход 38), и на его выходах 39 формируется двоичный код 0001, который совместно с кодом, сформированным на выходах 30, образует двоичный код номера сработавшей нити 000100102 18,0 . Одновременно на выходе 37 уровень меняется на противоположньш и на выходе 9 формируется импульс,который сопровождает код координаты в качестве синхроимпуль са. Кроме того, этот импульс через элемент задержки 27 поступает на входы элементов И 17-0 и 18-0. Поскольку триггер 20-0 находится в нулевом со8112стоянии, то элемент И 17-0 закрыт, а элемент И 18-0 открыт. Импульс проходит этот элемент и поступает на входы элементов И 17-1 и 18-1,Триггер 20-1 находится в состоянии 1, поэтому импульс проходит элемент И 17-1, проходит элемент ИЛИ 19-17 и устанавливает на О триггер 20-1. Изменение состояния триггера 20-1 приходит с задержкой на величину за-. держки элемента 25-0, поэтому импульс, поступающий с выхода элемента 18-0, дальше по цепи не проходит. Поскольку все триггеры установлены на О, то.на втором управляющем выходе 40 приоритетного шифратора 21 вырабатывается импульс, который через элемент задержки 29 поступает на вход элемента И 23. На втором входе этого элемента поддерживается разрешающий уровень, поступаюший с выхода 35 . С выхода элемента И 23 импульс поступает на управляющий вход дешифратора 16, на выходе 12-1 которого вырабатывается импульс, с помощью которого устанавливаются на О триггеры первой группы входного регистра. Сигнал Пуск на входе 6 присутствует все время, пока идет регистрация всех координат одного события . Поэтому после установки на О триггеров первой группы на вы ходах 30 формируется код 0010, со- . ответствующий наличию единицы во второй группе триггеров входного регистра. Этот код поступает также на уп7 равляющие входы 31-34 мультиплексоров. Несколько ранее после установки на О триггера 20-1 на управляющем выходе 40 второго приоритетного шифратора 21 вырабатывается импульс, который через элемент задержки 29 поступает :ш управляющий вход одновибратора 24. В результате сигнал на выходе одновибратора модулируется по амплитуде и фронтом этого сигнала, поступающего на общий управляющий вход 36 мульти1тлексоров 13-0... 13-15 на триггер 20-2 заносится 1. За счет задержки на элементе 28 на управляющем входе 38 продолжает оставаться разрешающий уровень и на выходах 39 формируется код 0100, который совместно с кодом 0010 образует код 00100100 34,р следующей сработавшей нити. Одновременно на управляющем выходе 37 изменяется уровень напряжения и на выходе 9 формируется им13пульс, который проходит элементы И 18-0, 18-1, 17-2, элемент ИЛИ ISIS и срабатывает на О триггер 202. Аналогично вьппеописанному на вых де элемента И 23 формируется импульс, котсрьй разрешает работу дешифратора 16, на выходе которого 12-2 формируется импульс, с помощью которого устанавливается на О вто рая группа триггеров входного регистра. В результате на втором управляющем выходе 40 второго приоритетного шифратора 21 вырабатывается импульс Конец регистрации координат одного события, Одновременно снимается разрешающий уровень на уп равляющем выходе 35 и на управляюще входе 6. Далее цикл регистрации координат события повторяется. На управляющий вход 7 перед началом рабо 155ИВ1 155ТМ2 155КП1 155ВДЗ 426 3408 155ЛАЗ 1 1 155ЛН1 1 I 155АГЗ

492

247

Итого:

При оценке быстродействия будем исходить из того, что в обоих устройствах используются ТТЛ микросхемы 531.серии, которые имеют следующие задержки на элемент: И, ИЛИ-5нс, триггер-10 НС, дешифратор - 12 не, мультиплексор - 12 не, приоритетный шифратор - 12 НС.

В прототипе для регистрации каждой координаты подается тактовый импульс. При числе входов такто184

58

3922

51

вый импульс в худшем случае проходит 256 элементов типа И, каждый из которь1х имеет задержку 5 не. Итого максимальная величина задержки Т составляет примерно 1,3 МКС. Поэтому для надежной работы тактовая частота не превышает 800 кГц. В настоящем устройстве максимальная величина задержки импульса опроса равна -Ыт, где t - задержка на одном элементе, равная 5 не. Таким образом, макси81ты устройства подается сигнал установки на О. С помощью элемента задержки 26 имеется возможность плавно регулировать время поступления двоичных координат с выходов 30,39 на запоминающее устройство, где с помощью сигнала- медленного строба происходит регистрация только координат полезных событий. В таблице приведены данные о количестве стандартных микросхем (в корпусах), необходимых для построения прототипа и настоящего устройства. Видно, что экономичность настоящего устройства существенно повышается с увеличением числа входов. Так, при в настоящем устройстве число микросхем более чем в 20 раз меньше5 чем в прототипе.

мальная величина задержки распространения импульса опроса составляет всего 80 НС. Величина Т вносит основной вклад при определении скорости работы как в прототипе, так и в настоящем решении. Время, требуемое дпя подключения группы триггеров, складывается из задержки в приоритетном шифраторе и мультиплексоре и это время равно 24 НС. В силу свойства работы приоритетного шифратора время занесения -кода из последней группы триггеров, где по нашему предположению содержатся данные, не превышает 24 НС. Таким образом.при наиболее неблагоприятных условиях быстродействие настоящего устройства на.много выге, чем в прототипе. Предположим, что сработало 16 нитей по одной в каждой группе. Тогда в прототипе для регистрации всех координат необходимо подать 16 тактовых импульсов, что составляет 22 мкс. В настоящем устройстве для этих же целей потребуется 16x22+16x80 1,7 МКС, т.е. на порядок меньше. Такая эффективность настоящего устройства достигнута благодаря применению блока асинхронного преобразования и за держки кода , для работы которого не требздатся тактовые импульсы.

1Z-15

.1

| Басиладзе С.Г | |||

| Быстродействую,щая ядерная электроника, Энергоиздат М., 1982, с.141 | |||

| P.R.Bevington а.о | |||

| Fast САМАС MWPC readont System IEEE Transaction on Nuclear Science | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

Авторы

Даты

1986-09-07—Публикация

1983-12-22—Подача