Изобретение относится к области автоматики и вычислительной техники.

Известно запоминающее устройство (ЗУ), содержащее регистр адреса, дешифратор выборки, накопитель на ферритовых сердечниках, регистр числа, усилители считывания и дешифратор полярности сигналов fl.

Наиболее близким к предложенному устройству является ЗУ 21, содержащее дешифратор выборки, выход которого подключен ко входам сдвигающего регистра и блока управления, один из выходов блока управления подключен к одному из входов адресных и адресно-разрядных дешифраторэв и входу дешифратора полярности сигналов, выход которого подключен к другим входам адресных и адресно-разрядных дешифраторов, выходы которых соединены с первыми входами формировате- лей токов, выходы которых подключены ко входам накопителя, а выходы накопителя -ко входам усилителей считывания, регистр числа, выходные усилители и элемент задорж-хи. один из входов которого

подключен к одному из входов деши4 атора выборки и к другому выходу блока управления, а выход элемента задержки подключен к одним из входов выходных усилителей.

Такое устройство невозможно использовать в вычислительных системах с различной тактовой частотой и нельзя отключить от вычислительной системы при проведении профилактических работ ЗУ. Кром того, в нем не обеспечивается защита информации при уменьшении напряжения питания формирователей тока ниже допустимого предела и защита выходных каскадов формирователей тока при ложной дешифрации, что снижает надежность устройства.

Целью изобретения является повышение надежности устройства.

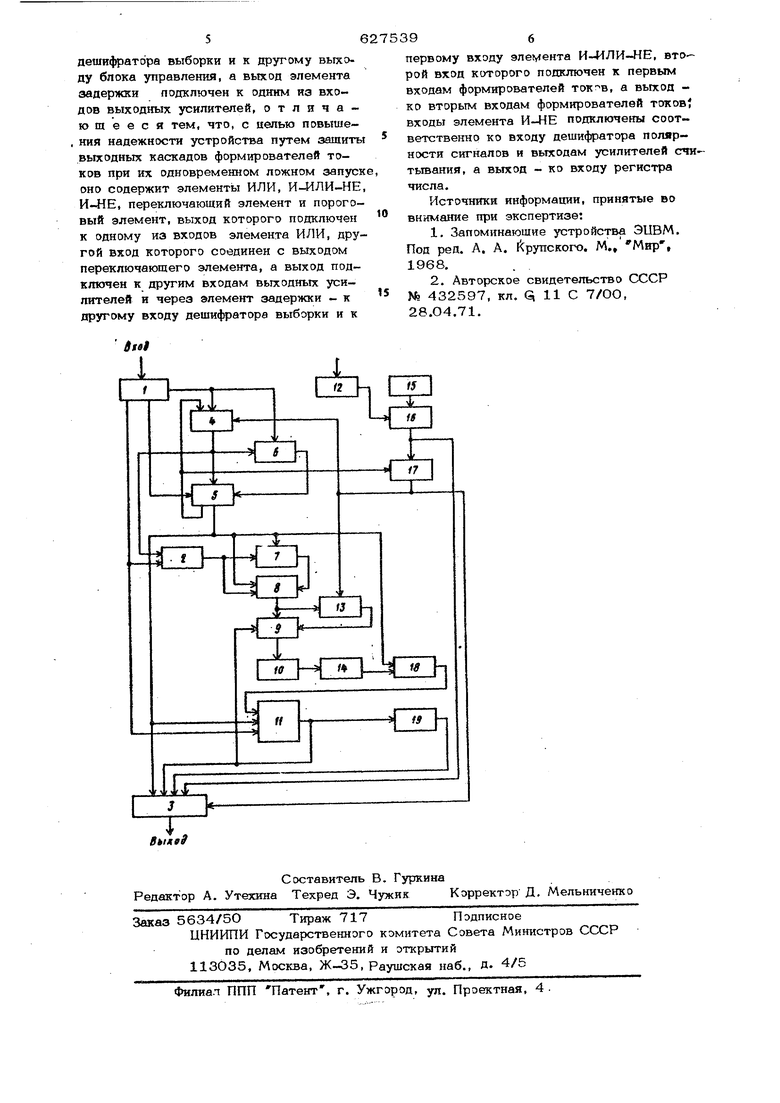

Поставленная цель достигается тем, что предложенное устройство содержит элементы ИЛИ, И-ИЛИ-НП, И-FIE, переключающий элемент и пороговый элемент выход которого подключен к одному из входов элемента ИЛИ, другой вход которого соединен с выходом переключающего элемента, а выход подклго чен к Другим входам выходных усилителей и через элемент задержки - к другому входу дешифратора выборки и к пер вому входу элемента И-ИЛИ-НЕ, второй вход которого подключен к первым входам формирователей токов, а врлход - ко вторым входам формирователей токов. Вх ды элемента И-НЕ подгспючёны соотвестп венно ко входу дешифратора полярности сигналов и выходам усилителей считыван а выход - ко входу регистра числа. На чертеже представлена структурная схема ЗУ, ЗУ содержит входные усилители 1, ре гистр адреса 2, выходные усилители 3, дешифратор выборки 4, блок управлетгя 5 сдвигающий регистр 6, дешифратор поляркости сигналов 7, адресные и адресноразрядные дешифраторы 8, формирователи токов 9, накопитель 10, регистр числа 11, пороговый элемент 12, элемент И- ИЛИ-НЕ 13, усилители считывания 14, переключающий элемент 15, элемент ИЛИ 16, элемент задержки 17, элемент , 18 и блок контроля 19. Устройство работает следующим образом. При обращении к устройству, если оно свободно, а сигнал Авария отсутствует на выходе элемента задержки 17, сигнал с выхода дешифратора выборки 4 запускает блок управления 5, сдвигающий регистр 6 и записывается адрес ячейки памяти в регистр адреса 2. При этом по сигналу с дешифратора выборки 4 устройство переходит в состояние Занято. Блок управления формкфует все синхроимпульсы, исполъ,эуемые в работе ЗУ. nocTyntremHft адрес дешифрируется дешифратором полярности сигналов 7 а также адресными и адресно-разрядными дешифраторами 8. При этом согласно адресу ячейки памяти выбираются соответствующие формирователи токов 9. Фopм фoвaтeли токов 9 формируют полутоки чтения, протекающие по выбранным координатньпу шинам накопителя Ю. Считанные сигналы с выхода накилителя 10 поступают на входы усилителей считьгеания 14, где усиливаются, стробируют ся элементом И-НЕ 18 и заносятся в ре. гистр числа 11. В режш.1е запись форм рователи токов 9 формируют полутоки записи, протекающие по выбранным координатным шинам накопителя 10,в результате чего информация записывается в накопитель 10. 6 94 При выполнении операцик чтение считанная информация выдается через выходные усилители 3 в вычислительную систему. Блок контроля 1C контролирует принятую информацию из вычислительной системы в регистр числа 11 на четность. При обнаружении ошибки вырабатывается сигнал Ошибка , который через выходные усилители 3 выдается в вычислительную систему. . По окончании полуцикла записи устройство переходит в состояние Свободно и может принимать следующее обращение к устройству. Технико-экономический : эффект изобретения заключается в том, что элемент И-НЕ 18 и сдвигающий регистр 6 обеспечивают работоспособность устройства и вычислительной системы при изменении тактовой частоты от О до 3 мггц. Пороговый элемент 12, переключающий элемент 15, элемент ИЛИ 16 и элемент задернжи 17 обеспечивают сохранность информации при выходе за допуст1-1мые предел :, контролируемых источников питания, возможность перезаписи информации в другое ЗУ при работе с вычислительной системой по сигналу Авария и позволяют улучщить условия эксплуатации вычислительной системы, так как аопускается откл очение устройства ка профилактику без останова и выключения вычислительной системы. Элемент И-ИЛИ-НЕ 13 блокирует работу выходных каскадов адресных и адресно-разрядгш х формирователей токов 9 при одновременном появлении запускающих сигналов на их входах. формула изобретений Запоминающее устройство, содержащее дешифратор выборки, выход которого под- ключе{ ко входам сдвигающего регистра и блока управления, один из выходов блока управления подключен к одному из входов адресных и адресно-разрядных дешифраторов и входу дешифратора полярности сигналов, выход которого подключен к другим входам адресных и адресно-разрядных дешифраторов, выходы которых соединены с первыми входами формирователей токов, выходы которых подключены ко входам накопителя, а выходы накопителя - ко входам усилителей считывания, регистр числа, выходные усилители и элемент задержки, одик из входов которого подключен к одному из входов

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| Запоминающее устройство с сохранением информации при аварийном отключении питания | 1977 |

|

SU693441A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Запоминающее устройство | 1974 |

|

SU536524A1 |

| Запоминающее устройство | 1977 |

|

SU733021A1 |

| Запоминающее устройство | 1971 |

|

SU479151A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Запоминающее устройство типа 2,5 д | 1981 |

|

SU999105A1 |

| Запоминающее устройство | 1978 |

|

SU799001A1 |

Авторы

Даты

1978-10-05—Публикация

1975-04-21—Подача