(5) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ТИПА 2,5 Д

| название | год | авторы | номер документа |

|---|---|---|---|

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Логическое запоминающее устройство | 1971 |

|

SU443411A1 |

| Устройство для контроля матриц памяти на цилиндрических магнитных пленках с неразрушающим считыванием информации | 1986 |

|

SU1387045A1 |

| Магнитное оперативное запоминаю-щЕЕ уСТРОйСТВО | 1979 |

|

SU841039A1 |

| Запоминающее устройство | 1974 |

|

SU536524A1 |

| Запоминающее устройство | 1977 |

|

SU733021A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Запоминающее устройство | 1971 |

|

SU479151A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1124384A1 |

1

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство типа 2,5 Д, содержащее магнитный накопитель, адресный и адресно-разрядные дешифраторы, регистр адреса, регистр информации и усилители считывания l 1.

Недостатками этого устройства являются большая потребляемая мощность , и низкая надежность.

Наиболее близким к Предлагаемому изобретению является запоминающее устройство -типа 2,5,Д, содержащее ,5 магнитный накопитель, адресно-разрядные шины, выборки которого подключены в каждом разряде к отдельным адресно-разрядным дешифраторам, регистр адреса и регистр информации 2. 20

Недостатком известного устройства является низкая надежность обусловленная тем, что при записи и считывании возбуждаются формирователи тока

в каждом разряде адресно-разрядных цепей.

Целью изобретения является повышение надежности запоминающего устрюйства.

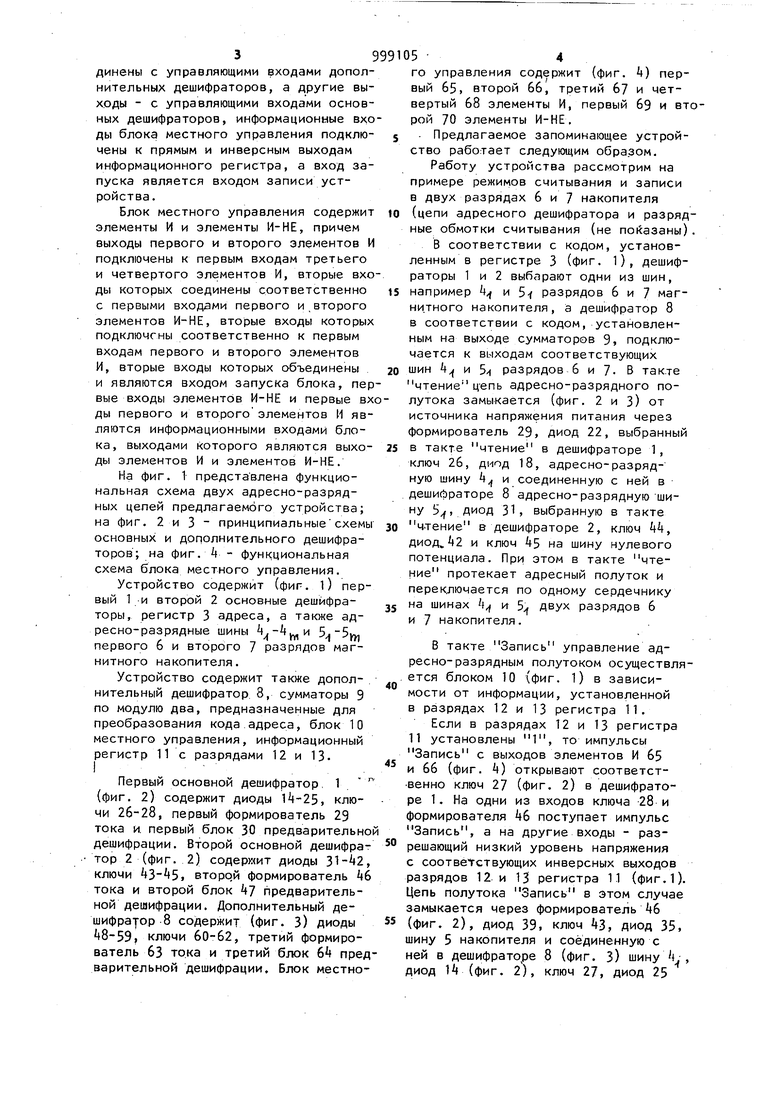

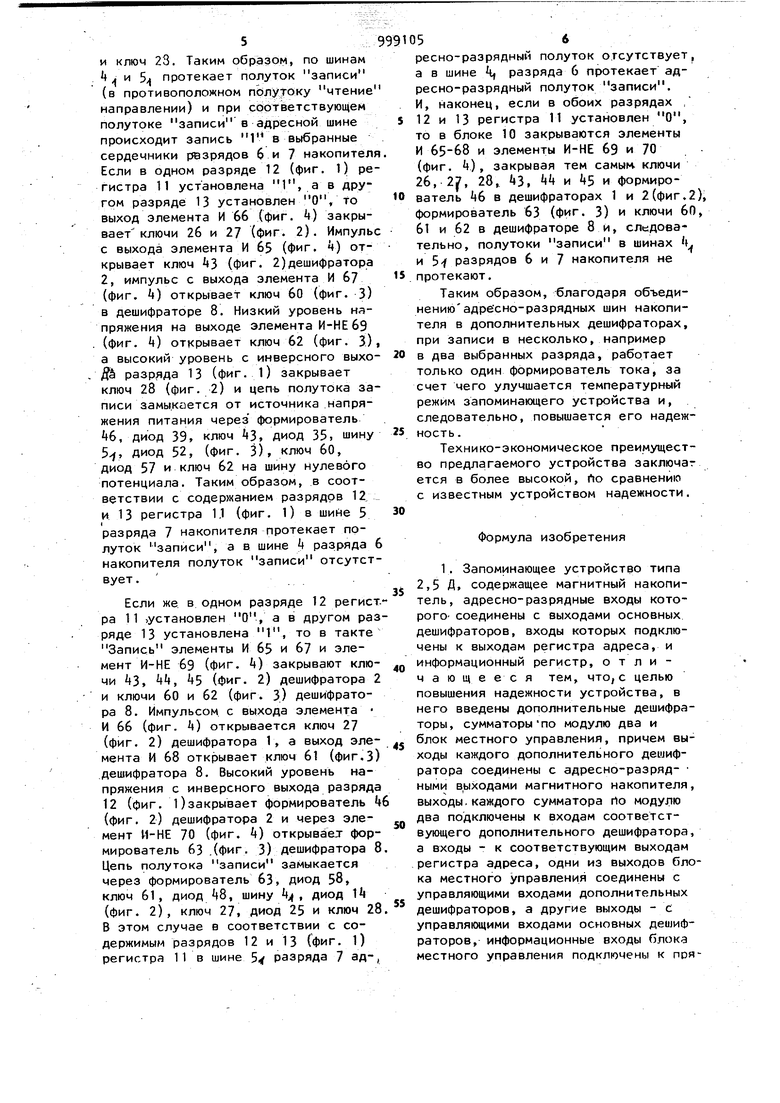

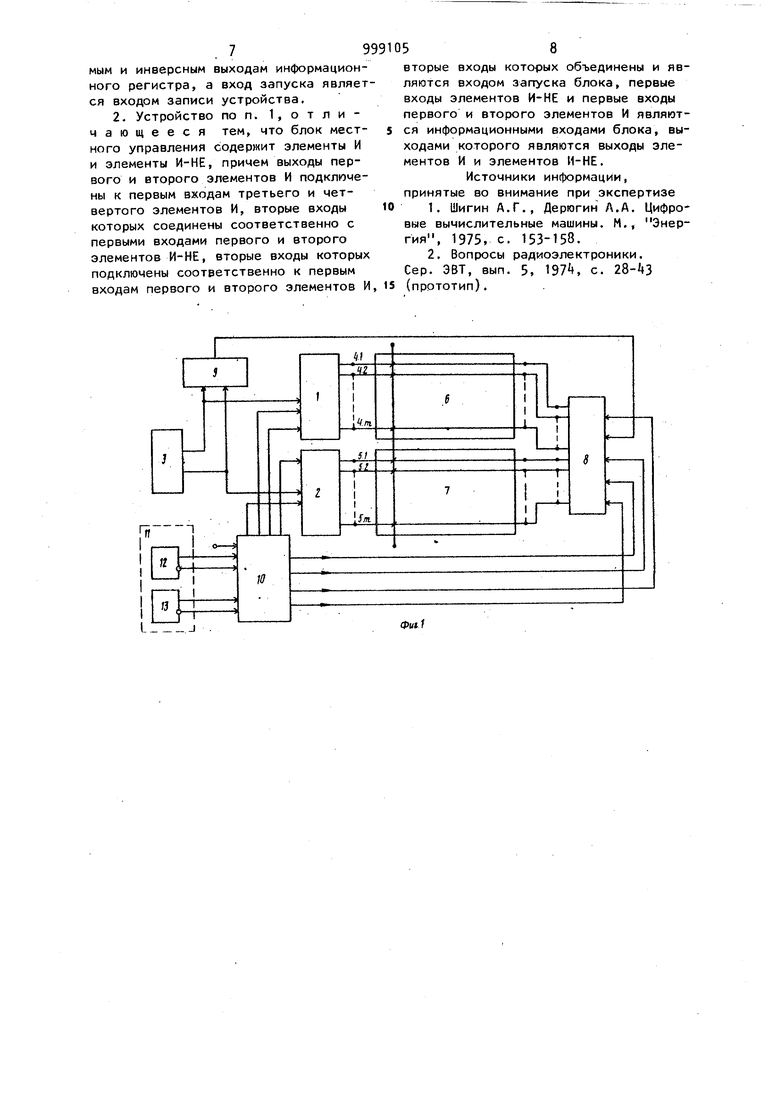

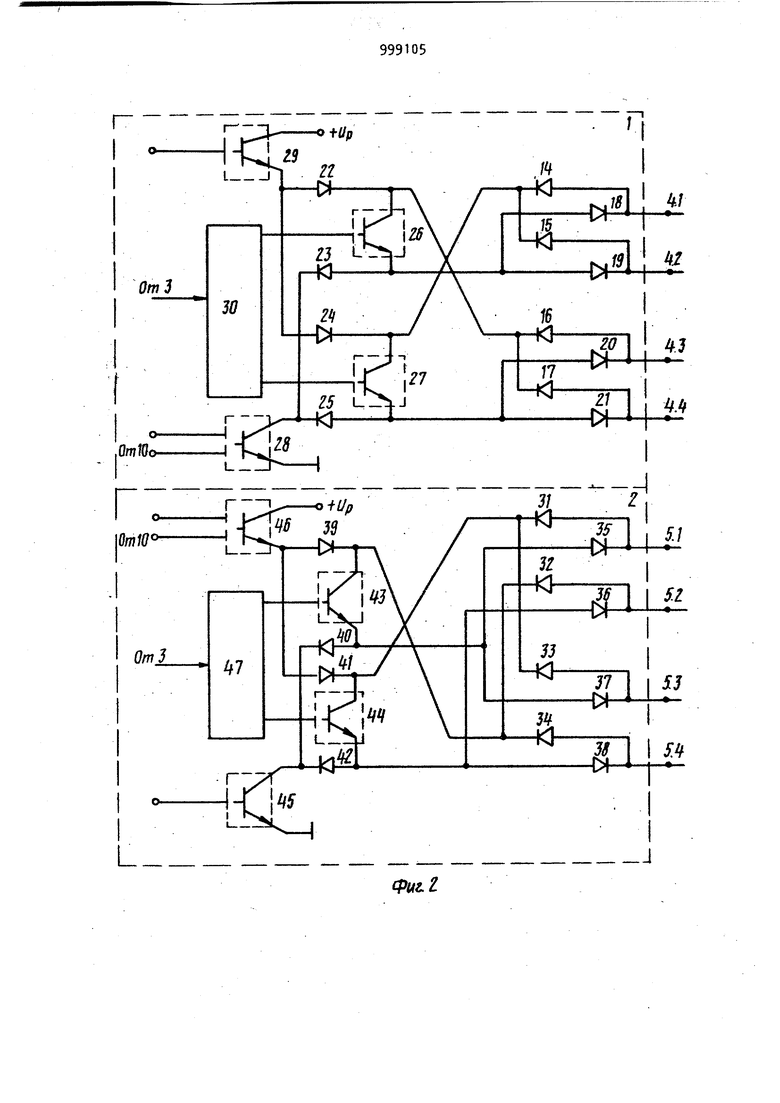

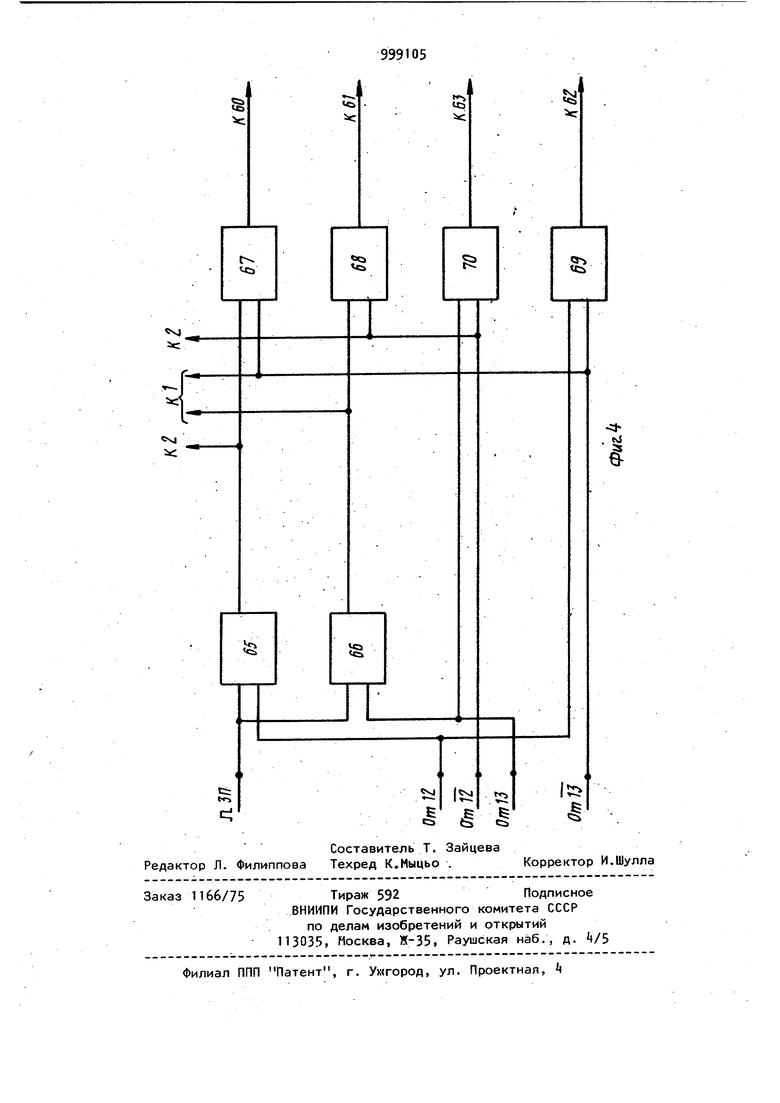

Поставленная цель достигается тем, что в запоминающее устройство типа 2,5 Д, содержащее магнитный накопитель, адресно-разрядные входы KOTOJJOго соединены с выходами основных дешифраторов, входы которых подключены к выходам регистра адреса, и информационный регистр, введены дополнительные дешифраторы, сумматоры по модулю два и блок местного управления, причем выходы каждого дополнительного дешифратора соединены с адресноразрядными выходами магнитного накопителя , выходы каждого сумматора по модулю два подключены к входам соответствующего дополнительного дешифратора, а входы - к соответствующим выходам регистра адреса, один из выходов блока местного управления соединены с управляющими входами дополнительных дешифраторов, а другие выходы - с управляющими входами основных дешифраторов, информационные вхо ды блока местного управления подключаны к прямым и инверсным выходам информационного регистра, а вход запуска является входом записи устройства. Блок местного управления содержит элементы И и элементы И-НЕ, причем выходы первого и второго элементов И подключены к первым входам третьего и четвертого элементов И, вторые вхо ды которых соединены соответственно с первыми входами первого и второго элементов И-НЕ, вторые входы которых подключены соответственно к первым входам первого и второго элементов И, вторые входы которых объединены и являются входом запуска блока, пер вые входы элементов И-НЕ и первые вх ды первого и второго элементов И являются информационными входами блока, выходами которого являются выходы элементов И и элементов И-НЕ. На фиг. 1 представлена функциональная схема двух адресно-разрядных цепей предлагаемого устройства; на фиг. 2 и 3 - принципиальныесхемы основных и дополнительного дешифраторов; на фиг. 4 - функциональная схема блока местного управления. Устройство содержит (фиг. l) первый 1 и второй 2 основные дешифраторы, регистр 3 адреса, а также адресно-разрядные шины у,и первого 6 и второго 7 разрядов магнитного накопителя. Устройство содержит также дополнительный дешифратор 8, сумматоры 9 по модулю два, предназначенные для преобразования кода адреса, блок 10 местного управления, информационный регистр 11 с разрядами 12 и 13. I Первый основной дешифратор. (фиг. 2) содержит диоды 14-25, ключи 26-28, первый формирователь 29 тока и. первый блок 30 предварительно дешифрации. Второй основной дешифратор 2 (фиг. 2) содержит диоды , ключи . второй формирователь 46 тока и второй блок 47 предварительной дешифрации. Дополнительный дешифрауор 8 содержит (фиг. 3) диоды 48-59, ключи 60-б2, третий формирователь 63 тока и третий блок 64 пред варительной дешифрации. Блок местноГО управления содержит (фиг. 4) первый б5. второй 66, третий 67 и четвертый 68 элементы И, первый б9 и второй 70 элементы И-НЕ. Предлагаемое запоминающее устройство работает следующим образом. Работу устройства рассмотрим на примере режимов считывания и записи в двух разрядах 6 и 7 накопителя (цепи адресного дешифратора и разрядные обмотки считывания (не показаны). В соответствии с кодом, установленным в регистре 3 (фиг. 1), дешифраторы 1 и 2 выбарают одни из шин, например 4 и 5-( разрядов 6 и 7 магни.тного накопителя, а дешифратор 8 в соответствии с кодом, установленным на выходе сумматоров 9 подключается к выходам соответствующих шин 4 и 5-1 разрядов 6 и 7- В такте чтение ц-епь адресно-разрядного полутока замыкается (фиг. 2 и 3) от источника напряжения питания через формирователь 29, диод 22, выбранный в такте чтение в дешифраторе 1, ключ 2б, диод 18, адресно-разрядную шину 4 и соединенную с ней в дешифраторе 8 адресно-разрядную шину 5, диод 31, выбранную в такте чтение в дешифраторе 2, ключ 44, и ключ 45 на шину нулевого потенциала. При этом в такте чтение протекает адресный полуток и переключается по одному сердечнику на шинах 4 и 5, двух разрядов 6 и 7 накопителя. В такте Запись управление адресно-разрядным полутоком осуществляется блоком 10 (фиг. 1) в зависимости от информации, установленной в разрядах 12 и 13 регистра 11. Если в разрядах 12 и 13 регистра 11 установлены 1, то импульсы Запись с выходов элементов И 65 и 66 (фиг. 4) открывают соответственно ключ 27 (фиг. 2) в дешифраторе 1. На одни из входов ключа 28 и формирователя 46 поступает импульс Запись, а на другие входы - разрешающий низкий уровень напряжения с соответствующих инверсных выходов разрядов 12 и 13 регистра 11 (фиг.1). Цепь полутока Запись в этом случае замыкается через формирователь 46 (фиг. 2), диод 39, ключ 43, диод 35, шину 5 накопителя и соединенную с ней в дешифраторе 8 (фиг. 3) шину 4 , диод 14 (фиг. 2), ключ 27, диод 25 5 и ключ 23. Таким образом, по шинам ,( и протекает полуток записи (в противоположном полутоку чтение направлении) и при соответствующем полутоке записи в адресной шине происходит запись 1 в выбранные сердечники разрядов 6 и 7 накопителя Если в одном разряде 12 (фиг. 1) ре гистра 11 установлена 1, а в другом разряде 13 установлен О, то выход элемента И 66 (фиг. k) закрывает ключи 26 и 27 (фиг. 2). Импульс с выхода элемента И 65 (фиг, ч) открывает ключ 3 (фиг. 2)дешифратора 2, импульс с выхода элемента И 67 (фиг. ) открывает ключ 60 (фиг. 3) в дешифраторе 8. Низкий уровень напряжения на выходе элемента И-НЕбЭ . (фиг. k) открывает ключ 62 (фиг. 5) а высокий уровень с инверсного выхоS разряда 13 (фиг. 1) закрывает ключ 28 (фиг. 2) и цепь полутока записи замыкается от источника .напряжения питания через формирователь , диод 39, ключ ii3, диод 35, шину 5, диод 52, (фиг. 3), ключ 60, диод 57 и ключ б2 на шину нулевого потенциала. Таким образом, в соответствии с содержанием разрядов 12 и 13 регистра 1.1 (фиг. 1) в шийе 5 разряда 7 накопителя протекает полуток записи, а в шине разряда 6 накопителя полуток записи отсутствует . . Если же в одном разряде 12 регист ра 11 установлен О, а в другом раз ряде 13 установлена 1, то в такте Запись элементы И б5 и 67 и элемент И-НЕ б9 (фиг. ) закрывают ключи 43, , 5 (фиг. 2) дешифратора 2 и ключи 60 и 62 (фиг. 3) дешифратора 8. Импульсом, с выхода элемента И 66 (фиг. А) открывается ключ 27 (фиг. 2) дешифратора 1, а выход элемента И 68 открывает ключ б1 (фиг.З) .дешифратора 8. Высокий уровень напряжения с инверсного выхода разряда 12 (фиг. 1)закрывает формирователь k (фиг. 2) дешифратора 2 и через элемент Н-НЕ 70 (фиг. 4) открывает формирователь 63 .(фиг. 3) дешифратора 8 Цепь полутока записи замыкается через формирователь 63, диод 58, ключ 61, диод 8, шину 4j| , диод (фиг. 2), ключ 27, диод 25 и ключ 28 В этом случае в соответствии с содержимым разрядов 12 и 13 (фиг. 1) регистра 11 в шине разряда 7 ад-, 056 ресно-разрядный полуток отсутствует, а в шине разряда 6 протекает адресно-разрядный полуток записи. И, наконец, если в обоих разрядах , 12 и 13 регистра 11 установлен О, то в блоке 10 закрываются элементы И 65-68 и элементы И-НЕ б9 и 70 (фиг. t), закрывая тем самым, ключи 26, 2, 28, , kk и kS формирователь 46 в дешифраторах 1 и 2(фиг.2), формирователь 63 (фиг. 3) и ключи 60, 61 и 62 в дешифраторе 8 и, следовательно, полутоки записи в шинах Н. и 5-1 разрядов 6 и 7 накопителя не протекают. Таким образом, благодаря объединению адресно-разрядных шин накопителя в дополнительных дешифраторах, при записи в несколько, например в два выбранных разряда, работает только один формирователь тока, за счет чего улучшается температурный режим запоминающего устройства и, следовательно, повышается его надежность. Технико-экономическое преимущество предлагаемого устройства заключат ется в более высокой, fio сравнению с известным устройством надежности. Формула изобретения 1. Запоминающее устройство типа 2,5 Д, содержащее магнитный накопитель, адресно-разрядные входы которого соединены с выходами основных дешифраторов, входы которых подключены к выходам регистра адреса, и информационный регистр, отличающееся тем, что,с целью повышения надежности устройства, в него введены дополнительные дешифраторы, сумматорыпо модулю два и блок местного управления, причем выходы каждого дополнительного дешифратора соединены с адресно-разряд- ными вь1ходами магнитного накопителя, выходы,каждого сумматора ho модулю два подключены к входам соответствующего дополнительного дешифратора, а входы - к соответствующим выходам регистра адреса, одни из выходов блока местного управления соединены с управляющими входами дополнительных дешифраторов, а другие выходы - с управлякнцими входами основных дешифраторов, информационные входы блока местного управления подключены к прямым и инверсным выходам информационного регистра, а вход запуска являет ся входом записи устройства. 2. Устройство по п. 1, о т л и чающееся тем, что блок местного управления содержит элементы И и элементы И-НЕ, причем выходы первого и второго элементов И подключены к первым входам третьего и четвертого элементов И, вторые входы которых соединены соответственно с первыми входами первого и второго элементов И-НЕ, вторые входы которых подключены соответственно к первым входам первого и второго элементов И вторые входы которых объединены и являются входом запуска блока, первые входы элементов И-НЕ и первые входы первого и второго элементов И являются информационными входами блока, выходами которого являются выходы элементов И и элементов И-НЕ. Источники информации, принятые во внимание при экспертизе 1.Шигин А.Г., Дерюгин Л.А. Цифровые вычислительные машины. М., Энергия, 1975, с. 153-158. 2.Вопросы радиоэлектроники. Сер. ЭВТ, вып. 5, 197, с. (прототип).

Фиг. г

I

Я

Г

J 53

.З

§

t

«э

«SJ

f

«s

«3-

tea

h

Авторы

Даты

1983-02-23—Публикация

1981-08-28—Подача