(54) ЛОГИЧЕСКОЕ ПРОГРАММНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое программное устройство | 1974 |

|

SU522522A1 |

| Логическое запоминающее устройство | 1976 |

|

SU631989A1 |

| Устройство для ввода информации | 1980 |

|

SU964618A1 |

| Устройство для программного управления | 1985 |

|

SU1267362A2 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Запоминающее устройство | 1978 |

|

SU926712A1 |

| Логическое устройство | 1974 |

|

SU538340A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Многокоординатная система числового программного управления | 1972 |

|

SU448435A1 |

1

Йзоёретение отнрситсй к автоматик и вычислительной технике и может быгь использовано в качестве логического устройства в автоматизированных системах управления.

Известно логическое программное устройство, содержащее усилители-формирователи импульсов тока, матрицу логических базисов, входные и выходные реле, генератор импульсов считывания l .

Однако, известное устройство требует бопыпЕх аппаратурных затрат - для считывания нвформацни с базисов, ойределения фазы сигнала, исключения помех требуете сложная аппаратура. Кроме этогоГ гвфЬрмаононная екосость таких устройств (сумма входных и выходных свгиалое) не превышает 1ОО-150 сигвалов, так как с ув1елш1еннем ивформапионной емкости устройства матрица увеличввается по квадратичной зависвмоств.

Наяболее близким техническим нием к данному изобретению является логическое программное устройство, содержшаее матричный дешифратор, выпол ненный в виде матрицы на двухотверстных трансфлюксорах, большие отверстия которых прошиты горизонтальными и вертикалы{Ь Ми шинами, подключенными к источнику постоянного тока, а малые отверстия прмаиты вертикальными шинами, подключенными к источнику напряжения считывания через rpyimy входных переключательных элементов и через группу выходных переключательных элеме1ггов, и гор{13овтапы1ыми шинами, усилители считывания, диоды 2 .

Однако, на построение этого устрой ства требуются значвгельныа аппаратурные затраты.

ЦещАЭ изобретения является ссжрашевве аппаратурных затрат.

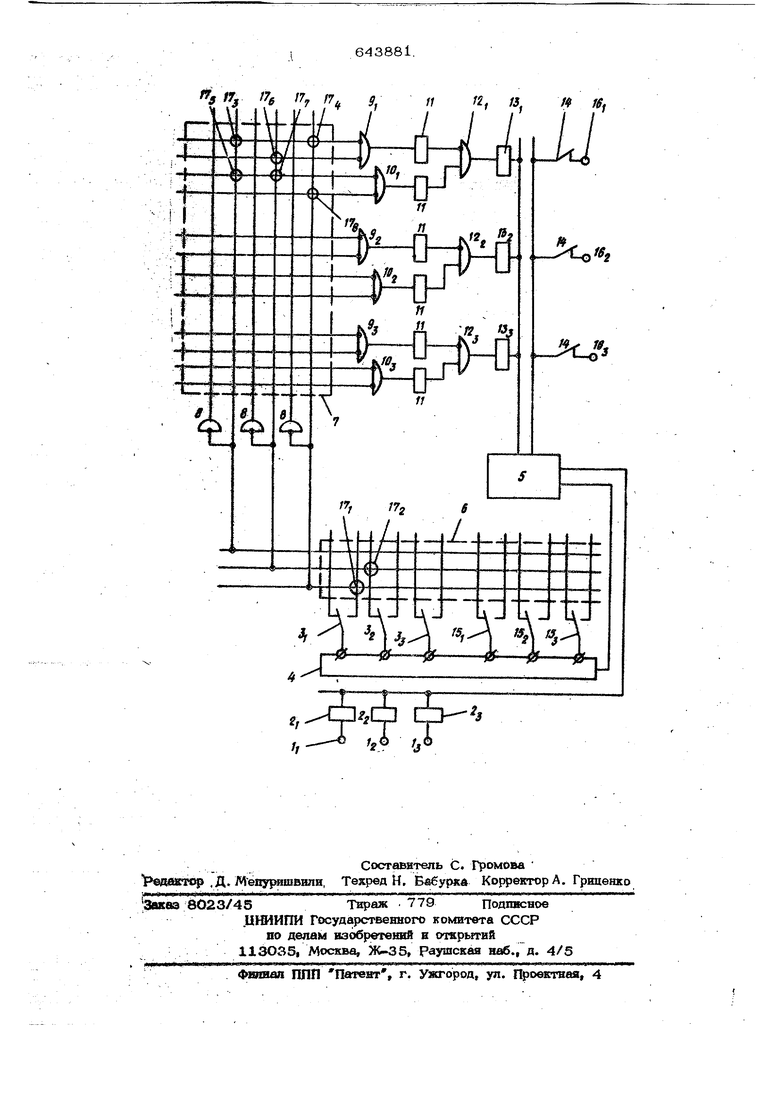

.Эта цель достигается тем, что яред« ложенное программное логическое уст po&cvao содержит матри Еный шифратор. группу элементов НЕ, две группы эле ментов , ЗАПРЕТ, rpyinny элэментов задержки и коммутатор, входы которого соединены с соответствующими выходами групль входньтх переключательных элементов, а выходы с соответствующими входами матричного шифратора, , выходы которого через группу элементов НЕ подключены ко входам матричного дешифратора, выходы которого сое« динены черев первувЗ группу йлёМентсзв ЗАПРЕТ, группу элементов задержки, вт рую группу элементов ЗАПРЕТ- со входами грушш выходных переключательных элементов.. На чертеже приведена структурная блок-схема устройства (длят примера на. три входа и на три выхода). Устройство содержит входные клемм 1„, группу входных переключательных элементов; в которую входят обмотки входных реле 2.- 2j, перекидные контакты входных реле 3j- 3„, коммутатор 4, источник питания 5, матрич1Ш1Й шифратор б, матричный дешифратор 7, группу элементов НЕ 8 две группы эле ментов ЗАПРЕТ Э, lOg, .(введенных дополнительно),группу эле Ментов задержки 11, элементы ЗАПРЁТ 12з, группу выходных переключательных элементов, в которую входят обмотки выходных реле 13.- 13,, , зам каккцие контакты выходных реле 14, перекидные контакты выходных реле , выходные клеммы 1б2,(выходные сигналы х.},, элементы 1 матриц, в которых записано состояние .,., ..,..,: .,..-..-..-;-:: . Вл;однь1е клеммы IjCoenHaSHbt с. обмотками входных реле 2.- 2„1по вторяющими вход11гые переменные а), другой .ВДбОД рбмотьк соединей с кст:ОЧшпсрм питания 5. Подвижзаые контакты .переквдных контактных групп З-и 1 5 входньтх и выходных реле сое динены с контактами коммутатора 4, а неподвижные - ее входйми матричного шифратора 6. Выходы матричного шифра тора 6 соединентл с йрямыми вертикальными шинами матричного дешифратора 7 и со входами элементов НЕ S, выходы которых соединены с инверсными вертикальньши шинами дешифратора. Горизонтальные пины матричного дешифратора соединены со входами элементов ЗАПРЕТ, при этом однь пара шин соединена; с элементами ЗАПРЕТ9 - 9 , а другая - с элементами ЗАПРЕТ .Выходы элементов ЗАПРЕТ соединены через элементы задержки 11 со входами элементов ЗАПРЕТ 12, выходы которых соединены с обмотками выходных реле Замьпсающяе контакты 14 выходных реле соединены с источйиком питания 5 и с выходными клеммами устройства 16.- 16 Устройство функционирует следующим . / В соответствии с заданным алгоритмом функционирования производится запись слов в матричный шифратор 6 и матричный дешифратор 7. Запускается коммутатор 4, Начинается последовательное считьгоание слов, заш«;анных на вертикальных шинах шифратора 6. При этом, если входное (выходное) обесточено, то есть если отсутствует входная переменная а (или выходная переменная х), то считывание производится только с шин, соединенных с нормально-замкнутыми контактами реле, если входное (выходное) реле сработало, то есть если. подаетсй входной а (выходной х), сигнал-то считывание производится только с шин, соединенных с нормально-разомкнутыми контактами реле. Таким обраЙЬм, последовательный набор слов, считываемый с шифратора, является функцией входных (а) и выходных (х) переменных. Слова последовательно засыпаются в матричный дешифратор 7, выходы ;которого построены на двух горизонтальных шинах, элементе ЗАПРЕТ и элементе задержки. При совпадении входного слова с aaimсанным на соответствующем выходе дешифратора образуется сигнал, который удлиняется с помощью элемента аедерж ки 11 на время, большее времени одного цикла работы коммутатора. Если при последуюц1нх циклах данное слово продолжает засылаться в дешифратор, то на выходе последнего будет присутствовать постоянный сигнал. Таким образом достигается программная связь между входами шифратора, представленного входными и выходными переменными и выходами дешифратора, представленного выходными переменными. Н . и. выходе устройства установлень логи ескне элементы, данное устройство реализует булевы функции .в логическом базисе ЗАПРЕТ-ИЛИ-НЕ1. Например, для реализации произвольной функции х а(, 1, а 2 - le) необходимо в элементы 17g . матриц шифратора и дешифратора зайисать . При этом схема работает следующим образом. С помощью эпемента 17 образуется слово ОО1 (l), с по мощью элемента 17,,- слово 010 (2). Первая выходная пара дешифратора 9. настроена на слово ОЮ, вторая 10.на слово 001. При наличии сигналов и и a,gсрабатывают-реле 2, поэтому считывается толыко одно словоОС. Это слово г регистрируется на втором выходе 10:, подакицем сигнал на прямой вход элемента 12 3АПРЕТу срабатывает выходное реле 13, замыасаются ко1ггактЦ Ift выходного реле, выдается сигнал х . Если сигнал а отсутствует, отсутствует и снгнал на прямом входе элемента ЗАПРЕТ; если отсутствует сигнал лрн считываши информации с шифратора в дешифратор засьшается слово OlO, которое СОааает сигнал на запретном входе элемента 1 2л J в обоих случаях сигнал х1 .отсутствует. Остальные булевы функции реализуются аналогичным образом. Обратная связь (выходные сигналы на входе) вве дена в устройство для попучешш функпин ПАМЯТЬ С ЗАПРЕТОМ, применения при ципа суцерпозйции функций и тому по добное. Данное устройство требует матрицу ,размер которой в несколько раз меньше матрицы прототипа, поэтому информационная емкость устройства увеличивает-, ся до неск:ольких сотен сигналов. формула изобретения Логическое программное устройство, содержащее матричный дешифратор, группу входных переключательньпс элементов я группу выходных переключатель ных элементов, о т л я ч а ю щ е е с я тем, что, с целыо сокращения аппаратурных затрат, оно содержит матричный ши(ц рвтор, группу элементов НЕ, две группы элементов ЗАПРЕТ, группу элементов задержки и коммутатор, входы которого соединены с соответствующими выходами группь входнь1х переключательных элементов, а выходы - с соответствукацймй входами матричного шифратора, выходы которого через группу элементов НЕ подключены ко входам матричного дешифратора, выходы которого соединены через первую группу элементов ЗАПРЕТ, группу элементов; - задержки, вторую группу элементов ЗАПРЕТ - со входами группы выходных переключательных эле ментов. Источники информации, принятые во внимание при экспертизе. 1. Авторское свидетельство СССР № 5OS015, кл. О Об F 15/2О, 1974. 2- Авторское свидетельство СССР № 522522, кл. Q 11 С 11/О8, 1974.

17,

/75 J7,

4

-Ш,

й 4H-ftfLJij

f

%

жрни

О

ъ

It

,//,

у

t №,

Авторы

Даты

1979-01-25—Публикация

1976-02-17—Подача