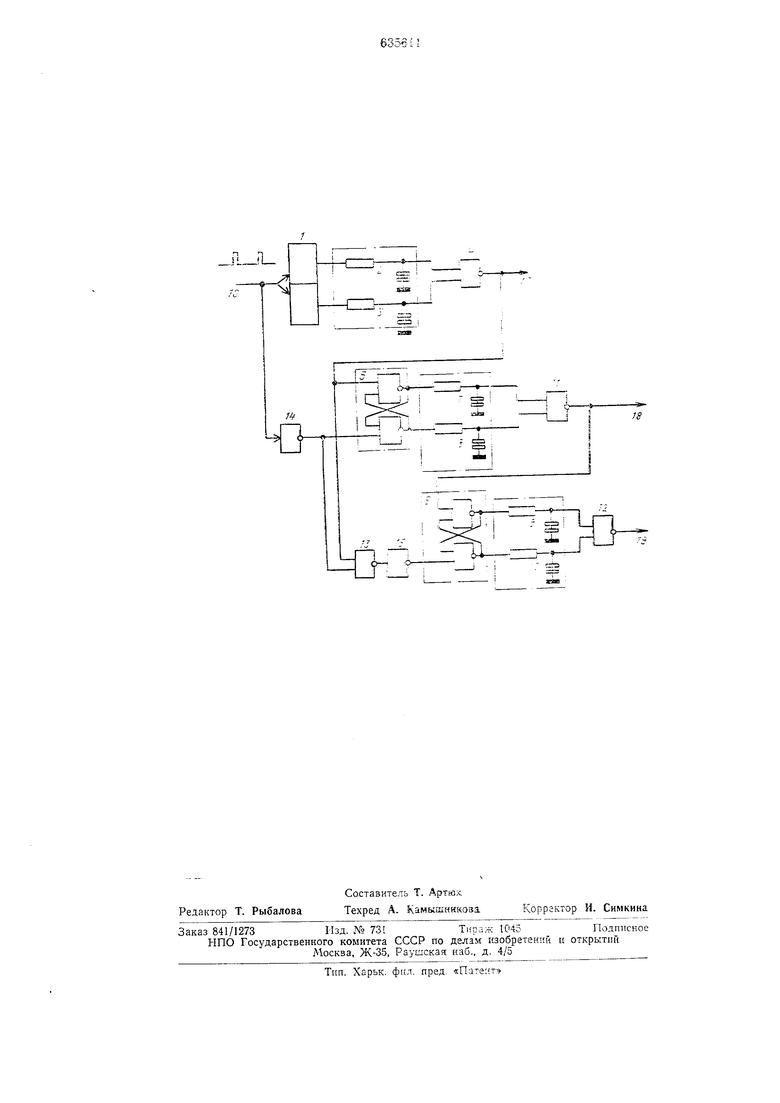

теля также входят логический элемент ИЛИ 13 и инверторы 14, 15.

Входной сигнал подан кз входную 1лину 16. Выходные сигналы сн 1Г 1аются с ВЫХОДОВ 17-19.

Иринцнп работы умножителя заключается в следующем.

Ма выходе триггера / псязля;отс;-; симметричные имнульсы, длителькосгъ кото эых равна периоду следования входных им11 Льсов на входной шине 16. На вь:х:одах интегрирующих / С-эле.ентоЕ 2, 2 появляются экснонеиты заряда - разряда. Ирн равенстве потеииналов экспонент на выходе логического элемента И-НЕ 4 появляются импульсы отрицательной поляриостн. Выравнивание экспонент происхоД1ГГ на их середиие и, таким образом, кмиульс иа выходе элемента И-НЕ 4 появляется на середиие импульса с выхода триггера /.

Импульс с логического элемента И-НЕ 4 взводит триггер 5 в другое состояние, и с этого момента начинают работать интегрир -юн1не С-элементы 7, 8 следующег о каскада. Триггер 5 устанавливается в исходное состояние входным импульсом. На выходе триггера 5 появляются и.мпульсы, длительность которых вдвое меньше длительности импульсов на выходе триггера 1.

Работа следующего каскада умножеиия аналогична работе описанного выше каскада. Таким образом, триггеры 5, с устанавливаются последовательно в единичное состояние импульсом с выходов логических элементов И-НЕ предыдущего

каскада, а сбрасываются триггерь 5, 6 имп льсами с выходов инверторов 14, 15.

Обилий коэффициент умножен;1к частоты равен Л1 2--.

Формула изобретения

Умножитель частоты имиульсов, содержаи1ий тр каскада умножения частоты, каждый из которых состоит из Tpttrrepa, пыходы которого через интегрирующие / С-элементы соединены с входами логического элемента И-НЕ, выход которого в первом каскаде умножения частоты подключен к одному из входов триггера второго каскада умножения частоты, и два инвертора, выходы которых соединены, соответственно с вторыми входами триггеров второго и третьего каскадов умножения частоты, о т л и ч а ю HI, и и с я тег что, с целью иовыщення надежности работы, в liero введен логический элемент ПЛИ. зходы которого соединены с входами Tpiirreра второго, а выход - с входом инвертоjia третьего каскадов умножения частоты, причем вход инвертора второго соединен со счетны.м входом триггера первого каскадов умножения частоты и с входной илтой.

Источники иифор.мации, принятые

во виимаиц. экспертизе:

1.Заявка ФРГ .Y 1948567, кл. И 03 К 35 23/00, 01.02.73.

2.Авторское свидетельство СССР .YO 436445, кл. Н 03 К 23/02, 12.07.73.

п n

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1977 |

|

SU738125A1 |

| Устройство для подавления помехпРи цифРОВОй пЕРЕдАчЕ иМпульСНОйпОСлЕдОВАТЕльНОСТи | 1977 |

|

SU840745A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1102036A2 |

| Формирователь импульсов | 1977 |

|

SU764108A1 |

| Одновибратор | 1978 |

|

SU703896A1 |

| Селектор импульсов по длительности | 1980 |

|

SU902240A1 |

| Устройство для генерации одиночных импульсов | 1977 |

|

SU711670A1 |

| Формирователь импульсов | 1979 |

|

SU839029A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1991 |

|

RU2036550C1 |

| Ждущий генератор импульсов | 1980 |

|

SU894832A1 |

Авторы

Даты

1978-11-30—Публикация

1977-07-26—Подача