счетчик, выходы разрядо-в которого подключены :ко входам дополнительного триггера, дополнительный триггер, шины данных управления коэффициентом иересчета, -в каждый разряд синхронного двоичного счетчика введен элемент И-ИЛИ с тремя структурами И, прямой гвыход три1ггера р азряда еоедИНен с .первыми входамл первой и второй структуры И, инверсный выход триггера -разр.яда саедиг еи с первым входом третьей структуры И, соответствующая шипа данных унравления коэффициентом пересчета соединена со вторым входом второй структуры И, соответствующая шина инверсных даииых - со вторым входом третьей структуры И, прямой выход дополнительного триггера соединен со вторыми входами первых структур И всех разрядов, а инверсный выход дополнительного триггера - с третьими входами третьих структур И всех разрядов.

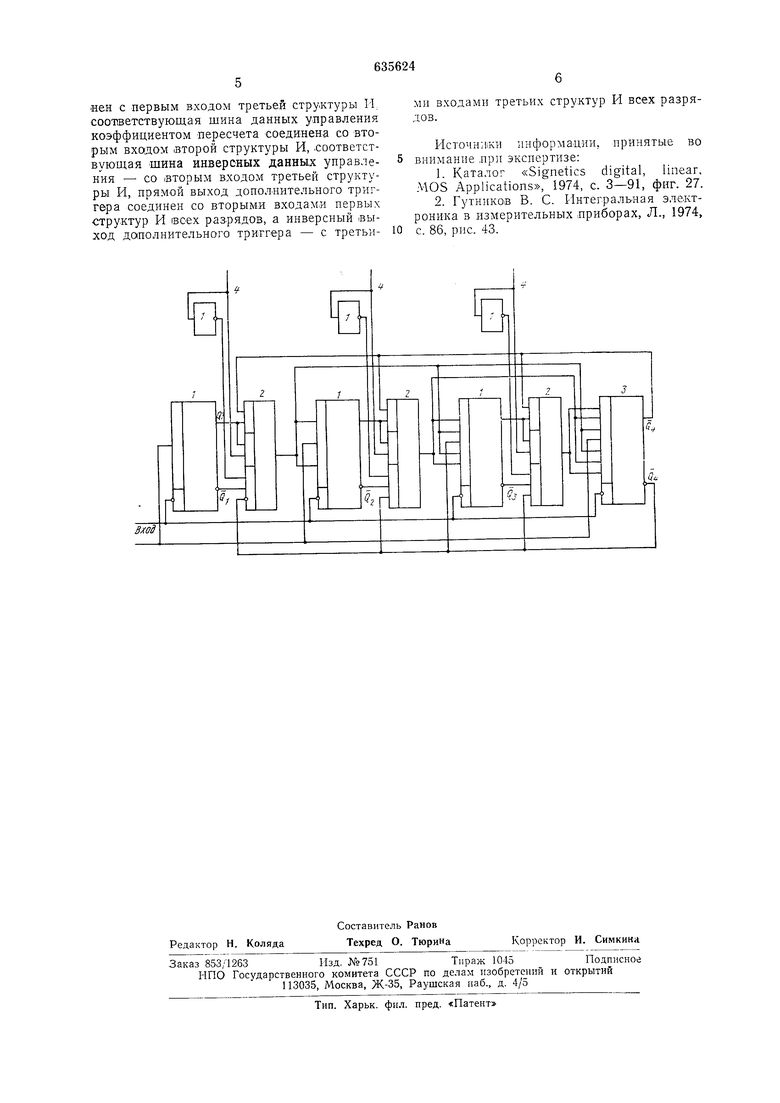

На чертеже (ириведсна схема -предлагаемого счетчика.

Счетчи к с регулируемым коэффициентом .пересчета состоит из синхронного двоичного счетчика, каждый разряд которого содержит //(-триггер / и элемент И-ИЛИ 2 с тремя структурными И, из доиолнительного //(-триггера 3 и шин управления коэффициентом пересчета 4.

Выходы элементов И-ИЛИ 2, являющиеся выходами разрядов синхронного счетчика, соединены €0 .входами дополнительного триггера 3. В каждом разряде .прямой ВЫХОД //(-триггера / еоединен с первыми входами первой и второй структуры И элемента И-ИЛИ 2, инверсный выход //(-триггера / соединен с первым входом третьей структуры И. Соответствующая данному разряду шина унравления коэффициентом пересчета 4 соединеиа со вторым входом второй структуры И, а ее инверсия - со BTOipbiM входом третьей структуры И, прямой выход дополнительного триггера 3 соединен со вторыми входами первых структур И элементов И-ИЛИ .всех разрядов, а инверсный выход дополн.ительиого триггера 3 соединен е третьим входом третьих етруктур И элементов И-Р1ЛИ всех разрядов.

Устройство работает следующим образом.

В исходном состоянии на прял-гых выходах триггеров / и 3: Qb Q2/ Qz, Qi - находятся «нуль, а коэффициент пересчета 2(/(+1) вводится путем установки двоичного .кода числа К н-а в.ходах шин управления коэффищиеито.м пересчета 4.

.При этом .потенциалы на прямом п инверсном выходах Q4 и Q4 дополнительного тригге|ра 3 и шинах уиравления коэффициеитом пересчета 4 «разрешают прямой выход триггера / и «запрещают инверсный выход или «разрешают инверсный -выход

ФПИГГРПЯ / И «ЧЯППРГИЯТПТ ППЯМОЙ BIilXOI.

Элементы И-ИЛИ 2 коммутируют триггеры / 1ИО «разрешенным выходам .по схеме сиихроппого двоичного счетчика. На выходах счетчика с регул.ируемым коэффициентом пересчета, т. е. на выходах элементов .И 2 находится число 7 - К в двоичном коде - .начальное состояние (для случая трех триггеров /). Иосле прихода /(-го счетного импульса на «разрешенных выходах триггеров / и па выходах элементов И-ИЛИ 2 находятся «единицы. После прихода /(j-i счетного импульса переключаются -все триггеры У и 3 и триггер 3 своим «едииичным потенциалом на иря.мом выходе 4 «разрешает пря.мые выходы Qi-Q3 триггеров / и «запрещает инверсные QI-Qs- В это время па прямых .выходах триггеров / QI-Qa находится число 7-/(в двоичном коде. Элементы И-ИЛИ 2 коммутируют триггеры / ио прямым выходам QI-Qs но схеме сиихронного двоичного счетчика .и иа вы.ходах элементов И-ИЛИ 2 находится число 7-К в двоичном коде- иачальное состояние. После ирихода 2К+И

го счетного им.пульса иа лрямых выходах триг.геров } Е 3 и иа выходах .комм-утирующих схем находятся «единицы. После .прихода 2/(+2 счетного имнульса триггеры / и 3 переключаются в состояние «нуль -

исходное состояние. При это.м по выходу Qi ведется пересчет на 2, а по выхода.м элементов ИЛИ 2 и триггера 3 Q-i ведется лересчет па 2(/(+1).

Предельная частота иоступлепия счетных импульсов на вход быстродействующего счетчика

.1

1

где /1-предельная частота синхронного двоичного счетчика на //(-триггер.ах; 1 - задерж.ка сигнала на элементе И-ИЛИ.

Исцользоваиие предлагаемого счетчика в схемах цифровых устройст(в позволит повысить быстродействие этих устройств.

Формула изобретения

Счетчик iC регулируе.мым коэффициенто.м .пересчета, содержащий синхронный двоичный счетчи.к, доиолнительный триггер,

шины данных управления коэффициентом пересчета, выходы разрядов синхронного двоичного счетчика .подключены IKO входам дополнительного триггера, отличающийся те.м, что, с целью повышения быстродействия, в каждый разряд синхронного двоичного счетчика введен элемент с тремя структурами И, пря-мой выход триггера р1азряда соединен с пер.выми входами пер.вой и второй структуры И,

инвепспый выхоп тпиггепа пазояда соеди«ен с первым входом третьей структуры И, сооттветствующая шина данных управления коэффициентом пересчета соединена со вторым входом второй структуры И, .соответствующая шина инверсных данных управления - со вторым входом третьей структуры И, прямой выход допол-нительного триггера соединен со вторыми входами первых структур И всех разрядов, а инверсный выход дополнительного триггера - с третьими входами третьих структур И всех разрядов.

Источни1ки информации, принятые во внимание лри экспертизе:

1.Каталог «Signetics digital, linear, MOS Applications, 1974, с. 3-91, фиг. 27.

2.Гутников В. С. Интегральная электроника в измерительных цриборах. Л., 1974, с. 86, рнс. 43.

| название | год | авторы | номер документа |

|---|---|---|---|

| Недвоичный синхронный счетчик | 1990 |

|

SU1742994A1 |

| Недвоичный синхронный счетчик | 1988 |

|

SU1598168A1 |

| Комбинированный счетчик | 1986 |

|

SU1383490A1 |

| Четырехразрядный двоичный счетчик | 1988 |

|

SU1598171A1 |

| Двоичный реверсивный счетчик | 1990 |

|

SU1758873A1 |

| Недвоичный синхронный счетчик | 1989 |

|

SU1714807A1 |

| Кольцевой счетчик | 1988 |

|

SU1531213A1 |

| СПОСОБ И УСТРОЙСТВО СЧЕТА ИМПУЛЬСОВ | 2015 |

|

RU2604334C2 |

| Управляемый делитель частоты с дробным коэффициентом деления | 1989 |

|

SU1677870A1 |

| Синхронный десятичный счетчик | 1989 |

|

SU1661994A1 |

J

G,

Авторы

Даты

1978-11-30—Публикация

1976-07-21—Подача