Изобретение относится к цифровой технике и может найти применение в устройствах автоматики и вычислительной техники для обработки дискретной информации в условиях помех.

Цель изобретения - упрощение счетчика при расширенных функциональных возможностях и высокой помехоустойчивости.

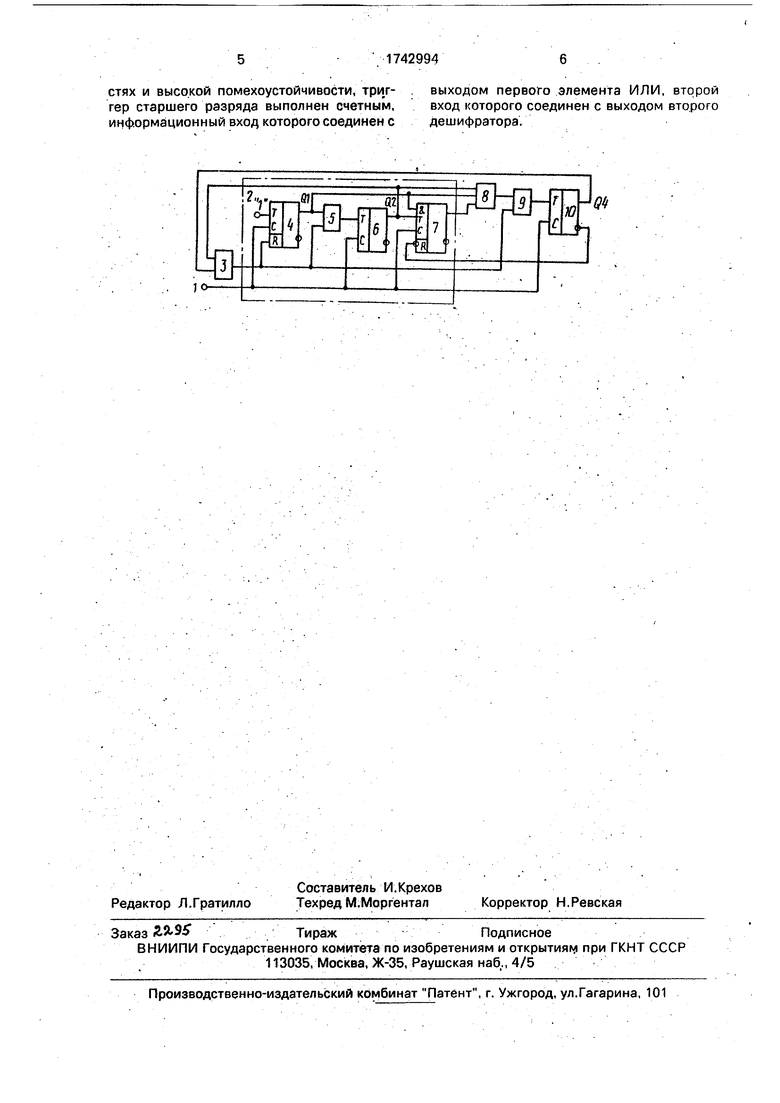

На чертеже приведен недвоичный четырехразрядный синхронный счетчик с модулем счета равным одиннадцати.

Счетчик имеет входную шину 1, двоичный синхронный счетчик 2, элемент И 3, первый-третий. разряды 4, 6, 7, элемент ИЛ И 5, элемент И 8, элемент ИЛИ 9, счетный триггер 10. Элемент И 8 является первым

дешифратором, а элемент И 3 - вторым дешифратором. Входная шина 1 подключена к тактовым входам триггеров двоичного синхронного счетчика 2 и триггера 10, прямой выход которого соединен только с входом элемента И 3, другой вход которого подключен к выходу триггера 6, а выход элемента И 3 соединен с входом установки в О триггера 4, входом элемента ИЛИ 5 и входом элемента ИЛИ 9. Входы элемента И 8 подключены к соответствующим выводам триггеров 4, 6 и 7 двоичного синхронного счетчика 2, а выход элемента И 8 соединен с вторым входом элемента ИЛИ 9, выход которого соединен с входом счетного триггера 10, инверсный выход которого подклюVI

Јь Ю Ю ЧЭ 4

чен к входу установки в О триггера 7 двоичного синхронного счетчика 2. Выход триггера 4 через второй вход и выход элемента ИЛИ 5 соединен с входом триггера 6, выход которого соединен с первым входом триггера 7, второй вход которого соединен с выходом триггера 4 для образования двоичного синхронного счетчика 2. Вход триггера 4 подключен к шине потенциала логической единицы для обеспечения работы двоичного синхронного счетчика 2. Триггеры разрядов счетчика выполнены на основе счетных триггеров.

Счетчик работает следующим образом. В исходном состоянии, поскольку цепи установки не показаны, счетчик может находиться в любом из возможных одиннадцати состояний. Пусть счетчик находится в состоянии, когда на прямых выходах Qi, Cte. Оз, Q4 соответственно разрядов 4,6,7,10 образован код 0000. В этом случае на выходах элементов И 3 и И 8, а также элементов ИЛИ 5 и ИЛИ 9 будет О. С подачей тактовых импульсов по шине 1 работает, двоичный счетчик 2 до тех пор, пока на его выходах не образуется код 111, т.е. единицы на прямых выходах разрядов 4, б, 7, а на выходе триггера 10 будет О, так что образован код 1110. Следовательно на выходе элемента И 8 к этому моменту образован потенциал единицы, который передается на выход элемента ИЛИ 9 и разрешающий вход триггера 10. С подачей восьмого входного импульса двоичный счетчик 2 обнуляется, а триггер 10 переходит в единичное состояние и образуется код 0001. При этом на инверсном выходе триггера 10 образован потенциал нуля, который блокирует в нулевом состоянии разряд 7 двоичного счетчика 2, а на выходе элемента ИЛИ 9 вновь образуется О, так как на выходах элементов И 3 и И 8 будет О. С подачей девятого входного импульса по шине 1 первый разряд 4 двоичного счетчика 2 вновь переходит в единичное состояние, так что образуется код 1001, поэтому на выходе элемента ИЛИ 5 будет образован единичный потенциал, который подготавливает разряд 6 к срабатыванию. С подачей десятого входного импульса по шине 1 первый разряд 4 двоичного счетчика 2 переходит в 0м, а из-за наличия в предыдущем такте 1 на выходе элемента ИЛ И 5 триггер 6 занимает единичное состояние, так что образуется код 0101. Следовательно, на выходе элемента И 3 образуется 1, которая через элемент ИЛИ 9 подготавливает к срабатыванию триггер 10, при этом по входу установки блокируется с выхода элемента И 3 триггер 4 в нулевом состоянии, а через элемент ИЛИ 5 готовится к срабатыванию

триггер 6. С подачей одиннадцатого входного импульса по шине 1 счетчик возвращается в начальное состояние, т.е. образуется код 0000. Таким образом счетчик считает по

одиннадцати в равномерном двоичном коде, а все избыточные состояния счетчика исключены. В общем случае может быть,по- строен счетчик с коэффициентом пересчета 2т + 2П - 1, где т - разрядность двоичного

счетчика, an- разрядность неблокированных разрядов двоичного счетчика, причем элемент И 3 является вторым дешифратором, на первый вход которого подают сигнал с прямого выхода триггера 10, а на

второй его вход - сигнал, соответствующий наличию хотя бы одной единицы от неблокированных разрядов двоичного счетчика. Блокированными являются все младшие разряды двоичного счетчика с выхода дешифратора 3 и все старшие разряды двоичного счетчика 2 с инверсного выхода разряда 10. Наличие хотя бы одной единицы .от неблокированных разрядов двоичного счетчика 2 можно, например, получить с выхода элемента ИЛИ. входы которого соединены с выходами этих неблокированных разрядов.

30

Формула изобретения

Недвоичный синхронный счетчик, содержащий входную шину, т-разрядный двоичный счетчик, триггер старшего разряда, два элемента ИЛИ, два дешифратора,

входы первого из которых подключены к выходам триггеров разрядов двоичного синхронного счетчика, тактовые входы которого, соединены с тактовым входом триггера старшего разряда и входной шиной, первый

вход первого элемента ИЛИ соединен с выходом первого дешифратора, прямой выход триггера старшего разряда соединен с соответствующим входом второго дешифратора, остальные входы которого соединены с выходами триггеров неблокированных разрядов двоичного синхронного счетчика, вход триггера младшего из неблокированных разрядов подключен к выходу второго элемента ИЛИ, первый вход которого соединен

с выходом второго дешифратора и входами установки в ноль триггеров младших разрядов двоичного синхронного счетчика, старший из младших разрядов которого соединен с вторым входом второго элемента ИЛИ, инверсный выход триггера старшего разряда подключен к входу установки в ноль m-n (где m n 1) старших разрядов двоичного синхронного счетчика, отличающийся тем, что, с целью упрощения при

расширенных функциональных возможностях и высокой помехоустойчивости, триггер старшего разряда выполнен счетным, информационный вход которого соединен с

выходом первого элемента ИЛИ, второй вход которого соединен с выходом второго дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Недвоичный синхронный счетчик | 1989 |

|

SU1714807A1 |

| Недвоичный синхронный счетчик | 1988 |

|

SU1598168A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| Преобразователь кода во временной интервал | 1988 |

|

SU1672567A1 |

| Пересчетное устройство | 1980 |

|

SU921093A1 |

| Недвоичный синхронный счетчик | 1981 |

|

SU961151A1 |

Изобретение может быть использовано в радиоэлектронных устройствах цифровой техники для обработки дискретной информации в условиях помех. Цель изобретения - упрощение при расширенных функциональных возможностях и высокой помехоустойчивости. Счетчик содержит входную шину 1 двоичный синхронный счетчик 2, два дешифратора 8 и 3, два элемента ИЛИ 5 и 9 и старший разряд 10, вход которого через первый элемент ИЛИ 9 соединен с выходом первого дешифратора 8 всех единиц двоичного счетчика, выход второго дешифратора 3 блокирует младшие разряды и через второй элемент ИЛИ 5 соединен с триггером неблокированныхразрядов, старшие разряды двоичного счетчика 2 блокированы с инверсного выхода триггера старшего разряда 10. Счетчик может иметь коэффициент пересчета не только 11, но и 2т + 2 - 1, где т- разрядность двоичного счетчика; п - разрядность его неблокированных с выхода разряда счета разрядов. 1 ил. сл

| Справочник по интегральным микросхемам, под ред | |||

| Тарабрина Б.В | |||

| М.: Энергия, 1980 | |||

| Недвоичный синхронный счетчик | 1988 |

|

SU1598168A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-06-23—Публикация

1990-01-25—Подача