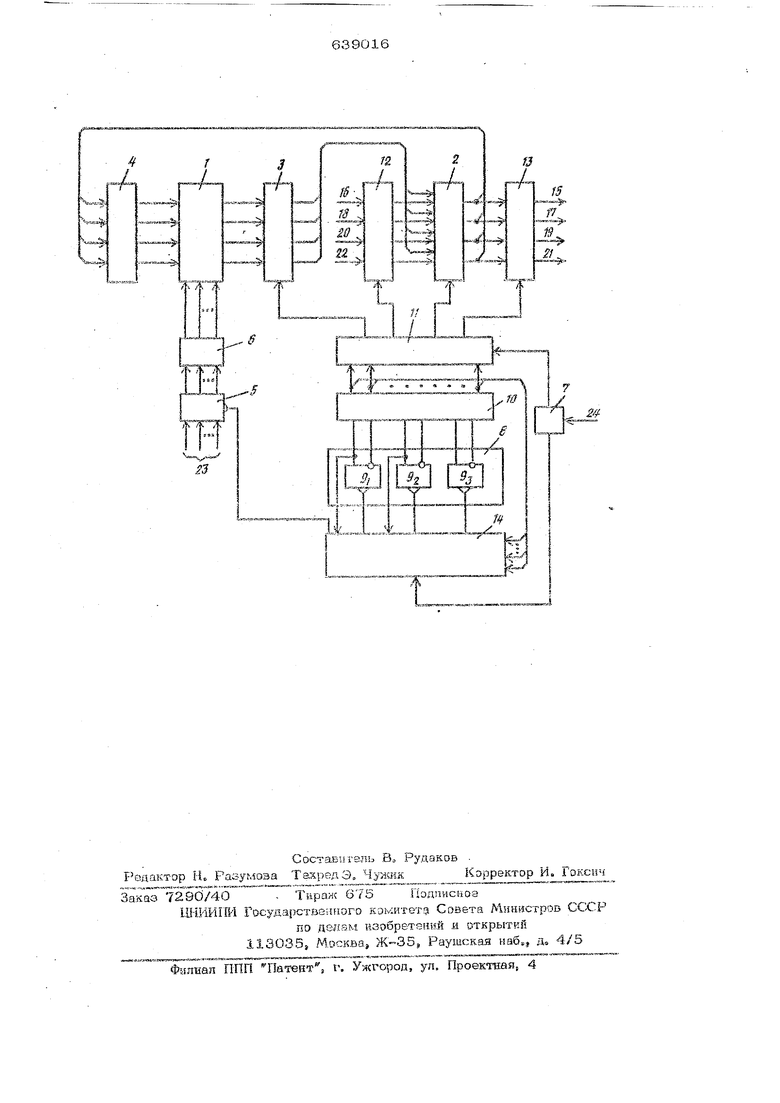

Изобретение относится к запоминающим услройствам. Известно устройство, содержащее регистр к дешифратор адреса, подключенные к накопителю, синхронизатор, регистр числа, соединенный с выходным коммутатором -1едостатком устройства является низкая ффектквность его использования при работе с устройствами - потребителями, ииформбщионная разрядность которых меньше разрядности запоминающего устройства Изосновногоавт.св.№526019 извест- но запоминаюшее устройство, содержашее регистр адреса, выходы которого через де шифратор адреса подключены к адресным шинам накопителя, а его выходные шины через усилители воспроизведения подсоеди нены к одним из входов регистра числа. При этом выходы регистра числа соединены с одними из входов выходного комму татора и через разрядные формирователи с разрядными шинами накопителя, адресные шнны - со входами регистра адреса, вькодные шины устройства - с выходами выходного KDMNtyTSTOpa, а входные шины устройства -с первыми входами аходного к.ом {утатора, выходы которого подключены ко Бторык входам peniCTpa числа. Устройст во .е содержит блок управления, пер Bbot LiXDA которого соедшгзн с первым вь ходом сикхрокйзатора, ьторыэ входы с выходами дешифратора вь;бйра операции обмен., ., K:-ro|.t:iro пойгсдючоиь к выходам регистра Еыб:.}ра операции o6N.sua, первые вьк.йды блока управления соединены с другими аходам.и выходного коммутатора, вторые выходы - с третьими входами регистра числа, третьи выходы - со вторыми вкодакш входного коммутатора U четвертые выходы - со вторыми входами усилителей воспроизведения. При монопольном обращении к последовательно расположенным ячейкам памяти этого запоминающего устройства необходимо при калсдом обращении фор Шровать следующий код адреса и код выбора оп&рации обмена, передача которых снижает надежность системы в целом. Поэтому для организации монопольного режима используется счетный регистр адреса, в который заносится начальный код адреса и при каждом последующем обращении синхронизатор вырабатывает импульс, поступа ющий на счетный вход регистра адреса дл выполнения команды по следующему адресу запоминающего устройства без паредбнчи кода адреса по адресным шинам. Недостатком известного устройства яв ляется то, что монопольный режим возможен лишь при обмене с потребителем, дан ным с максимальной разрядностью (например, только словами) запоминающего устройства. Это снижает надежность устройства, так как при обмене данными укороченным форматом (например, при обмене полусловами и четвертьсловами байтами), когда в зависимости от операции обмена нужно записывать в одну ячей ку запоминающего устройства, например полуслова или байты, такой режим невозможен. Цель изобретения -повышение надежности устройства Это достигается тем, что устройство содержит дополнительный коммутатор, вхо ды которого подключены соответственно к дополнительному выходу сиахроиизатора и выходам дешифратора выбора операции обмена и регистра выбора операции обменаэ а выходы дополнителшного коммутатора соединены соответственно со входами регистра выбора операдин обмена и со счетным входом регистра адреса. На чертеже дана структурная схема устройства, информадионная разрядность которого составляет, например четыре байта. Запоминающее устройство содержит накопитель 1, регистр 2 числа, усилители 3 воспроизведения, разрядные формирователи 4, регистр 5 адреса, дешифратор 6 адреса, синхронизатор 7, регистр 8 выбора операций обмена, состоящий, например из триггеров 9, дешифратор Ю выбора операдии обмена, блок 11 управления, входной коммутатор 12, вьгходной коммутатор 13, дополнительный коммутатор 14, шины 15-24, причем 15, 17, 19 и 21 - выходные шины, 16, 18, 20 и 22 в.ходн1 е шины, 23 - адресные шины, 24 - шина признак монопольного режима. Выходы регистра 5 адреса через дешифратор 6 подсоединены к адресным шинам накопителя 1. Выходы накопителя 1 через усилители воспроизведения 3 подключены к первым входам регистра 2, Выходы регистра числа 2 соединены с одними из входов выходного коммутатора 13 и через разрядные формирователи 4 соединены с разрядными шинами накопителя 1, Выходы входного коммутатора 12 подключены ко вторым входам регистра числа 2. Первый акод блока 11 управления соединен с первым выходом сиахронизатора 7, вторые входы блока 11 с выходами дешифратора 10 выбора операции обмена, входы которого подключены к выходам регистра 8 выбора операции обмена. Первые выходы блока 11 управления соединены с другими аходами выходного коммутатора 13, вторые выходы с третьими аходами регистра числа 2, третьи выходы - со вторыми входами входного коммутатора 12 и четвертые выходы блока 11 - со вторыми входами усилителей 3 воспроизведения, К первому входу коммутатора 14 подключен дополнительный выход синхронизатора 7, Ко вторым входам коммутатора 14 подключены вьрсоды дешифратора 10 выбора операдии обмена, к третьим входам - выходы регистра 8. Вьсходы коммутатора 14 подключены к аходам регистра 8 и счетному входу регистра адреса 5, Устройство работает следующим образом, Содержимое регистра 8 выбора операции обмена несет информацию о номерах шин, по которым ведется обмен словами с потребителем; при обмене по одному байту - по шинам 15, 16, при обмене по полуслову - по шинам 15-18, при обмене по слову - по шинам 15-22, Перед записью данных производится стирание следующим образом: во время операдии стирания синхронизатор 7 выдает сигнал стробирования в блок 11 управ-ления, который, анализируя результаты,, вьщанкые дешифратором 1О выбора операции обмена, производит стробирование топьiio тах байтов данных, которые необходимо сохранять, а остальные байты в регистр числа Я не заносятся. При обмене данкьгми с максимальным количеством бай тов производится стирание во всех байтах данных. Во время записи информадия о данных, подаваемая по шинам 16 18 или 16, 18,2О и 22 поступает на входной коммутатор 12, Синхронизатор 7 выдает сигнал приема данных в блок 11 ynpaa ieния, который анализирует состояние выхо-« дов дешифратора 1О выбора операдии обмена и с помощью входного коммутатора 12 производит перевод байтов с шик, на

которые они поступают (16 или 16 н 18), в Т9 байты рагистра 2, где информация должна быть записана и заранав произведено стирание прежней информадии. Затем обиовленное содержимое всего ре- s гистра 2 числа через разрядные формироватани 4 записывается в накопитель 1. При обмене данными с максимальным количеством байтов производится прием всех байтов данных по шинам 16,18, 20 и 22. ю

В случае необходимости записи данных в последовательные ячейки накопителя 1 имеете с начальным кодом адреса, с которого нужно проводить запись к который 15 подается на адресные шины 23, на синхронизатор 7 подается признак монопольного режима по шине 24 и поддерживается до тех пор, пока осуществляется последовательная запись. Поэтому, при наличии 20 признака монопольного режима, по второму обращению к запоминающему устройству на запись код адреса на адресные шины 23 не поступает, а импульс единичного приращения с синхронизатора 7 через 25 коммутатор 14 поступает на счетный вход рагистра адреса 5 и, тем самым подготавливает следующую ячейку накопителя 1 для залйси следующих данньии Такое взаимодействие блоков запоминшошего 33 устройства справедливо при записи данных с максима/шным количеством байтов (в нашем примере - яо слову). При обмене по полуслову с признаком монопольного режима сигналы с выходов дешифратора 35 10 выбора операции обмена осугаествлиот коммутааию кмдульса единичного приращеаия, поступающего с синхронизатора 7 а коммутатор 14, на счетный нход триггера 8 старшего разряда (левый на чергейса) 0 регистра 8 выбора операции обмана, Flpsjмой выход этого триггера 9 через коь,мутатор 14 соединяется со счетным входам регистра адреса 5. При обмене по одному байту блок 14 адресного управления осуществляет коммутацию импульса единичного приращения на счетный вход триггера 9 предыдущего разряда и коммутацию прямого выхода этого триггера 9 на счетный нход триггера 9 старшего разряда, а прямого выхода последнего - на счетный вход регистра 5 адреса. Благодаря такому подключению коммутатора 14 11режде, чем провзвести запись новой информации в следующую ячейку накопителя 1 (при обмене по полуслову или по одному байту), производится распаковка полуслов (байтов)внутри ячейки, а затем пере« ход к следующей ячейке накопителя 1,

В режимах чтения н чтения с записью новой информации взаимодаВствне всех блоков при обмене информацией по полуслову и байтам остается такнм же, как и в режиме записи с монопольным признаком.

Таким образом, предложенное запоминающее устройство позволяет производить последовательный привм-вщдачу информации с учетом обмена и без пересылки кода адреса в запоминающее устройство от потребители, что повышает надежность и расширяет функциональные воэможностя устройства,

Формула 5 3обретения

Запоминающее устройство по авт.св. № 526О19, отличающееся тем, чтзг с аеяью гаэаышения надежности устройства, оно содержит дополнительный коммутатор, кходы которого подключены соответственно к дополнительному выходу синхронизатора к выходам дешифратора выбора операдни обмена н решстра выбора опарацкн обмена, а выходы дополнительного комк-Еутатора соединены соответственно CD входами регистра выбора операции обмена и со счетным входом регистра адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на газоразрядной индикаторной панели | 1983 |

|

SU1119065A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для управления обменом информацией между ЭВМ и группой периферийных устройств | 1988 |

|

SU1640700A1 |

| Устройство для ввода и вывода динамически изменяющейся информации | 1982 |

|

SU1115043A1 |

| Магнитное оперативное запоминающее устройство | 1976 |

|

SU647742A1 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

Авторы

Даты

1978-12-25—Публикация

1975-12-22—Подача