(Б) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Многотактное микропрограммное устройство управления | 1982 |

|

SU1094033A1 |

| Пикопрограммное устройство управления | 1979 |

|

SU817714A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1179337A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

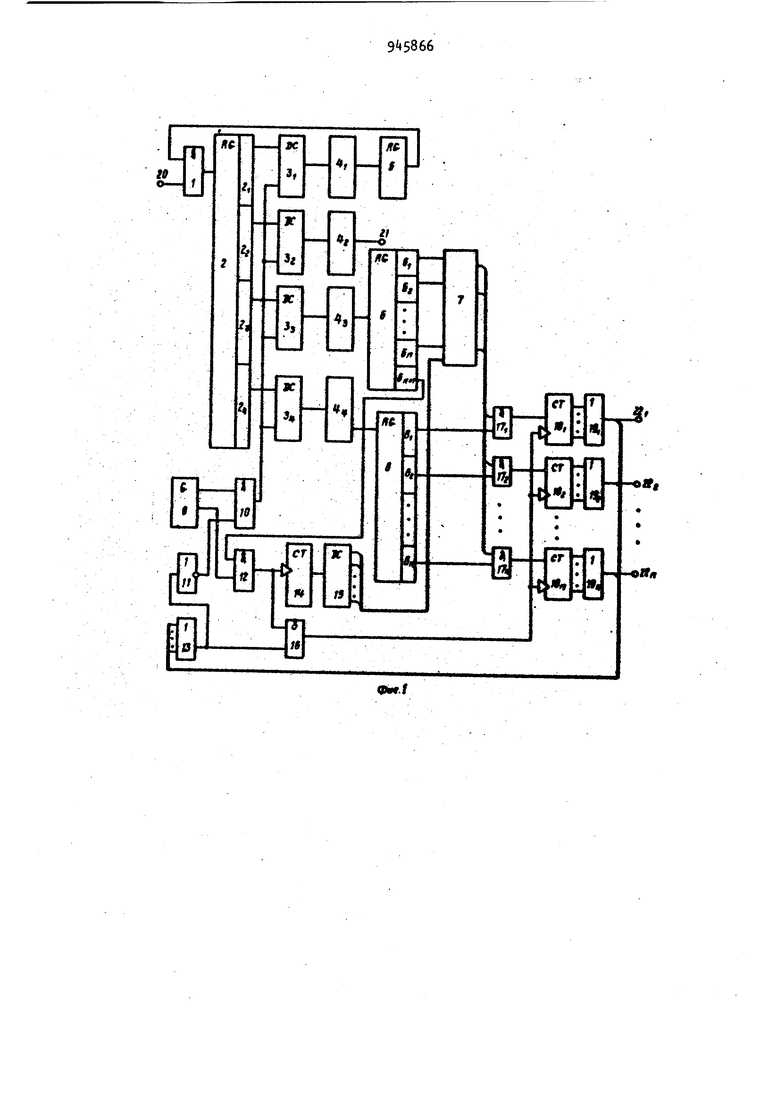

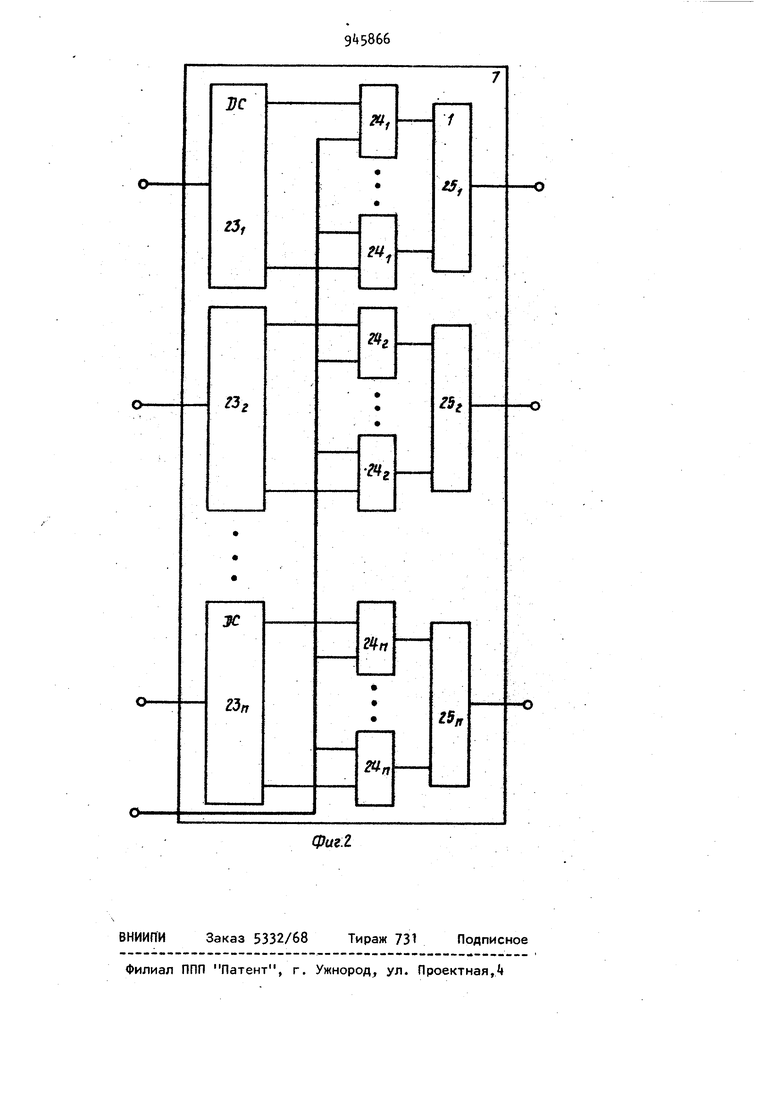

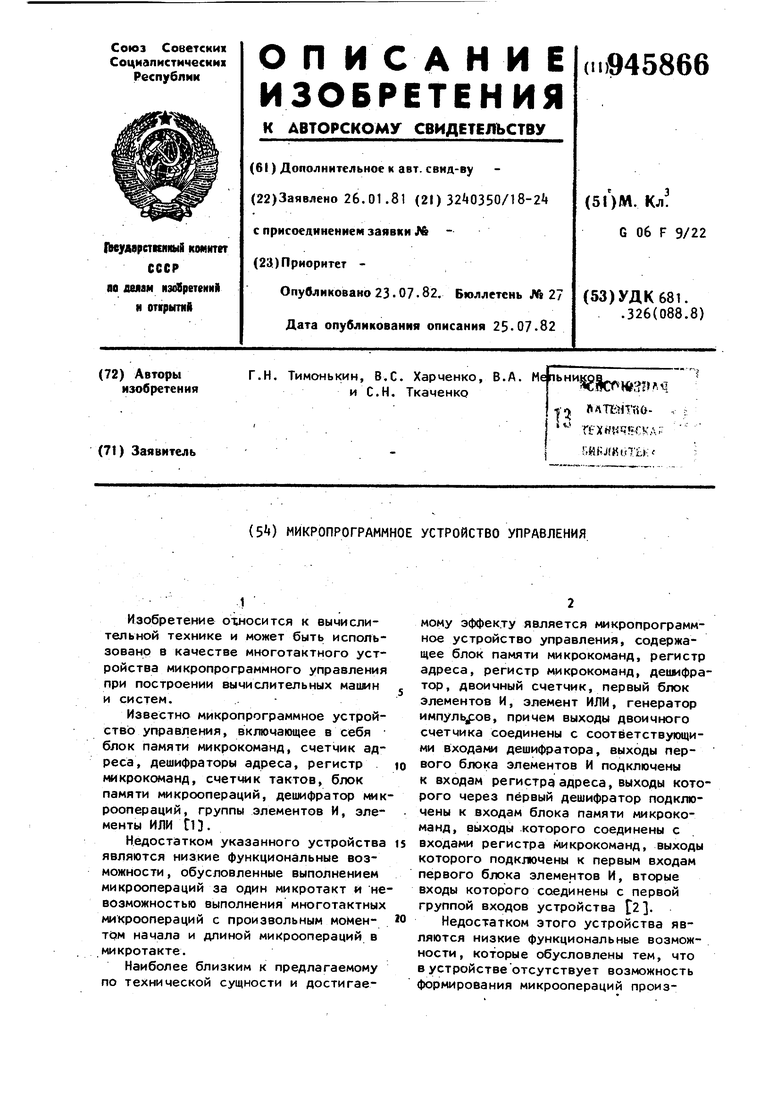

- , ..1 Изобретение оросится к вычислительной технике и может быть использовано в качестве многотактного устройства микропрограммного управления при построении вычислительных маимн и систем.Известно микропрограммное устройство управления, включающее в себя блок памяти микрокоманд, счетчик адреса, дешифраторы адреса, регистр к 1крокоманд, счетчик тактов, блок памяти микроопераций, дешифратор мик роопераций, группы элементов И, элементы ИЛИ ГП. Недостатком указанного устройства являются низкие функциональные возможности, обусловленные выполнением микроопераций за один микротакт и не возможностью выполнения многотактных микроопераций с произвольным моменТ0М начала и длиной микроопераций в микротакте. Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту является микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, дешифратор, двоичный счетчик, первый блок элементов И, элемент ИЛИ, генератор импульсов, причем выходы двоичного счетчика соединены с соответствующими входами дешифратора, выходы первого блока элементов И подключены к входам регистра адреса, выходы которого через первый дешифратор подключены к входам блока памяти микрокоманд, выходы которого соединены с входами регистра микрокоманд, выходы которого подключены к первым входам первого блока элементов И, вторые входы которого соединены с первой группой входов устройства 2. Недостатком этого устройства являются низкие функциональные возможности, которые обусловлены тем, что в устройстве отсутствует возможность формирования микроопераций произвольной длительности в микротакте. В дальнейшем под микрртактом будем п . нимать время, в течение которого выполняется одна микрокоманда. Каждый микротакт разбивается на нанотакты.. Микрокоманда может быть однотактной ил« многотактной. Одйотактная микрокоманда - микрокоманда, микрооперации которой выполняются за один нанотакт. Многотактная микрокоманда микрокоманда, микрооперации которой выполняются за несколько нанотактов в микротакте, при этом начало выполнения микрооперации может быть в любом нанотакте данного микротакта В устройстве отсутствует возможность выдачи в микоотакте микроопераций с перекрытием, имеется большая СЛОЖНОСТЬ в модификации микропрограмм, так как при необходимости изменения либо адресной, либо операционных частей, микропрограмм, либо кодов нанотактов необходимо менять весь блок микропрограммной памяти, кроме того, низкие функциональные возможности устройства обусловлены низким коз1ффициентом информативности блока памяти микрокоманд, что обусло лено наличием повторяющихся операцио ных частей и кодов нанотактов для различных адресов. Целью изобретения является расширение функциональных возможностей ус ройства за счет организации произвол ных процедур нанопрограммирования. Поставленная цель достигается тем что микропрограммное устройство упра ления, содержащее последовательно сое диненные первый регистр адреса, первый- дешифратор, первый блок памяти, второй регистр адреса и первый блок элементов И, другой вход которого является входом логических условий устройства, а выход соединен с входом первого регистра адреса, генератор тактовых импульсов, элемент ИЛИ, счет чик, выход которого соединен с входом дешифратора, дополнительно содержит второй, третий и четвертый блоки памяти, второй, третий и четвертый дешифраторы, третий и четвертый регист ры адреса, группу счетчиков, узел ком мутации моментов начала микроопераций , группу блоков элементов И, первый, второй и третий элементы И, груп пу элементов ИЛИ, элемент НЕ, причем первый выход генератора тактовых импульсов подключен к первому входу пер вого элемента И, второй вход котороЭ64 го подключен через элемент НЕ к выходу элемента ИЛИ и к первому входу второго элемента И, выход первого элемента И соединен с управляющими входами первого, второго, третьего и четвертого дешифраторов, информационные входы второго, третьего и четвертого деимфраторов соединены соответственно с вторым, третьим и четвертым выходами первого регистра адреса, и выходы через второй, третий и четвертый блоки памяти - с первым выходом устройства, входами третьего и четвертого регистров адреса соответственно, выходы разрядов, кроме последнего, третьего регистра адреса соединены с первыми входами узла коммутации моментов начала ь 1кроопераций, вторые входы которого соединены с выходами дешифратора импульсов, а. выходы узла коммутации соединены с первыми входами групп блоков элементов И, вторые входы которых соединены с выходами четвертого регистра адреса, а выходы - с информационными входами групп счетчиков, нулевые выходы которых через группу элементов ИЛИ подключены к второму выходу устройства и к входам элемента ИЛИ, второй выход генератора импульсов соединен с первым входом третьего элемента И, второй вход которого подключен к выходу последнего разряда третьего регистра адреса, а выход - к счетному входу счетчика и к второму входу второго элемента И, выход которого соединен с вычитающими входами группы счетчиков, а также тем, что узел коммутации моментов начала микроопераций содержит группу дешифраторов, группу блоков элементов И, rpynriy элементов ИЛИ, причем входы группы дешифраторов подключены к первым входам узла, а выходы группы дешифраторов соединены с первыми входами группы блоков элементов И, вторые входы которых соединены с вторыми входами узла, а выходы - с входами группы элементов ИЛИ, выходы которых являются выходами узла. На фиг. 1 изображена функциональная схема предлагаемого устройства; на (. 2, - функциональная схема узла коммутации моментов начала микроопераций. Устройство содержит блок 1 элементов И, регистр 2 адреса с выходами , дешифраторы адресов, блоки памяти, регистры 5 и 6 адреса, коммутатор 7, регистр 8 адреса, генератор 9 тактовых импульсов, элемент И 10, элемент НЕ 11, элемент И 12, элемент ИЛИ 13, счетчик Н, дешифратор 15, элемент И 16, группу блоков 17 элементов И, группу 18 счетчиков, группу элементов ИШ , вход 20 устройства, выход 21 устройства, выходы 22 устройства. Узел 7 содержит группу дешифраторов , группу блоков элементов И, группу элементов ИЛИ 25,-25„. Микропрограммные устройства работают следующим образом. Из блоков k и kn памяти считываются адреса и операционные части однотактных микрокоманд. В зависимости от логических условий, поступающих со входа 20 на блок 1 элементов И, происходит модификация адреса и вы.полняется следующая микрокоманда. Если микрокоманда является однотактной, то микрооперации считываются с блока Ц памяти операционных частей на выход 21 устройства. Если считывается адресная микрокоманда, которой соответствует многотактная микрокоманда, то в полях регистра 2 адресов записаны адреса, по которым считывается информация из блоков 3 памяти, в которых хранятся коды начала микроопераций и коды длин микроопераций соответственно. После считывания информация в регистр 6 и регистр 8 по метке в поле являющийся признаком наличия многотактной микрокоманды, открывается элемент И 12, и импульсы с генератора 9 импульсов с частотой, определяемой длительностью нанотакта, начинают запол нять счетчик , который совместно с дешифратором 15 образует распредели тель импульсов. Импульсы с выходов д шифратора 15 определяют последовател ность нанотактов. Последовательность импульсов с дешифратора 15 поступает для.опроса полей регистра 6, в которых хранятся коды начала микроопераций. При совпадении кода нанотакта с выхода дешифратора 15с кодом начала микрооперации, на соответствующем вы ходе группы элементов ИЛИ 25,)25j. уз ла 7 коммутации появляется сигнал начала микрооперации. Сигналы начала микроопераций в определенном нанотак ,те с выхода узла 7 коммутации откры. вают блок 17 элементов И, через кото рые из полей регистра 9 переписываются в двоичные счетчики 18.-18 коды длин микроопераций, начавшихся в данной нанотакте. В результате на соответствующих выходах устройства появляются потенциальные сигналы сигналы микроопераций многотактной микрокоманды. Изменение нулевого состояния определенных счетчиков 18, приводит к появлению сигналов на соответствующих выходах первой группы элементов ИЛИ 19,.-19 г оторые поступают на элемент ИЛИ 13- Сигнал о начале выполнения многотактных микроопераций поступает на элемент И 16 и одновременно запрещает через элемент НЕ формирование очередного микротакта до вьшолнения предыдущей микрокоманды. С началом выполнения многотактной микрокоманды открывается элемент И 16 и на вычитающие входы счетчиков поступают сигналы с генератора 9 импульсов и изменяют состояние кодов соответствующих счетчиков по мере изменения номера нанотакта. Микрооперации на выходах 22-J-22 ц устройства выдаются до обнуления соответствующего счетчика. После обнуления всех счетчиков сигнал на выходе элемента ИЛИ 13 равен нулю, а на выходе элемента НЕ 11 появляется сигнал, который через элемент И 10 разрешает считывание очередной многотактной или однотактной микрокоманды. Возможность формирования в многотактном устройстве микропрограммного управления микроопераций с произвольными моментами начала и длительностью а микротакте, а также увеличение коэффициента информационной гибкости за счет хранения параметров микрокоманд в отдельных блоках памяти позволяет расширить функциональные возможности предлага- емого устройства по сравнению с известным. Формула изобретения 1. Микропрограммное устройство управления, содержащее последовательно соединенные Нервый регистр адреса первый дешифратор, первый блок памяти, второй регистр адреса и первый блок элементов И, другой вход которого является входом логических условий устройства, а выход соединен с входом первого регистра адреса, генератор тактовых импульсов, элемент ИЛИ, счетчик, выход которого соединен с входом дешифратора, о т л и чающееся тем, что, с целью расширения функциональных возможностей за счет организации произвольных процедур нанопрограммирования, допол нительно содержит второй, третий и четвертый блоки памяти, второй, третий и четвертый дешифраторы, третий и четвертый регистры адреса, группу счетчиков, узел коммутации моментов начала микроопераций, группу блоков элементов И, первый второй и третий элементы И, группу элементов ИЛИ, элемент НЕ, причем первый выход генератора тактовых импульсов подключен к первому входу первого элемента И, второй вход (fOTOporo подключен через элемент НЕ к выходу элемента ИЛИ и к первому входу второго элемента И, выход первого элемента И соединен с управляющими входами первого, второго, третьего, четвертого дешифраторов, информационные входы второго, третьего, четвертого дешифраторов соединены соответственно с вторым, третьим, четвертым выходами первого регистра адреса, а выходы через второй, третий, четвертый блоки памяти - с первым выходом устройства, входами третьего и четвертого регистров адреса соответственно, выходы разрядов, кроме последнего третьего регистра адреса, соединены с первыми входами узла коммутации мо ментов начала микроопераций, вторые входы которого соединены с выходами .дешифратора импульсов, а выходы узла 9 8 коммутации адреса соединены с первыми входами группы блоков элементов И, вторые входы которых соединены с выходами четвертого регистра адреса, а выходы - с информационными входами группы счетчиков, нулевые выходы кот торых через группу элементов ИЛИ подключены к второму выходу устройства и к входам элемента ИЛИ, второй выход генератора импульсов соединен с первым входом третьего элемента И, второй вход которого подключен к выходу последнего разряда третьего регистра адреса, а выход - к счетному входу счетчика и к второму входу второго элемента И, выход которого соединен с тающими входами группы счетчиков. 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что узел коммутации моментов начала микроопераций содержит группу дешифраторов, группу блоков элементов И, группу элементов ИЛИ, причем входы группы дешифраторов подключены к первым входам узда, а выходы группы дешифраторов, соединены с первыми входами группы блоков элементов И, вторые входы которых соединены с вторыми входами узла, а выходы - с входами группы элементов ИДИ, выходы которых являются выходами узла. I , Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 615480, кл. G 06 F 9/22, 1976. 2.Авторское свидетельство СССР № 64029. кл. G Об F 9/22, 1976.

Авторы

Даты

1982-07-23—Публикация

1981-01-26—Подача