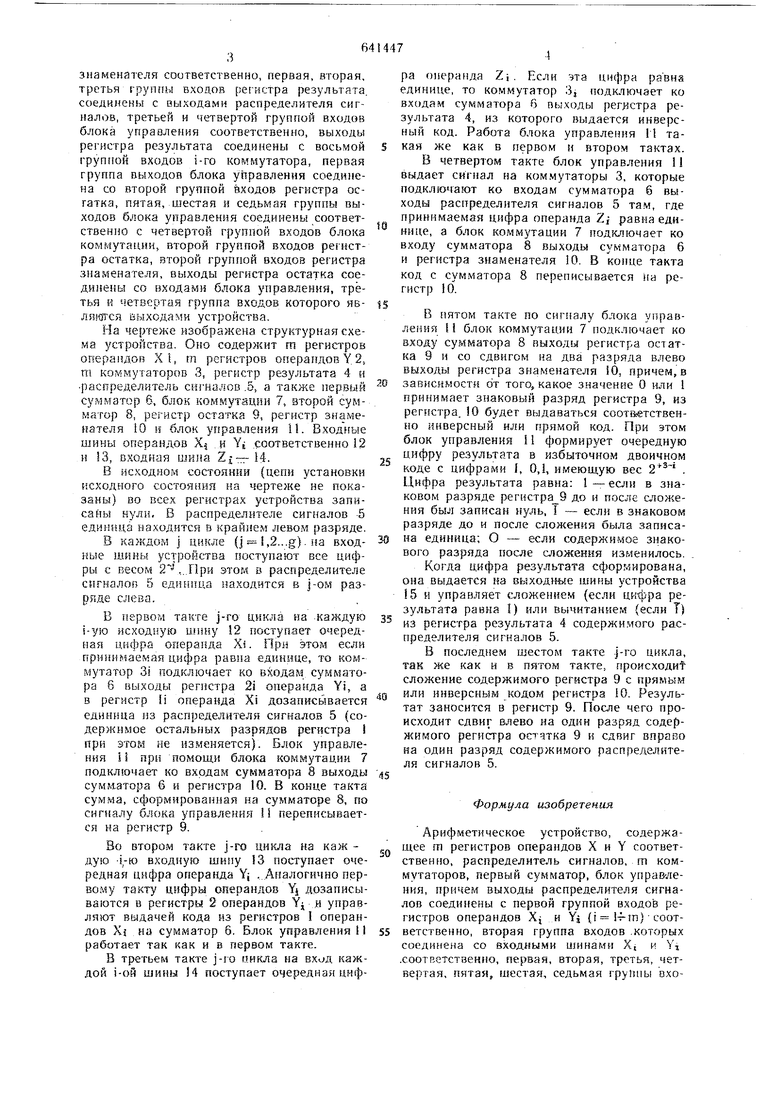

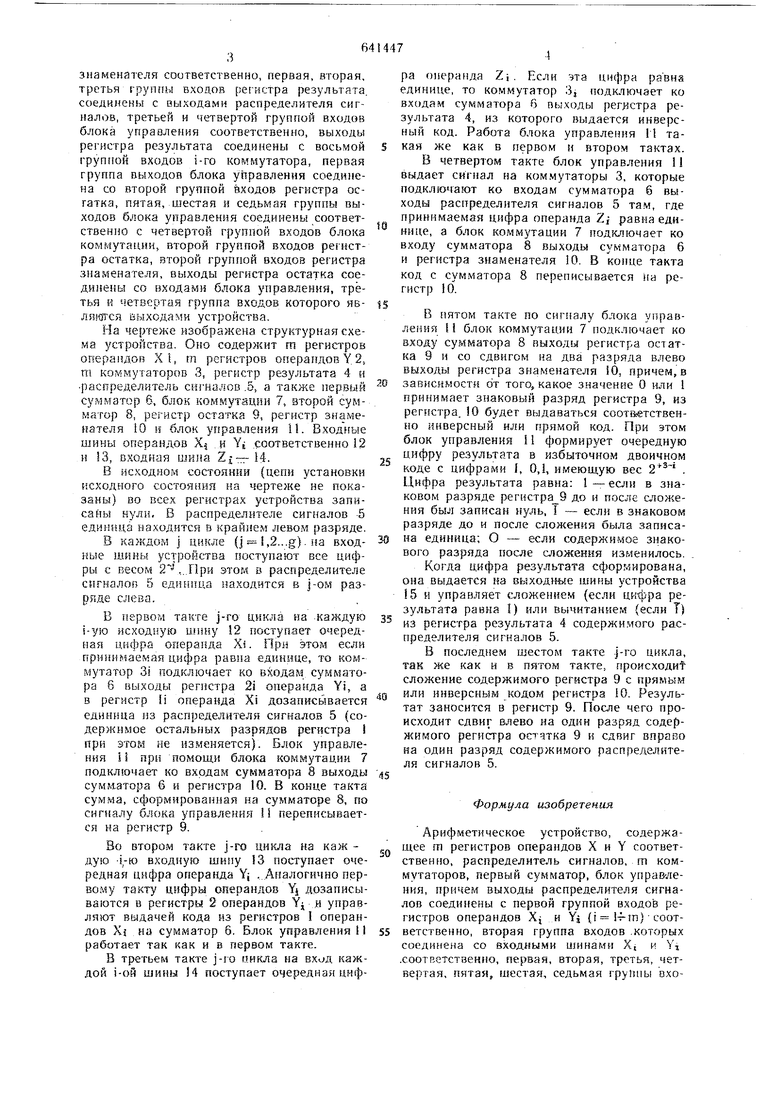

(54) АРИФМЕТИЧЕСКОЕ yCTt OftCTBO знаменателя соответственно, первая, вторая, третья группы входов регистра результата, соединены с выходами распределителя сигналов, третьей и четвертой группой входов блока управления соответствеино, выходы регистра результата соединены с восьмой группой входов i-ro коммутатора, первая группа выходов блока управления соединена со второй группой входов регистра остатка, пятая, шестая и седьмая группы выходов блока управления соединены соответственно с четвертой группок входов блока коммуталик, второй группой входов регистра остатка, второй группой входов регистра знаменателя, выходы регистра остатка соединены со входами блока управления, третья и -зетвертая группа входов которого явлпдася выходами устройства. На чертеже изображена структурная схема ycrposicTBa. Оно содержит m регистров операндов Х1, m регистров операндов Y 2, m коммутаторов 3, регистр результата 4 и распределитель сигналов .5, а также первый су.чзматор б, блок коммутащ Н 7, второй сумматор 8, регистр остатка 9, регистр знаменателя 10 и блок управления 11. Входные шины операндов Х .и Yi соответственно 12 и 13, входная шипа ZITT- Н. В исходном состоянии (цепи установки исходного состояния на чертеже не показаны) во всех регистрах устройства записаны нули, В распределителе сигналов -5 един1 и.а находится в крайнем левом разряде. В каждом j цикле (j i,2...g}. sia входные шинь устройства поступают все цифры с весом ....При этом в распределителе сигналов 5 единица находится в |-ом разряде слева. В первом такте J-ro цикла на каждую 1-ую искодиую шину 12 поступает очередная цифра операнда Xi. При этом если принимаемая цифра равна единице, то коммутатор 31 подключает ко входам сумматора 6 выходы регистра 2i операнда Yi, а в регистр П операнда Xi дозаписывается единица из распределителя сигналов 5 (содержимое остальных разрядов регистра i при этом не изменяется). Блок управления П при помощи блока коммутации 7 подключает ко входам сумматора 8 выходы сумматора 6 и регистра 10. В конце такта сумма, сформированная на сумматоре 8, по сигналу блока управления П переписывается на регистр 9. Во втором такте j-ro цикла на каж дую -i.-K) входную шину 13 поступает очередная цифра операнда Y; ....Аналогично первому такту цифры операндов Yj дозаписываются в регистры 2 операндов Yj н управляют выдачей кода из регистров 1 операндов Xj на сумматор 6. Блок управления 11 работает так как н в первом такте. В третьем такте j-ro цикла на вход каждой 1-ой шины 4 поступает очередная цифра операнда Z,. Если эта цифра равна динице, то коммутатор 3j подключает ко входам сумматора 6 выходы реультата 4, из которого выдается инверсный код. Работа блока управления Г1 такая же как в первом и втором тактах. В четвертом такте блок управления 11 выдает сигнал на коммутаторы 3, которые подключают ко входам сумматора 6 выходы распределителя сигналов 5 та.м, где принимаемая цифра операнда Zf равна единице, а блок коммутации 7 подключает ко входу сумматора 8 выходы сумматора 6 и регистра знаменателя 10. В конце такта код с сумматора 8 переписывается на регистр 10. В пятом такте по сигналу блока управления 11 блок коммутации 7 подключает ко входу сумматора 8 выходы регистра остатка 9 и со сдвигом на два разряда влево выходы регистра знаменателя iO, причем, в зависиь ости от того, какое значение О или 1 принимает знаковый разряд регистра 9, из регистра. 10 будет выдаваться соот ьетствеино инверсный или прямой код. При этом блок управления i 1 формирует очередную цифру результата в избыточном двоичном коде с цифрами I, ОД, имеющую вес . Цифра результата равна: 1-если в знаковом разряде регистра 9 до и после сложения был зап Ссан нуль, I - если в знаковом разряде до и после сложения была записана единица; О - если содержимое знакового разряда после сложения изменилось. Когда цифра результата сформирована, она выдается на выходные шины устройства 5 и управляет сложением (если цифра результата равна I) или вычитанием (если Т) из регистра результата 4 содержимого распределителя сигналов 5. В последнем шестом такте -|-го цикла, так же как и в пятом такте, npoMCxoAHf сложение содержимого регистра 9 с прямым или инверсным кодом регистра 10. Результат заносится в регистр 9. После чего происходит сдвиг влево на один разряд содержимого регистра остатка 9 и сдвиг вправо на один разряд содержимого распределителя сигналов 5. Формула изобретения Арифметическое устройство, содержащее m регистров операндов X и Y соответственно, распределитель сигналов, , m коммутаторов, первый сумматор, блок управ-ления, причем выходы распределителя сигналов соединены с первой группой входов регистров операндов Xj и Yj (i ) соответственно, вторая группа входов .которых соединена со входными шинами Xt и YI .соответстаенно, первая, вторая, третья, четвертая, пятая, шестая, седьмая группы оходов 1-го коммутатора с(№дииеиы cooi ветственно с п(фвой группой выходов блока управления, входной шиной Zi .входной шиной Xj, входной шиной Yj , выходами регистра операндов Xj .выходами регистра операндов YI, выходами распределителя сигналов, вторая группа входов которого соединена со второй группой выходов блока управления,отличающееся тем, что, с целью расширения функциональных возможностей устройства,

т

за счет получения функции вида ст j,

tfz,

в устройство введены регистр результата, регистр остатка, регистр знаменателя, блок коммутации, второй сумматор, причем, выходы первого сумматора соединены с первой группой входов блока коммутации, вторая, третья и четвертая группы входов которого соответственно соединены с выходами регистра знаменателя, регистра остатка, третьей группой выходов блока управления, а выходы блока коммутации соедине}5ы со входами второго сумматора, выходы которого соединены с первой группой входов регистра остатка и регистра знаменателя

/,

соответственно, первая, вторая, т)сгья группы входов регистра результата соединеии с выходами распределителя сигналов, третьей и четвертой группой входов блока управле1 ия соответственно, вых)ды регистра результата соединены с восьмой группой входов i-ro коммутатора, первая группа выходов блока управления соединена со второй группой входов регистра остатка, пятая, шестая и седьмая группы выходов блока управления соединены соответственно с четвертой группой входов блока коммутации, второй группой входов регистра остатка, второй группой входов регистра знаменателя, выходы регистра остатка соединены со входами блока управления третья и четвертая группа входов которого являются выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 415088,кл. G 06 F 5/20, i974.

2..Авторское свидетельство СССР по заявке № 2353798/18--24, кл. G Об F 7/39, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое вычислительное устройство | 1976 |

|

SU593211A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Устройство для вычисления дробнойРАциОНАльНОй фуНКции | 1979 |

|

SU842796A1 |

| Арифметическое устройство | 1981 |

|

SU993252A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для возведения в степень | 1976 |

|

SU888106A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

Авторы

Даты

1979-01-05—Публикация

1976-05-07—Подача