(54) АРИ Е ШТИЧЕСКОЕ УСТРОЙСТВО .

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Арифметическое устройство | 1976 |

|

SU703804A1 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для быстрого преобразования фурье | 1981 |

|

SU1018123A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

Изобретение относится к вычислительной технике и может быть использовано для выполнения операций сложения, вычитания, умножения, деления и извлечения корня при обработке больших массивов многоразрядных чисел.

Известно матричное арифметическое устройство .

Однако устройство не имеет высокой производительности при обработке массива чисел, так как выполнение операций над очередной парой чисел можно производить лишь тогда, когда будет получен предыдущий результат.

Известно арифметическое устройство, которое содержит п последовательно соединенных однотипных блоков, каждый из которых содержит два регистра, формирователь (п+1) старших разрядов, два триггера и элемент .

Однако устройство предназначено для обработки массива чисел одновременно, а не массива из пар чисел, и кроме того, не может выполнять операции деления и извлечения корня квадратного.

Наиболее близким к предлагаемому является арифметическое устройство, которое содержит п однотипных последовательно соединенных ретдающих блоков, каясдый из которых содержит три триггера, сумматор, элементы И-ИЛИ, а также логический узел, содержащий два элемента И, прямой и инверсный выходы которых объединены элементом ИЛИ ,

Недостатком этого устройства является недостаточное быстродействие10при выполнении операции деления и извлечения корня квадратного, которые выполняются за два полутакта. Кроме того, при выполнении этих опе раций необход1:мо сдвигать данные

15 два раза влево в первом регистре каждого блока, что также приводит к снижению быстродействия.

Цель изобретения - повышение быст20 родействия устройства при вьшолнении операции деления- и извлечения корня квадратного.

Поставленная цель достигается тем, что в арифметическом устройстве, содержащем п последовательно соединенных решающих блоков (п - разрядность операндов), состоящих из трех регистров, сумматора, коммутаторов, и п логических узлов, содержащих элемент ИЛИ и два элемента И,

30 выходы которых соединены с входами

элемента ИЛИ, причем выходы логических узлов соединены с входами разрядов второго регистра первого решающегЧэ блока, выходы разрядов первого регистра k-ro блока (где k l,...,tj| соединены с первыми входами соответствующих разрядов сумматора, прямые выходы разрядов второго регистра k-ro решающего блока соединены с входами разрядов второго регистра (k+l)-ro решающего блока, инверсный и прямой выходы (k+l)-ro разряда второго регистра k-ro решающего блока соединены с информационными входами первого коммутатора, управляющие входы которого соединены с первой и второй управляющими шинами устройства, выход первого коммутатора соединен с вторым входом (k+ 1)-г разряда сумматора, прямые выходы k-x разрядов третьего регистра k-ro решающего блока соединены с входами (k-O-ых разрядов третьего регистра (k+1)-ro решающего блока, выход второго коммутатора k-ro решающего блока соединен с входом k-ro разряда второго регистра (k+1)-ro решающего блока, первый информационный вход второго коммутатора k-ro блока соединен с прямым выходом k-ro разряда второго регистра k-ro блока, первый управляющий вход второго коммутатора соединен с второй управляющей шиной устройства, каждый решающий блок дополнительно содержит третий коммутатор, причем информационные входы k-ro разряда третьего коммутатора соединены с выходом (k-l)-ro разряда первого регистра, с выходом (k+1)-ro разряда первого регистра, с выходом (k-l)-ro разряда сумматора, с выходом {k+l)-ro разряда сумматора, управляющие входы третьего коммутатора соединены с прямыми и инверсными выходами знакового разряда сумматора и первого разряда третьего регистра и с третьей и четвертой управляющими шинами устройства, выход k-ro разряда третьего коммутатора k-ro ретиающего блока соединен с входом k-ro разряда первого регистра (k+l)-ro решающего блока, инверсный выход знакового разряда сумматора k-ro блока соединен с входом п-го разряда третьего регистра (k+O-ro блока и с вторым информационным входом второго коммутатора, второй управляющий вход которого соединен с первой управляющей шиной устройства, инверсные выходы всех разрядов второго регистра k-ro блока, кроме (k+1)разр5ша, соединены с вторыми входами сумматора.

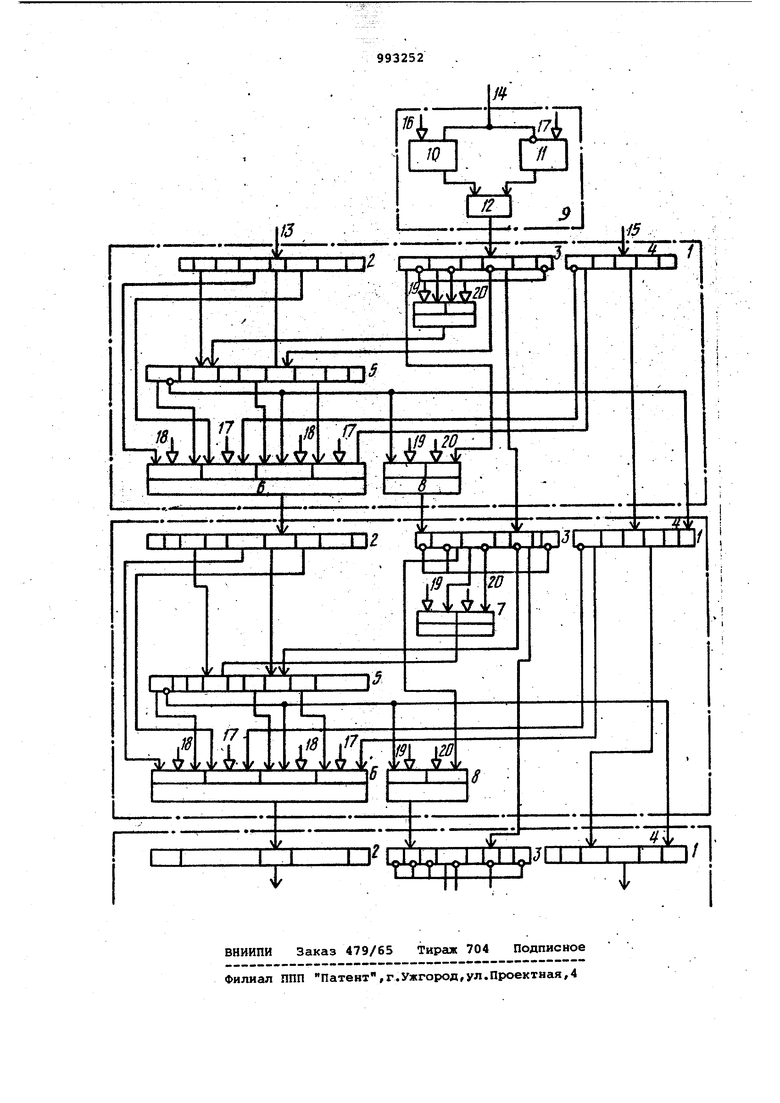

На чертеже представлена функциональная схема арифметического устрой ства.

Устройство содержит п решающих блоков 1, каждый из которых содержит

регистры 2-4, сумматор 5, коммутаторы 6-8. Кроме того, устройство содержит п логических узлов 9, содержащих элементы И 10 и 11 и элемент ИЛИ 12, входные шины 13-15, управляющие шины 16-20. Блок 1 содержит коммутатор 6, имеющий п разрядов, и одноразрядные коммутаторы 7 и 8. Выход (k-l)-ro разряда регистра 2 соединен с первым информационным входом k-ro разряда коммутатора б, управляющие входы которого соединены с управляющей шиной 18 (операции Деление, извлечение корня) и с прямым выходом знакового разряда сумматора Выход (Ц+1)-горазряда регистра 2 соединен с вторым информационным входом k-ro разряда коммутатора 6, управляющие входы которого соединены с шиной 17 (Умножение) и с ин- версным выходом первого разряда регистра 4. Выход (k-l)-ro разряда сумматора 5 соединен с третьим информационным входом k-ro разряда коммутатора 6, управляющие входы которого соединены с шиной18 и инверсным выходом знакового разряда сумматора 5. Выход (k+O-ro разряда сумматора 5 соединен с четвертым информационным входом k-ro разряда коммутатора 6, управляющие входы которого соединены с шиной 17 и с прямым выходом первого разряда регистра 4. Выход k-ro разряда регистра 2 соединен с первым входом k-ro разряда сумматора 5, второй вход которого соеди.нен с инверсным выходом k-ro разряда регистра 3, кроме второго разряда в первом блоке 1, третьего разряда во втором-блоке 1 и п-го разряда в (п-1)-ом блоке 1. В каждом из блоков 1 прямой выход этих разрядов соединен с первым информационным входом коммутатора 7, первый управляющий вход которого соединен с шиной 19 (Извлечение корня), а инверсньхй выход - с вторым информационным входом коммутатора 7, второй управляющий вход которого соединен с шиной 20 (Деление, умножение). Выход коммутатора 7 соединен с вторым входом соответствующего разряда сумматора 5. Выходы k-x разрядов коммутатора б соединены с входами соответствующих разрядов регистра 2 последующего блока 1.

Инверсные выходы k-x разрядов регистра 3 каждого предыдущего блока 1 соединены с входами k-x разрядов регистра 3 последующего блока 1, кроме первого разряда во втором блоке 1 второго разряда в третьем блоке 1 и т.д. Входы этих разрядов соединены с выходом коммутатора 8, первый информационный вход которого соеди.нен с инверсным выходом знакового разряда сумматора 5, первый управлягаций вход - с шиной 19, второй информационный вход коммутатора 8 соединен с инверсным выходом первого раз ряда первого блока 1 (второго разряда второго блока 1 и; т.д.), а второй управляющий вход - с шиной 20. Выход 1с-го разряда регистра 4 каждого предыдущего блока 1 соединен с входом (k-1}-ro разряда регистра 4 последующего блока 1. Вход п-го разряда регистра 4 последуквдего блока 1, начиная с второго блока 1, соединен с инверсным выходом знакового разряда сумматора 5 предыдущего блока 1. При сложении, вычитании, делении входами устройства являются шины 13 и 14. При этом логический узел 9 пропускает через элемент ИЛИ 12 прямлв. (через элемент И io) или инверсные (через элемент И 11) значения входных сигналов. При умножении входами устройства являются шины 14 и 15, при извлечении корня квадратного шина 13. Перед началом работы все регистры сбрасываются в нулевое состояние .

При умножении в первом такте первое множимое, поступающее по тине 14 проходит на регистр 3 череа элементы И 11, ИЛИ 12, а первый множитель по шине 15 на регистр . 4, причем первый разряд - мпадший разряд множителя.

Содержимое регистра 3 проходит на сумматор 5, где складывается с нулевыми значениями регистра 2. Если первый разряд множителя регистра 4 равен 1, то коммутатор б пропускает На регистр 2 второго блока сдвиг нутое значение сумматора 5. Если первый разряд множителя равен О, то коммутатор 6 пропускает сдвинутое значение регистра 2,

Сдвиг операндов вправо обеспечен соединением разрядозв регистра 2 и сумматора 5 с коммутатором 6, а также соединением регистров 4 соседних блоков 1. . .

Во втором такте содержимое первого блока 1 переписывается во второй блок 1, а в первый блок 1 поступает вторая пара операндов. В первом блоке 1 получают в сумматоре 5 первую частичную сумму произведения первой пары чисел. Во вторрм блоке полученную jpaHee первую частичную сумму, записанную в регистр 2, складывают в сумматоре 5 с содержимым регистра 3. В зависимости от значения второго разряда первого ишржимого (регистр 4) в сумматоре 5 получают вторую частичную суыму произведения первой пары чисел (производится сложение или сдвиг операндов).

При п-разрядных входных операндах результат вычислений первой пары чисел получают на выходе сумматора 5П-ГО блока через п тактов, а всех

последующих пар чисел - через один такт. При делении первое делимое записывают в регистр 2, а первый делитель - по шине 14 в регистр 3 через элементы И 10, ИЛИ 12 делителя. Деление выполняют с восстановлением остатка. В первом такте в сукматоре 5 вычитают из первого делимого инверсные значения первого делителя. Если остаток получился положительный,

0 разряд частногоравен единице, и коммутатор б пропускает содержимое сумматора 5 со сдвигом под управлением инверсного выхода знакового разряда сумматора 5. Если остаток отрицатель5ный, разряд частного равен нулю, коммутатор б пропускает содержимое регистра 2 со сдвигом под управлением прямого выхода знакового разряда сумматора 5, т.е. происходит восстановление остатка и сдвиг его. Сдвиг

0 операндов влево обеспечивается соединением регистра 2 и cyhe aTopa 5с коммутатором б.

Во втором такте первый остаток . от деления первой пары чисел перепи5сывается в регистр 2 второго блока 1 из кокв 1утатора б, первый делитель переписывается в регистр 3, а первая цифра частного - в п-й (старший) разряд регистра 4второго блока 1, как

0 значение инверсного выхода знакового разряда сумматора 5 первого . В сумматоре 5 второго блока 1 получают второй остаток от деления первой пары чисел и вторую цифру частного.

5 Одновременно в регистры 2 и 3 первого блока 1 записывают вторую пару операндов и получают первый остаток , от деления второй пары операндов и первую цифру частного.

0

Результат вычислений первой пары чисел получают на выходе регистра 4 п-го блока 1 через п тактов, а результат вычислений последукяцих пар чисел - через каждый такт.

5

При извлечении квадратного корня в первом такте первое подкоренное . выражение поступает в регистр -2 по шине 13,.а затем в сумматор 5, где происходит вычитание инверсных зна0чений регистра 3 с пропуском второго разряда, т.е. числа 1011111.... Если остаток сумматора 5 положителен (знак су№лы равен нулю), информация с выходов сумматора 5 поступает на

5 коммутатор б под управлением инверсг ного выхода знакового разряда сумматора 5. При этом первое число результата равно единице и оно поступает на коммутатор 8 под управлени0ем шины 19. Если остаток сумматора 5 отрицателен, происходит восстановление остатка и сдвиг его влево за счет пропускания через коммутатор 6 содержимого регистра 2 bo сдвигом

5 под управлением шины 18 и прямого

выхода знакового разряда сумматора 5 причем число результата равно нулю.

Во втором такте содержимое блока 1череписывается в регистр 2 следующего блока 1, а в регистр 2 первого блока 1 записывается второе подкоренное выражение. В первом блоке 1 вычисляют первый чаетнйй результат второго операнда, а во втором блоке 1 вычисляют второй частный результат из первого подкоренного выражения. Окончательный результат извлечения корня получают на выходе регистра 3 п-го блока 1 в прямом коде. ;

В предлагаемом устройстве повышено быстродействие по сравнению с прототипом, которое. определяется од- ним тактом обработки данных в одном блоке. По сравнению с прототипом быстродействие предлагаемого арифметического устройства увеличено в 3,5 раз а. при выполнении операций делений и извлечения корня квадратного за счет обеспечения, вычитания без вое- : становления остатка в каждом решающем блоке конвейера. Устройство предназначено для работы в специализированных быстродействующих устройствах обработки больших массивов многоразрядных чисел. Специализированные устройства, работающие совместно с ЭВМ, выполняют однородные частоповторякициеся операции вместо ЭВМ, в которой записаны массивы обрабатываемых данных.

Формула изобретения

Арифметическое устройство, содержащее п последовательно соединенных решающих блоков (п-разрядность операндов ), состоящих из трех регистров сумматора, коммутаторов, п логических узлов, содержащих элемент ИЛИ и два элемента И, выходы которых соединены с входами элемента ИЛИ, причем выходы логических узлоь соединены с входами разрядов второго регистра первого решающего блока, выходы разрядов первого регистра k-ro блока (где k 1, ..., п) соединены с первыми входами соответствующих разрядов сумматора, прямые выходы разрядов второго регистра k-ro решающего блока соединены с входами разрядов второго регистра (k+1)-ro решающего блока, инверсный и прямой выходы (k+l)-ro разряда .второго регистра k-ro решающего блока соединены с информационными входами первого коммутатора, управляющие входы которого соединены с первой и второй управля-ющими шинами устройства, выход первого коммутатора соединен с вторым

входом (k+l)-ro разряда сумматора прямые выходы k-x разрядов третьего регистра решающего блока соединены с входами (k-l)-x разрядов третьего регистра (k+1)-ro решающего бло0 ка, выход второго коммутатора k-ro р ающего блока соединен с входом k-To разряда второго регистра (k+O-ro .решающего блока, первый информационный вход второго коммутатора k-ro ,

5 блока соединен с прямым выходом k-ro разряда второго регистра k-ro блока, первый управляющий вход второго коммутатора соединен с второй управляющей шиной устройства, о т л и ч аQ ю щ е е с я тем, что, с цель1о повышения быстродействия, каждый решающий блок дополнительно содержит третий коммутатор, причем информационные входы k-ro разряда третьего ком5 мутатора соединены с выходом (k-l)-ro разряда первого регистра, выходом (k+1)-ro разряда первого регистра, с выходом (k-O-ro разряда сумматора, с выходом Ik+O-ro разряда

сумматора, управляющие входы третьего коммутатора соединены с прямыми и инверсными выходами знакового разряда сумматора и первого разряда третьего регистра и с третьей и четвертой управляннцими шинами устрой5 ства, выход k-ro разряда третьего коммутатора k-ro реаакяцего блока соединен с входом k-ro разряда первого регистра (k-fO-ro решающего блока, инверснЁЛй выход знакового разряда

0 сумматора k-ro блока соединен с входом n-j разряда третьего регистра (k+1)-ro блока и с вторым информа. ционным входом второго коммутатора, второй управляющий вход которого со5 единен с первой управляющей шиной устройства, инверсные выходы всех разрядов второго регистра k-ro блока, кроме (k+1)-ro разряда, соединены с вторыми входами сумматора.

0 Источники информации,

принятые во внимание при экспертизе

; .798825, кл. G Об F 7/38, 1979 (прототип) .

/

Авторы

Даты

1983-01-30—Публикация

1981-08-03—Подача