Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах высокой производительности для деления больших массивов чисел в формате с плавающей запятой.

Цель изобретения - расширение функциональных возможностей устройства за счет деления массивов чисел в формате с плавающей запятой.

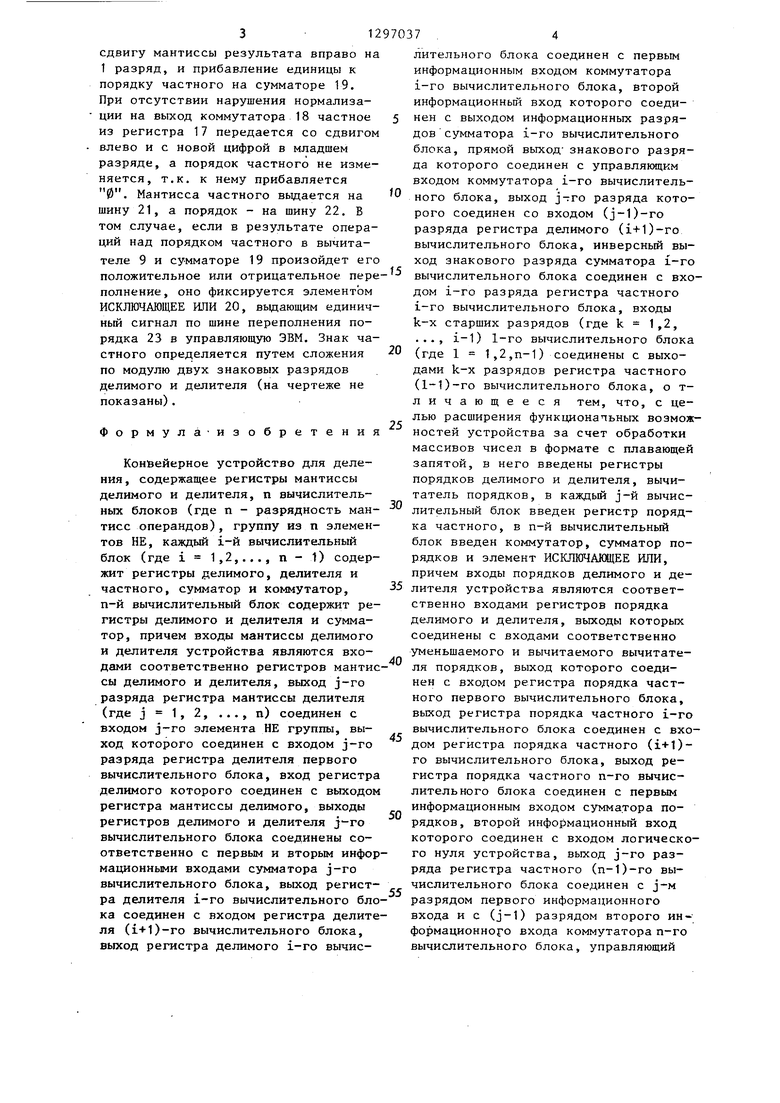

На чертеже представлена функциональная схема конвейерного устройства для деления.

Устройство содержит входы 1-4 мантиссы делимого, порядка делимого, мантиссы делителя и порядка делителя регистры 5-8 мантиссы делимого, порядка делимого, мантиссы и порядка делителя, вычитатель 9 порядков, группу элементов НЕ 10, и п вычислительных блоков 11,- 11п (п - разрядность обрабатываемых мантисс), кажды из которых содержит регистры 12-14 делимого, делителя и порядка частного, сумматор 15, (п-1) вычислительных блоков 11,- 11п-1 кроме последнего, содержат коммутатор 16 и регистр 17 частного, п-й вычислительный блок 11„ содержит коммутатор 18, сумматор 19 порядка, элемент 20 ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы 21-23 мантиссы частного, порядка частного и переполнения порядка, вход 24 логического О.

Устройство работает следующим образом.

Деление выполняется по формуле

РА - Р.

,.

м

в

где М , Мц, Mj, - мантиссы делимого, делителя и частного соответственно, Рд, Pg, Pj, - порядки делимого,

делителя и частного соответственно.

Мантиссы операндов и результата представлены в прямом коде со знаком порядки - в дополнительном коде. Процесс деления для каждой пары чисел, включая округление, длится (п+1) тактов.

В первом такте по фронту синхроимпульса в регистры 5, 6, 7 и 8 поступают с входных шин мантиссы и порядки делимого и делителя соответственно. Мантиссы должны быть нормализованы:

I М 1 .

5

0

5

На вычитателе 9, имеющем дополнитель- ньш знаковый разряд, образуется разность порядков (Рд - Рц) в модифицированном дополнительном коде, которая по фронту второго тактового импульса записывается в регистр порядка частного 14 первого вычислительного блока 11,.. Одновременно в регистр 12 этого блока заносится мантисса делимого, а в регистр 13 - проинвертиро- ванная элементами НЕ 10 мантисса делителя. В последующие (п-1) тактов в вычислительных блоках 11 конвейера выполняется деление мантисс с восстановлением остатка. В каждом такте из частичного остатка, поступающего из регистра 12, на сумматоре 15 вы- читается делитель (на входе переноса сумматора 15 постоянно присутствует 1). Если остаток получился положительный, т.е. в знаковом разряде сумматора 15 - /5, то разряд частного равен 1, он поступает в младший разряд регистра 17 частного.

0

Новый остаток с выходов сумматора проходит через коммутатор. Если остаток отрицательный, разряд частного равен нулю, и через коммутатор передается первоначальньш остаток из регистра 12 (в первом блоке 11 это делимое), т.е. происходит восстановление остатка. В следующем такте информация с выхода коммутатора 16 переписывается в регистр 12 следую- 5 щего блока со сдвигом влево на одир разряд, делитель передается в регистр 23, а порядок частного - в регистр 14 следующего блока 11 без изменения. В этом же такте записывается очередная цифра частного в последний разряд регистра 17 того же блока. При передаче частного в следующий блок оно сдвигается влево на один разряд.

В последнем п-м блоке 11, вычисляется последняя цифра частного и производится его нормализация.

Так- как. М, и Mg нормализованы, то

0

5 I

50 1 ,м

2-2

-n-t-t

Следовательно, нарушение нормализации может произойти только влево и только на один разряд. Б этом слу- j чае в старшем разряде регистра частного 17 (п-1)-го блока присутствует 1, которая вызывает передачу частного с регистра 17 через коммутатор 18 без сдвига, что соответствует

сдвигу мантиссы результата вправо на 1 разряд, и прибавление единицы к порядку частного на сумматоре 19. При отсутствии нарушения нормализации на выход коммутатора 18 частное из регистра 17 передается со сдвигом влево и с новой цифрой в младшем разряде, а порядок частного не изменяется, т.к. к нему прибавляется 0. Мантисса частного выдается на шину 21, а порядок - на шину 22. В том случае, если в результате операций над порядком частного в вычита- теле 9 и сумматоре 19 произойдет его положительное или отрицательное пере полнение, оно фиксируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 20, вьщающим единичный сигнал по шине переполнения порядка 23 в управляющую ЭВМ. Знак частного определяется путем сложения по модулю двух знаковых разрядов делимого и делителя (на чертеже не показаны).

Формула-изобретения

Конвейерное устройство для деления, содержащее регистры мантиссы делимого и делителя, п вычислительных блоков (где п - разрядность мантисс операндов), группу из п элементов НЕ, каждый i-й вычислительный блок (где i 1,2,..., п - 1) содержит регистры делимого, делителя и частного, сумматор и коммутатор, п-й вычислительный блок содержит регистры делимого и делителя и сумматор, причем входы мантиссы делимого и делителя устройства являются входами соответственно регистров мантиссы делимого и делителя, выход j-ro разряда регистра мантиссы делителя (где j 1, 2, ..., п) соединен с входом J-го элемента НЕ группы, выход которого соединен с входом j-ro разряда регистра делителя первого вычислительного блока, вход регистра делимого которого соединен с выходом регистра мантиссы делимого, выходы регистров делимого и делителя вычислительного блока соединены соответственно с первым и вторым информационными входами сумматора j-ro вычислительного блока, выход регистра делителя i-ro вычислительного блока соединен с входом регистра делителя (1+1)-го вычислительного блока, выход регистра делимого i-ro вычисfO

t5

20

25

лительного блока соединен с первым информационным входом коммутатора i-ro вычислительного блока, второй информационньм вход которого соединен с выходом информационных разрядов сумматора i-ro вычислительного блока, прямой выход- знакового разряда которого соединен с управляющим входом коммутатора i-ro вычислительного блока, выход j-ro разряда которого соединен со входом (j-l)-ro разряда регистра делимого (i+1)-ro вычислительного блока, инверсный выход знакового разряда сумматора i-ro вычислительного блока соединен с входом i-ro разряда регистра частного i-ro вычислительного блока, входы k-x старших разрядов (где k 1,2, ..., i-1) 1-го вычислительного блока (где 1 1,2,п-1) соединены с выходами k-x разрядов регистра частного (l-l)-ro вычислительного блока, о т- личающееся тем, что, с целью расширения функционатьных возможностей устройства за счет обработки массивов чисел в формате с плавающей запятой, в него введены регистры порядков делимого и делителя, вычи- татель порядков, в каждый j-й вычислительный блок введен регистр порядка частного, в п-й вычислительный блок введен коммутатор, сумматор порядков и элемент ИСКЛЮЧАКЩЕЕ ИЛИ, причем входы порядков делимого и де- 35 лителя устройства являются соответственно входами регистров порядка делимого и делителя, выходы которых соединены с входами соответственно уменьшаемого и вычитаемого вычитате- ля порядков, выход которого соединен с входом регистра порядка частного первого вычислительного блока, выход регистра порядка частного i-ro вычислительного блока соединен с входом регистра порядка частного (1+1)- го вычислительного блока, выход регистра порядка частного п-го вычислительного блока соединен с первым информационным входом сумматора порядков , второй информационный вход которого соединен с входом логического нуля устройства, выход j-ro разряда регистра частного (п-1)-го вычислительного блока соединен с j-M разрядом первого информационного входа и с (J-1) разрядом второго ин- формационноро входа коммутатора п-го вычислительного блока, управляющий

30

40

45

50

55

вход которого соединен с выходом старшего разряда регистра частного (n-t)-ro вычислительного блока и входом переноса сумматора порядков, выход которого является выходом порядка частного устройства, инверсный выход знакового разряда сумматора п-го вычислительного блока соединен с п-м разрядом второго информацион1297037 6

ного входа комммутатора п-го вычислительного блока, выход квто рого является выходом мантиссы частного устройства, выходы двух знаковых разря- 5 дов сумматора порядка соединены с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом признака переполнения порядков устройства.

to

Редактор Л.Повхан

Составитель Н.Маркелова

Техред М.Ходанич Корректор М.Демчик

Заказ 781/51Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| Векторное устройство для деления | 1984 |

|

SU1259250A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для деления | 1980 |

|

SU898425A1 |

| Устройство для деления с плавающей запятой | 1979 |

|

SU860063A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для деления чисел | 1981 |

|

SU970356A1 |

| Устройство для деления | 1988 |

|

SU1621034A1 |

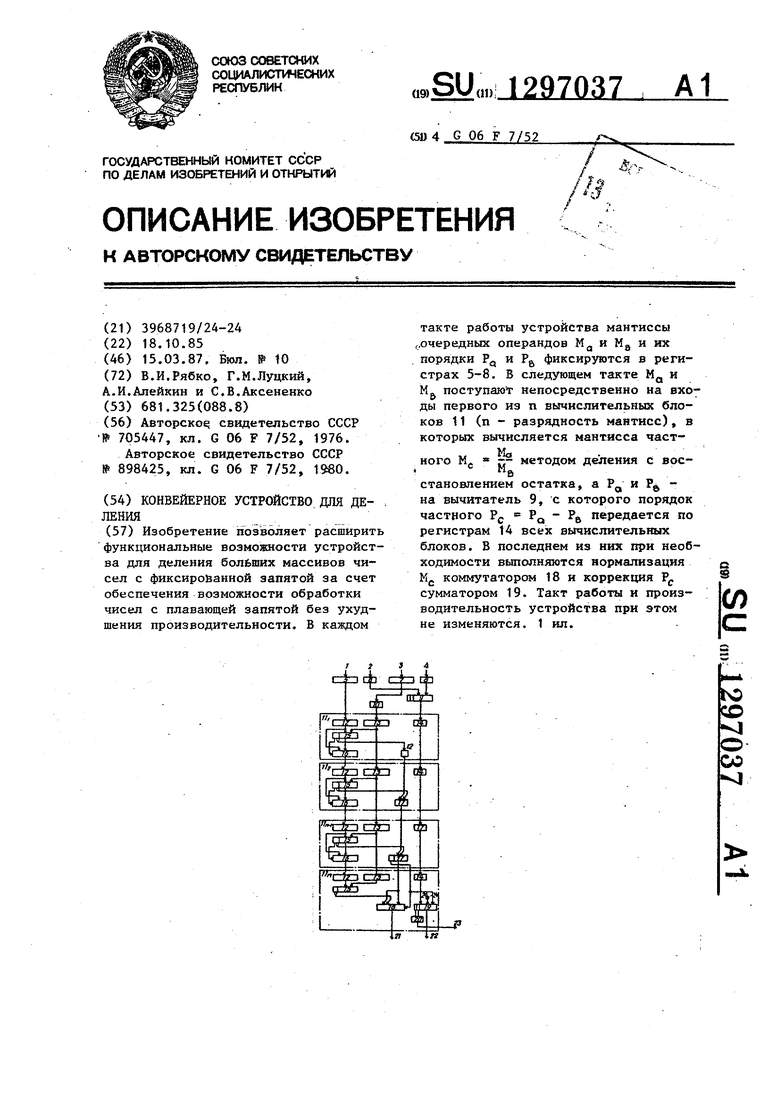

Изобретение позволяет расширить функциональные возможности устройства для деления больших массивов чисел с фиксированной запятой за счет обеспечения возможности обработки чисел с плавающей запятой без ухудшения производительности. В каждом 1 i 34 Гд1 / у i СП 1 ... tT такте работы устройства мантиссы f,очередных операндов Мд и Мц и их порядки PQ и Pg фиксир тся в регистрах 5-8. В следующем такте Мд и М. поступаю г непосредственно на входы первого из п вычислительных блоков 11 (п - разрядность мантисс), в которых вычисляется мантисса частного М, Ма П методом деления с вос- - й становлением остатка, а Р, и Р на вычитатель 9, с которого порядок частного Pg PQ - Ре передается по регистрам 14 всех вычислительных блоков. В последнем из них при необходимости выполняются нормализация Kg коммутатором 18 и коррекция Р сумматором 19. Такт работы и производительность устройства при этом не изменяются. 1 ил. СЛ tt

| Устройство для деления | 1976 |

|

SU705447A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1980 |

|

SU898425A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-18—Подача