1

изобретение относится к радиотехнике и может быть использовано в системах автоматики, в приемно-передающих устройствах и в измерительной технике.

Известен цифровой синтезатор частот, содержащий перестраиваемый генератор, к управляющему входу которого пошслю- чен выход фильтра нижних частот, а выход перестраиваемого генератора через управляемый делитель частоты соединен с первыми входами первого и второго им- пульсно-фазовых детекторов, к вторым входам которых подключены выходы первого и второго делителей частоты соответственно, входы которых соединены с выходом генератора опорной частоты,при этом поразрядные входы всех делителей частоты соединены с выходами управлшощего блока ij .

Однако в известном устройстве с целью получения малого шага перестройки частоты при высоком значении опорных частот используется несколько контуров фазовой автоподстройки.

Целью изобретения $голяется получение шага перестройки частоты, меньшего чем разность опорных частот на вторых входах импульсно-фазовых детекторов.

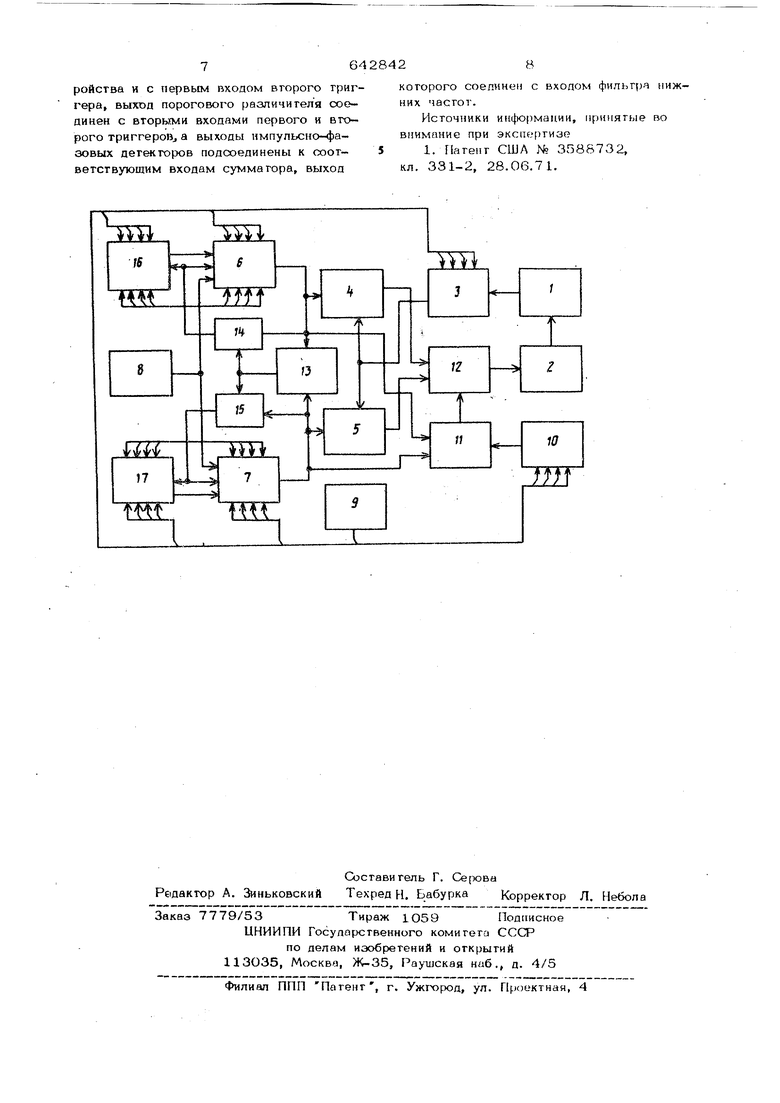

Цля этого в цифровой синтезатор частот, содержащий перестраиваемый генератор, к управляющему входу которого подключен выход фильтра нижних частот, а выход перестраиваемого генератора через управляемый делитель частоты соединен с первыми входами первого и второго импульсно-фазовых детекторов, к вторым входам которых подключены выходы первого и второго делитолей частоты соответственно, входы которых соединены с выходом генератора опорной частоты, при этом поразрядные входы всех делителей частоты соединены с вь|ходами управляющего блока, введены последовательно соединенные цифроана- поговый преобразователь, стробирующее устройство .и сумматор, а также порого вый различитель, первый и второй триггерыя первое и второе устройствадля nopaapfeiHoro совпадений, выходы которых соедйненм с усгановочными входами первого и второго делителей частоты соответственно, при этом выход первого триггера подсоединен к .управляющим вхо дам первого делителя частоты я первого устройства для поразрядного совпадения, выход 8горогчз| триггера соединен с управляющими входами второго делителя частоты и второго устройства для поразрядного совпадения, к выходу управляющего блока п,с дключены также разрядные входы .. цифроаналогоБого, преобразователя; и первые разр$1дные входы первого и второго устрсйствI для пораарядного сов падения, вторые разрядные входы которь х соединен. с разрядными выходами первого и вгорого делателей частоты со огветсгвеннор выход первого аеп игеля частоты соедк:нен также с первыми вхо дамй порогового различигеля сгробирующего устройс1ва к первого трлгтера, вы ход второго делателя частоты соеданен с вторыми входами порогового различите Ли и стробярующего устройства и с пер БЬШ1 входом второго триггера, выход поро гового раапичжгеяя .соейннен е вгорьили входами первсго я вт-орого триггеров, а выходы ймпульсно-(|)азовых детекторов подсоедйвены к соответствующим входам сутчалагорвг, выход которого соединен с вхойоы фвльтра НИЖНИХ частот. На чертеже приведена структуриан электрическаа схема синтезатора. Цифровой Синтезатор частот содер-лсит пересгранваемьгй генератор 1, к управля ютдему входу :5оторого поиключеп выход фзльгра 2. HH5iiHaxt4acTors, а выход пере-ч страиваемого генератора 1 через управляемьй йелйТ Э1ь 3 частоты соединен с первыми входгшй первого 4 и вгорого 5 ймпульсно- фа овых детекторов, к вторым : входам ко торЬЕХ подключены выходы первого 6 и второго 7 деаителей частоты |соо1-В9ТСТБенн 5 входы которых сое динены с выходом генератора 8 опорной чао тоты, при Qfou поразрядные входы всех -делателей Sj 6 и частоты соединены с |выходакш у51р 1впшощего блока 9 послеДовательво соединенные йи оаналоговый преобршаователь lOj стробирующее устройсгво 11 и сумматор I2j а также по роговый разяичйтель 13, первый 14 и второй 15 трггеры, первое 16 и вто рое 17 устройства для поразрядного СОБ падения, выходы которых соединены с усгааовочнымв: входами первого 6 я вто 64 2.4 ого 7 делителей частоты, при этом выОД первого триггера 14 подсоединен к управляющим входам первого делителя астоты 6 и первого устройства для поразрядного совпадения 18, выход второо триггера 15 соединен с управляющими ходами вТорогчз делителя частоты 7 и второго устройства для поразрядного совпадения 17, к выходу управляющего блоха 9 подключены также разрядные входы цифроаналогового преобразователя Ю, и первые разрядные входы первого 16 н второго 17 устройств для поразрядного совпадения, вторые разрядные входы которых соединены с разрядньп ли выходами первого б и второго 7 делителей частоты, выход первого делителя частоты 6 соединен также с первыми входами порогового различителй 13, стробирующего устройства 11 и первого триггера 14, выход второго делителя 7 частоты соединен с вторыми входами порогового раз- лйчителя 13 и .стробирующего устройства 11 и с первым входом второго триггера 15, выход порогового раа;яичителя 13 соединён с вторыми; входами первого 14 щ второго 15 триггеров, а выходы импульсно- |зазо0Ь5Х детекторов 4- и 5 подсоединены к соответствующим входам сумьхатора 12 выход которого соединен с входом фильтра 2 нижних частот. Слштезатор работает следующим образом. В первый момент производится задание Ha4iMbHbix временных соотношений между сигналами, которое осуществляет ся установкой управляемого делителя 3 и первого 6 и второго 7 делителей часто ты в начальные состояния управляло щим блоком 9. Это производится с той яепыо, чтобы в момент начала работы на входах импуяьсно-фазовых детекторов 4 и S импульс перестраиваемого генератора 1, прошедший через управляемый делитель 3с коэффициентом деления М, во времени находился между опорными i импульсами, сформароваиньшм. из сигнала генератора 8 liyтем деления на первом и втором делителях частоты 6 и 7 с коэффициентам деления равными соответственно М„и NJ. На выходе первого импульсно-фазового детектх ра 4 формируется сигнал с длительностью импульсов, равной временному рассогласованию опорных импульсов с первого делителя частоты 6 и поделен-т ных импульсов перестраиваемого генератора 1, а на выходе второго ямпульснофазового дегекгора 5 формируется сигнал Q длительностью импульсов, равной временному рассогласованию между поделенными нмйульсамй перестраиваемого генератора 1 и опорными импульсами с второго делителя частоты 7, Щзн суммировании этих сигналов на выходе сумматора 12 образуется сигнал с периодически измен51юшейся длительностью положительных и отрицательных импульсов.

На вход сумматора 12, кроме того, подается сигнал цифроаналогового преобразователя Ю, прошедший через стробирующее устройство 11. Стробирующее устройство 11 осуществляет стробировакие проходящего сигнала на время, равное рассогласованию опорных сигналов, которые подаются на его управляющие входы с выходов первого и второго делятепей частоты б и 7. Щ)н этом в сигнале иа выходе сумматора 12 амплитуда положительных импульсов в общем случае не равна амплитуде отрииателы ых импуль:сов, гак как сигнал цифроаналогового преобразователя 1О приводит к увапиче- 25 с нию амплитуды одних импул-ьсов и к равнозначному уменьшению амЕШИГуды других. ГЪспе фильтрации сук1марного сигнала на фильтре 2 угфавлшошеё напряжение, пропорциональное интегралу от постоянной составляющей суммарного сигнала, поступает на управление перестраиваемым генератором 1. В пороговом разлнчителе 13 производится сравнение временных интервалов между опорными сигналами с пороговым, и, когда эти интервалы становятся меньше порогового, осуществляется временной сдвиг onopHbixi сигналов. Сдвиг осущест- ваяется при поступлении сигналов с первого триггера 14 на управляющие входы первого и второго делителей частоты 6 (7) и первого н второго устройств для поразрядного совпадения 16 (17), вььходы и первые разрядные входы которых соединены соответственно со (вспомогательными входами и разрядными выходами соответствующих первого и второго делитеяей частоты 6 (7). .При этом производится разовое уменьшение коэффици- ента деления первого делителя частоты 6 , А на K,j н увеличение коэффициента /деления второго делителя частоты 7 Н на Kg. При этом выходной импульс первого делителя частоты 6 сдвигается влево на К. TO , а второго делителя 7 чаотогы вправо на Kg Т, где TQ- период

колебаний этапонного генератора. Сдвину тые выходные импульсы первого 6 и второго 7 делителей частоты возвращают соответствующие первый 14 я егорой 15 триггеры в исходные состояния. ,

Предложенный синтезатор частот по . с мвнению с известным позволяет получигь малый шаг перестройки частоты. Формула изобретения.

Цифровой синтезатор частот, содержащий перестраиваемый генератор, к управляющему входу которого подключен выход фильтра нижних частот, а выход перестраиваемого генератора через утфавпаелйлй делитель частоты соединен с первыми входами первого и второго импульснофазовых детекторов, к вторым входам которых подключены выходы первого н второго делителей частоты соответственно, входы которых соединены с выходом генератора опорной частоты, при этом поразрядные входы всех делителей частоты соединены с выходами управляющего блока, о г л н ч а ю щ и и с я тем, что. целью получения шага перестройки чаотогы, меньшего чем разность опорных частот на вторых входах импутасно-фазовых детекторов, в него дополнительно введены последовательно соединенные цифроаналоговый преобразователь, стробир аощее устройство я сумматор, а также пороговый различитель, первый н второй триггеры, первое и второе устройства для поразрядного совпадения, выходы которых соединены с установочными входами первого и второго делитеяей частоты соответственно, при этом выход первого триггера цодсоединен к управляющим входам первого делителя частоты и первого устройства для поразрядного совпадения, выход второго триггера соединен с управляющими входами второго делителя частоты и второго устройства для поразрядного совпадения, к выходу управляющего блока подключены также разрядные входы цифроаыалогового преобразователя н первые разрядные входы первого к второго устройств для поразрядного совпадения, вторые разрядные входы которых соединены с разрядными выходами первого и второго делителей частоты соответственно, вькод первого делителя частоты соединен ;также с первыми входами порогового различителя. стробирукетего устройства и первого триггера, выход второго делителя частоты соединен ; с втсфыми входами порогового различи еля и стробирующего устройства и с первым входом второго триггера, выхоп порогового различи геля с еаинен с вторыми входами первого и второго триггеров а выходы нмпупьсио-фааовых детекторов подсоединены к соответствующим входам сумматора, выход

которого соепинен с входом фильтра нижних частот.

Источники И114 ормации, принятые во внимание при экспертизе

1. Патент США № 3588732, кл. 331-2, 28.06.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1975 |

|

SU531246A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Синтезатор частот | 1980 |

|

SU886251A1 |

| Цифровой синтезатор частот | 1981 |

|

SU1058076A1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1981 |

|

SU1840149A1 |

| Синтезатор частот | 1973 |

|

SU479215A1 |

| Синтезатор частот | 1975 |

|

SU621063A1 |

| Устройство для фазовой автоподстройки частоты | 1974 |

|

SU511668A1 |

| Синтезатор частот | 1973 |

|

SU448394A1 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

Авторы

Даты

1979-01-15—Публикация

1974-10-16—Подача