I

Изобретение относится к радиотехнике и может быть ислользовано в приемопередающей аппаратуре систем связи, в генераторном оборудовании.

Известен синтезатор частот, содержав(ий последовательно соединенные опорный генератор, первый формирователь импульсов, фазовый детектор, выполненный на основе 3 К-триггера, фильтр нижних частот, управляемый генератор, второй формирователь импульсов, элемент совпадения, первый управляющий триггер, второй управляющий триггер, триггер памяти, а также делитель частоты с переменным коэффициентом деления, выход которого соединен с другим входом фазового детектора и с бдним из управляющих входов различителя знака частотной ошибки, другой управляющий вход которого соединен с выходом первого формиройателя импульсов l. .

Однако известный синтезатор частот имеет низкую устойчивость работы.

Цель изобретения - повышение устойчивости работы путем расширения полосы захвата.

Для достижения указанной цели в синтезаторе частот, содержащем последовательно соединенньге опоршш генератор, первый формирователь импульсов, фазопый детектор, выполненньй на основе К-триГгера, фильтр нижних частот, управляемый генератор,

10 второй формирователь импульсов, элемент совпадения, первый управляющий триггер, второй управляющий триггер, триггер памяти, а также делитель частоты с переменным коэффициентом деле15ния, выход которого соединен с другим входом фазового детектора и с од1щм из управляклвдх входов различителя знека частотной опп1бки, другой управлякядий вход которого соединен с вы20ходом первого формирователя импуль- сов, шлход первого формирователя импульсов .соединен-,с установочным входом триггера памяти, выход которого соединен с установочными входами фазового детектора и различителя знака частотной ошибки, первый выход фазового детектора подключен к одном иэ управляющих входов триггера памяти, второй выход фазового детектора соединен о другими управлянлциш входами триггера памяти и различител зиака частотной ошибки, первый выхбд которого подключен к цепи сброса первого и второго управляющих .триггеров. Другой выход различителя 1знака частотной ошибки соединен с входом элемента совпадения, выход которого подключен ко входу делителя частоты с переменным коэффициентом деления, выход которого подсоединен к счетно ту входу триггера памяти и к управляющему входу первого управляющего триггера, счетный вхбд которого соединен с 1ходом второго формирователя импульсов, выход первого управляющего триггера соединен со входом второго управляющего триггера, прямой и инвбрснь«й выходы которого coejD HewH соответственно с третьим управляющим входом различителя знака частотной ошибки и с установочным входом делителя частоты с переменным коэффициентом деления,. -

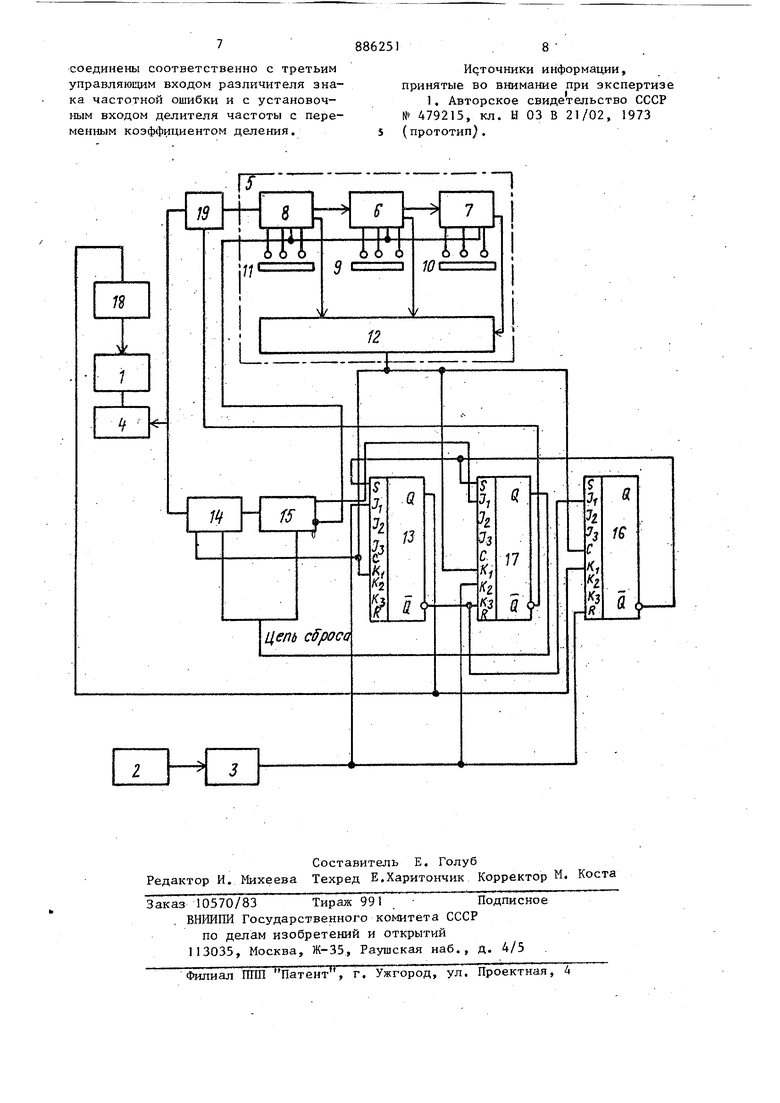

На чергёже представлена структурная электрическая схема предлагаемого синтезатора.

Синтезатор частот содержит управляемый генератор 1, опорнЕлй генератор 2, первый и второй формирователи 3 и 4 импульсов соответственно делитель 5 частоты с переМеншлм коэффициентом деления, который состоит из трех счетчиков 6,7 и 8 ямЛупЬ сов, трех переключателей 9,10 и М коэффициента деления частоты и cxefft 12 совпадения, фазовый детектор 13, первый и второй управлякнцие триггеры 14 и 15 соответственно, триггер 16 памяти, различитель 17 знака частотной ошибки, фильтр 18 нижних частот и элемент 19 совпадения.

Синтезатор частот работает следующим образом.

Пусть частота управляемого генератора 1, поделенная делителем 5 частоты с переменным коэффициентом

меньше частоты опорного

деления,

генератора 2. При этом начальная расстройка больше полосы захвата, но меньше полосы удержания.

В этом случае импульс с частотой опорного генератора 2, предшествующий импульсу с выхода схемы 12 совпадения (на выходе делителя 5 частоты с переменным коэффициентом деления частота следования импульсов , где

N- козф4н{ЦИент деления) , устанавливает на выходе d фазового детектора 13 логическуте 1, На выходе cxebfti 12 совпадения в случае др также устанавливается логическая 1. Этот сигнал не воздействует на различитель 17 знака частотной ошибки, выполненный на 3-К-триггере. Зато импуАьсы с опорной частотой с выхода первого формирователя 3 импульсов опрокидывают J-JK-триггер различителя знака частотной ошибки Сигнал с выхода схемы 12 совпадения поступает также на счетный вход триггера 16 памяти, на установочный (R вход) вход которого Поступает опорная ;последоватёльйость импульсов с выхода первого формирователя 3 импульсов и перебрасывает триггер памяти. в положение Г на 5 выходе.

Одновременно с выхода второго управлякщего триггера 15 импульсы поступшот на управлякнций вход различителя 17 знака частотной ошибки и по)цтве1 кда)от его первоначальное положение

Управляющее напряжение на выходе фильтре IS нижшх частот возрастает, сяёДОЭвтельноj частота управляемого гвнере Тора: 1 быстро увеличивается. Вследствие действия первого 14 и второго 13 управляющих триггеров импульсал ё вьпсода второго управляющего триггера воздействуют на различитель 17 знака частотной ошибки и счетчики 6,7 и 8 импульсов, делитель 5 частоты с переменным коэффициентом деления принудительно сбрасывается . с частотой f.. При этом конечное состоя1ше делителя 5 частоты пропорциональное частоте f , а фазовый детектор 13 находится в таком положении ,. что управляющее напряжение максимально по величине.

При равенстве частот импульсы с выхода делителя 5 частоты .с переменным коэффициентом деления поступают на вход К фазового детектора 13, Если на выходе Q была логическая I, то фазовый детектор перебрасьшается в положение О, на 5 вход 3 поступают импульсы от опорно генератора 2 и перекидывают фазовый детектор 13 в положение 1, На вход К различителя 17 знака частотной ошибки также поступают им пульсы с выхода делителя 5 частоты с переменным коэффициентом деления, на вход Kft поступают импульсы с опор ной частотой, на вход Xj - импульсы с шлхода фазового детектора 13, В случае оГ на выходе фазо вого детектора 13 присутствуют импульсы со скважностью, изменяющейся в зависимости от коэффициента деле1ШЯ Н . На выходе Я триггера 16 памяти в этом режиме l sigj-) появляет ся логическая 1, этот потенциал Прикладывается к S входу раэличйтеля 17 знака частотной ошибки, к § входу фазового детектора 13, к S входу первого управляющего триггера и разрешает обычный режим работы первого и второго уп авляющих триггеров, Когда частота сигнала на выходе делителя 5-частоты с переменным коэф Циентом деления становится болыпе частоты сигнала на выходе первого формирователя 3 импульсов, после второго импульса, поступавщего с имхода схемы совпадения 12, на выходе триггера 16 памяти появляется логический О, Этот низкий потенциал, прикладываясь к различителю 17, перекидывает его в состояние О, на выходе § , т,е, в этом случае счетчики 6,7 и 8 импульсов не работают в режиме счета. При этом конечное состояние делителя 5 частоты с переменным коэффициентом деления соответствует полной емкости. Фазовый детектрр 13 в этом случае находится в положении, обрат ном его положению в режиме ., а управляющее напряжение ьшнимальнО по величине, Таким образом, благодаря использованию в качестве фазового детекто ра, различителя знака частотной оши ки, триггера памяти, 3-К-триггеров расширение полосы захвата происходи без уменьшения вероятности захвата и без усложнения устройства. Кроме того, в предлагаемом синтезаторе частот нет необходимости предварительно устанавливать в определенное положение управляющие триггеры, что упрощает функцию управления и пойышает надежность вхождения в синхронизм при переходе с одной частоты на другую. При этом улучшаются технико-экономические показатели каНалообразующей аппаратуры систем спутниковой связи. Формула изобретения Синтезатор частот, содержащий последовательно соединенные опорный генератор, первый формирователь импульсов, фазовый детектор. Выполненный на основе 3-К-триггера, фильтр Нижних частот, управляемый генератор, второй формирователь импульсов, элемент , первый управляющий триггер, второй управляющий триггер триггер памяти, а также делитель частоты с переменным коэф щиейтом деления, выход которого соединен с Другим входом фазового Детектора и с одним из управляющих входов различителя знака частотной ощибкй, другой управляюпщй вход которого соединен с выходом первого формироватепя импульсов, о тлйч ающи йс я тем, что, с целью повьпаения устойчивости работы путем расширения полосы захвата, выход первого формирователя импульсов соединен с установочным входом TjiKri epa памяти, выход которого соединен с установочшми входами фазового де ектора и различителя знака чaetoтнoй ошибки, первый вых:од фазового детектора подключен к одному иа уйрааляющих входов триггера па1р4ятй, второй выход фазового детектора с другими управляи) входами триггера памяти Н различителя знака частотной ошибки, первый шлход которого подклзочен к цепи сброса первого и второго управлякяцих триггеров, другой выход различителя знака частотной ошибки соединен с другим входом элемента совпадения, выход которого подключен ко входу делителя частоты с переменшлм коэффициентом деления, выход которого подсоединен к счетному входу триггера памяти и к управляющему входу первого управляющего триггера, счетный вход которого соединен с выходом второго.формирователя импульсов, выход перрого управлякмцего триггера соединен со входом второго управляющего триггера, прямой и инверсный выходь которого

соединены соответственно с третьим управляющим входом различителя знака частотной ошибки и с установочным входом делителя частоты с переменным )ициентом деления.

886251. 8

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 479215, кл. Н 03 В 21/02, 1973 5 {прототип,

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1973 |

|

SU479215A1 |

| Синтезатор чатоты | 1974 |

|

SU555534A1 |

| Синтезатор частот | 1981 |

|

SU987818A1 |

| Синтезатор частот | 1986 |

|

SU1478328A1 |

| Цифровой синтезатор частот | 1981 |

|

SU1109913A1 |

| Цифровой синтезатор частоты | 1982 |

|

SU1109914A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Цифровой частотный демодулятор | 1984 |

|

SU1298845A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Цифровой синтезатор частоты | 1977 |

|

SU720667A1 |

Авторы

Даты

1981-11-30—Публикация

1980-02-05—Подача