(54) СИНТЕЗАТОР ЧАСТОТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1977 |

|

SU657578A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1988 |

|

SU1700751A1 |

| Цифровой синтезатор частот | 1974 |

|

SU642842A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Цифровой синтезатор частот | 1977 |

|

SU680142A1 |

| Синтезатор частот | 1973 |

|

SU479215A1 |

| Устройство для фазовой автоподстройки частоты | 1974 |

|

SU511668A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| СИНТЕЗАТОР ЧАСТОТ С ЧАСТОТНОЙ ИЛИ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2004 |

|

RU2280945C1 |

I

Изобретение относится к технике цифрового синтеза частот и может использоваться в аппаратуре радиосвязи в радиолокационных станциях, измерительной технике и устройствах телемеханики.

Известен синтезатор частот, содержащий последовательно соединенные опорный генератор, первый фазовый детектор, первый фильтр нижних частот, первый синхронизируемый генератор и первый делитель частоты с переменным коэффициентом деления, последовательно соединенные второй фазовый детектор, второй фильтр нижних частот и второй синхронизируемый генератор, а также второй делитель частоты с переменным коэффициентом деления, выход которого подключен к другому входу первого фазового детектора, и устройство сопряжения, первый и второй выходы которого соединены с установочными входами соответственно первого и второго делителей частоты с переменным коэффициентом деления 1 .

В известном синхронизаторе частот в спектре синхронизируемой частоты появляются помехи, равные субгармоникам опорной частоты.

Цель изобретения - повышение спектральной чистоты выходного сигнала при одновременном повышении быстродействия.

Для этого в синтезатор частот, содержащий последовательно соединенные опорный генератор, первый фазовый детектор, первый фильтр нижних частот, первый синхронизируемый генератор и первый делитель частоты с переменным коэффициентом деления, последовательно соединенные второй фазовый детектор, второй фильтр нижних частот и вторюй синхронизируемый генератор, а также второй делитель частоты с переменным коэффициентом деления, выход которого подключен к другому входу первого фазового детектора, и устройство сопряжения, первый и второй выходы которого соединены с установочными входами соответственно первого и второго делителей частоты с переменным коэффициентом деления, между выходом первого делителя частоты с переменньм коэффициентом деления и первым входом второго фазового детектора введены последовате.гьно соединенные первый деишфратор, первый триггер, первый элемент совпадения и первый делитель частоты

С постоянным коэффициентом деления, а между выходом первого делителя частоты с переменным коэффициентом деления и входом второго делителя частоты с переменным коэффициентом деления введены последовательно соединенные второй дешифратор, второй триггер и второй элемент совпадения, а выход второго синхронизируемого генератора соединен с другим входом второго элемента совпадения и череэ второй делитель частоты с постоянным коэффициенте деления - с другим входом второго фазового детектора, при этом выход первого синхронизируемого генератора подключен также к другому входу первого элемента совпадения.

Устройство сопряжения может быть выполнено S виде последовательно соединенных первого регистра, первого сумматора и второго сумматора, к другому входу которого подключен выход второго регистра.

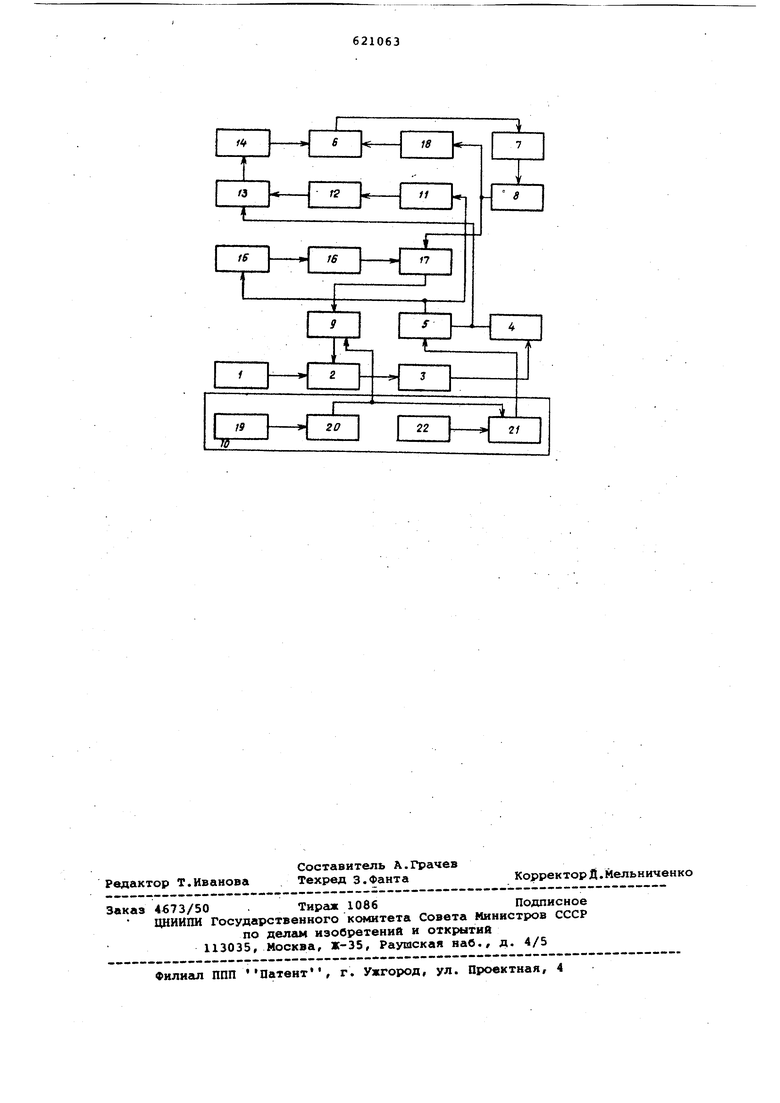

На чертеже изображена структурная электрическая схема синтезатора частот.

Синтезатор частот содержит последовательно соединенные опорный генератор 1, первый фазовый детектор 2, первый фильтр нижних частот 3, первый синхронизируемый генератор 4 и первый делитель частоты,5 с переменным коэффициентом деления; последовательно соединенные второй фазовый детектор 6, второй фильтр нижних частот 7 и второй синхронизируемый генератор 8, а также второй делитель частоты 9 с переменным коэффициентом деления, выход которого подключен к другому входу первого фазового детектора 2, и устройство сопряжения 10, первый и второй выходы которого соединены с установочными входами первого 5 и второго 9 делителей частоты с переменным коэффициентом деления; между выходом первого делителя частоты 5 с переменныр коэффициентом деления и первым входом второго фазового детектора 6 введены последовательно соединенные первый дешифратор 11, первый триггер 12, первый элемент совпадения 13 и первый делитель частоты 14 с постоянным коэффициентом деления; между выходом первого делителя частоты 5 с переманным коэффициентом деления и входом второго делителя частоты 9 с переменным коэффициентом деления введены последовательно соединенные второй дешифратор 15, второй тригге 16 и второй., элемент совпадения 17; выход второго синхронизируемого генератора 8 соединен с другим входом второго элемента совпадения 17 и через второй делитель частоты 18 с постоянным коэффициентом деления с другимвходом второго фазового детектора 6; при этом выход первого

синхронизируемого генератора 4 подключен также к Другому входу первого элемента совпадения 13. Устройство сопряжения выполнено в виде последовательно соединенных первого регистра 19, первого сумматора 20 и второго сумматора 21, к другому входу которого подключен выход второго регистра 22.

Устройство работает следуюа{им образом.

. На первый делитель частоты 5 со второго сумматора 21 заносится код числа ( - а на второй делитель частоты 9 с первого сумматора 20 код числа .

При считывании кода числа () первый дешифратор 11 вызывает срабатывание первого триггера 12, который вьадает разрешение первому элементу совпадения 13 на прохождение выходных колебаний первого синхронизируемого генератора 4 на вход первого делителя частоты 14, которые появляются на его выходе с частотой в () раз меньше частоты первого

синхронизируемого генератора 4 и, являясь опорными для синхронизации временного интервала подстройки второго синхронизируемого генератора 8, поступают на вход второго фазового

детектора 6, На другой вход которого поступает временной интервал подстройки частоты второго синхронизируемого генератора 8, сформированный прохождением выходных колебаний

второго синхронизируемого генератора 8 через второй делитель частоты 18. Сигнал ошибки с выхода второго фазового детектора 6 через второй фильтр нижних частот 7 поступает на управляемый вход второго синхронизируемого генератора 8, обеспечивая получение частоты второго синхронизируемого генератора 8, равной TCT и находящейся с синхронизируемой частотой в нониусном соотношении таким образом, что разность фаз между последним периодом первого синхронизируемого 4 и текущим периодом второго синхронизируемого б генераторов равно нулю, что

обеспечивается использованием второго фазового детектора 6 с нулевым фазовым сдвигом Б режиме слежения. После считывания последнего периода первого синхронизируемого генератора 4 в 1-ом интервале подстройки второй дешифратор 15 вызывает срабатывание второго триггера 16, выдавая разрешение на второй элемент совпадения 17 для прохождения выходных колебаний второго

синхронизируемого генератора В, которые поступают на вход второго делителя частоты 9, обеспечивая таким образом насчитываниа долей периода первого синхронизируемого генератора 4. 5 По окончании считывания числа (т занесенного во второй делитель частоты 9, он выдает импульс на вход перлого фазового деГектора 2, который является окончанием i-го интер вала подстройки первого синхронизируемого генератора 4, осуществляет занесение кода чисел ( и iH соответственно на: первый 5 и второй 9 делители частоты с перемен ным коэффициентом деления, возвраща первый 12 и второй 16 триггеры в ис ходное состояние. На другой вход первого фазового детектора 2 поступает сигнал с опор ного генератора 1, а сигнал ошибки с выхода первого фазового детектора 2через первый фильтр нижних частот 3подается на упраъпяемь& вход первого синхронизируемого генератора 4 осуществляя автоподстройку частоты .последнего. На первом сумматоре 20 вычисляет ся значение числа т прибавлением числа Wp , поступающего с первого регистра 19, а на втором сумматоре 21 производится вычисление числа причем числа и N вычисляются по следукмцему алгоритму:если .. то .--. если (, то , «j,, , а если (,-V; то ., а само число N поступает со второго регистра 22. Предложенный синтезатор частот позволяет создавать простые по конс рукции быстродействующие синтезатор частот с малым шагом перестройки и высокой спектральн9й чистотой колебаний на интегральных схемах средне го и низкого быстродействия, что зн чительно снижает их стоимость и пот ребление знергии. Формула изобрет.ения Синтезатор частот, содержешщй последовательно соединенные опорный 3 генератор, первый фазовый детектор, первЕ фильтр нижних частот, первый синхронизируемый генератор и первый делитель частоты с переменным коэффициентом деления, последовательно соединенные второй фазовый детектор, второй фильтр нижних частот и второй синхрогизируемый генератор, а также второй делитель частоты с переменным коэффициентом деления, выход которого подключен к другому входу первого фазового детектора, и устройство сопряжения, первый и второй выходы которого соединены с установочными входами соответственно первого и второго делителей частоты с переменньм коэффициентом, деления, отличающийся тем, что, с целью повышения спектральной чистоты выходного сигнала при одновременном повьлиении быстродействия, между выходом первого делителя частоты с переменн1Д4 коэффициентом деления и первьвл входом второго фазового детектора введены последовательно соединенные первый дешифратор, первый триггер, первый элемент совпадения и первый делитель час оты с постоянным коэффициентом деления, а между выходом первого делителя частоты с переменным коэффициентом деления и входом второго делителя частоты с переменным коэффициентом деления введены последовательно соединенные второй дешифратор, второй триггер и второй элемент совпадения, а выход второго синхронизируемого генератора соединен с другим входом второго элемента совпадения и через второй делитель частоты с постоянным коэффициентом деления - с другим входом второго фазового детектора, при этом выход первого синхронизируемого генератора подключен также к другому входу первого элемента совпадения. 2; Синтезатор по п. 1, отлич а ю щ и и с я тем, что устройство сопряжения выполнено в виде последовательно соединенных первого регистра, первого сумматора и второго сумматора, к другому входу которого подключен второго регистра. Источники информации, принятые во внимание при экспертизе: 1. Авторское свидетельство СССР 389608, кл. Н 03 В 25/00, 02.03.71.

Авторы

Даты

1978-08-25—Публикация

1975-05-11—Подача